#### Digital System Design Fourth Class EE 404

Diyala University CollegeTheoretical:2Hrs/Wkof Engineering DepartmentTutorial: 1Hrs/Wkof ElectronicsPractical:Hrs/Wk

| Simplification of Boolean Function using K-map and Tabulation                                                        | 6 Hrs             |

|----------------------------------------------------------------------------------------------------------------------|-------------------|

| Digital Circuit Design using Logic Circuits (LSI, SSI, MSI)                                                          | 6 Hrs             |

| Design using Programmable Logic Circuits (ROM, PLA, PAL)                                                             | 6 Hrs             |

| Synchronized Sequential Circuits (Analysis and Design)                                                               | 6 Hrs             |

| ASM Diagrams.                                                                                                        | 6 Hrs             |

| Analysis and Design of Sequential Circuits using ASM Diagrams                                                        | 6 Hrs             |

| Asynchronous Circuit s (Analysis)                                                                                    | 6 Hrs             |

| Luminescent pulse phenomenon in logic circuits (Static and Dynamic)                                                  | 6 Hrs             |

| Microprocessors-Component and Architecture                                                                           | 6 Hrs             |

| Microprocessors Hardware ~<br>4-, 8-, 16- and 32-bit Microprocessors, Single Chip Microcomputer 8085<br>MPU details. | 10 Hrs<br>, 8088, |

# <mark>Rom</mark> and Programmable Logic Devices (<mark>PLDs</mark>)

*Digital ICs* are often *categorized* according to the complexity of their circuits, as measured by the number of logic gates in a single package. The differentiation between those chips which have a few internal gates and those having hundreds of thousand of gates is made by customary reference to package as:

*Small-scale integration* (SSI) devices contain several independent gates in a single package. The inputs and outputs of the gates are connected directly to the pins in the package. The number of gates is usually fewer than 10 and is limited by the number of pins available in the IC.

*Medium-scale integration* (MSI) devices have a complexity of approximately 10 to 1000 gates in a single package. They usually perform specific elementary digital operations.

*Large-scale integration* (LSI) devices contain thousands of gates in a single package. They include digital systems such as processor, memory chips, and programmable logic devices.

*Very Large-scale integration* (VLSI) device contained hundred of thousand of gates within a single package. Examples are large memory array and complex microcomputer chips.

# Read Only Memory (ROM):

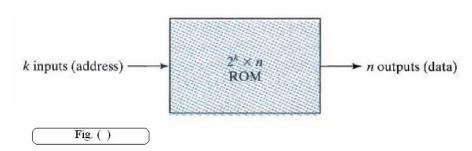

A ROM is essentially a memory device in which permanent binary information is stored. The binary information must be specified by the designer and is then embedded in the unit to form the required interconnection pattern. Once the pattern is established, it stays within the unit even when power is turned off and on again. A block diagram of a ROM consisting of k inputs and n outputs is shown in Figure (1).

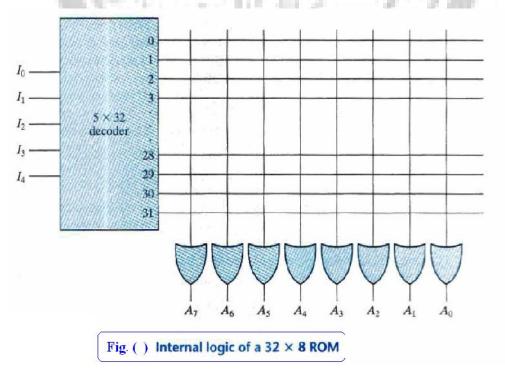

The inputs provide the address for memory, and the outputs give the data bits of the stored word that is selected by the address. The number of words in a ROM is determined from the fact that k address input lines are needed to specify  $2^k$  words. Note that ROM does not have data inputs, because it does not have a write operation. Integrated circuit ROM chips have one or more enable inputs and sometimes come with three-state outputs to facilitate the construction of large arrays of ROM. Consider, for example, a 32 X 8 ROM, the unit consists of 32 words of 8 bits each, there are five input lines that form the binary numbers from 0 through 31 for the address. Figure (2) shows the internal logic construction of this ROM. The five inputs are decoded into 32 distinct outputs by means of a 5 X 32 decoder. Each output of the decoder represents a memory address.

*EX:* Design a combinational circuit using a ROM. The circuit accepts a threebit number and outputs a binary number equal to the square of the input number?

| Sol: Three inputs specify eight words, | so the | ROM | must | be | of | size | 8 | X 4. | The |

|----------------------------------------|--------|-----|------|----|----|------|---|------|-----|

| ROM implementation is shown as:        |        |     |      |    |    |      |   |      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input          | s             |     |                | Out                              | puts           |                |                       |                       | 2.0              |                       |                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|-----|----------------|----------------------------------|----------------|----------------|-----------------------|-----------------------|------------------|-----------------------|-----------------------|----|

| A <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A <sub>1</sub> | Ao            | B5  | B <sub>4</sub> | B <sub>3</sub>                   | B <sub>2</sub> | B <sub>1</sub> | E                     | 30                    |                  | De                    | cim                   | al |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              | 0             | 0   | 0              | 0                                | 0              | 0              |                       | 0                     |                  |                       | 0                     |    |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              | 1             | 0   | 0              | 0                                | 0              | 0              |                       | 1                     |                  |                       | 1                     |    |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 0             | 0   | 0              | 0                                | 1              | 0              | į.                    | 0                     |                  |                       | 4                     |    |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 1             | 0   | 0              | 1                                | 0              | 0              |                       | 1                     |                  |                       | 9                     |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              | 0             | 0   | 1              | 0                                | 0              | 0              |                       | 0                     |                  |                       | 16                    |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              | 1             | 0   | 1              | 1                                | 0              | 0              |                       | 1                     |                  |                       | 25                    |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 0             | 1   | 0              | 0                                | 1              | 0              | 1                     | 0                     |                  |                       | 36                    |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 1             | 1   | 1              | 0                                | 0              | 0              |                       | 1                     |                  |                       | 49                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | mannanan      | 0 - |                | 3 <sub>0</sub><br>3 <sub>1</sub> |                | 0              | 0                     | 0                     |                  | <i>B</i> <sub>4</sub> |                       | l  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | (D)ASNEEDINGS |     | I              | 3,                               |                | 0              | 0                     | 1                     | 000              | 000                   | 00                    |    |

| $A_0 -$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |               |     |                | B2                               |                |                | 0<br>1<br>1           |                       | 0<br>0<br>0      | 0<br>0                | 0                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 8×4ROM        |     | <i>l</i>       | 33                               |                | 0<br>0         | 0<br>1<br>1           | 1<br>0<br>1<br>0      | 0<br>0<br>0<br>0 | 0<br>0                | 0<br>0<br>1<br>0      |    |

| $A_1 - $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                | 8×4 ROM       |     | <i>l</i>       |                                  |                | 0<br>0         | 0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1      | 0<br>0<br>1<br>0<br>1 |    |

| $A_0 - A_1 - A_2 - A_2 - A_2 - A_3 $ |                | 8 × 4 ROM     |     | I              | 33                               |                | 0<br>0         | 0<br>1<br>1           | 1<br>0<br>1<br>0      | 0<br>0<br>0<br>0 | 0<br>0                | 0<br>0<br>1<br>0      |    |

The type of ROM is determined by the way the switches are set or reset (i.e., programmed).

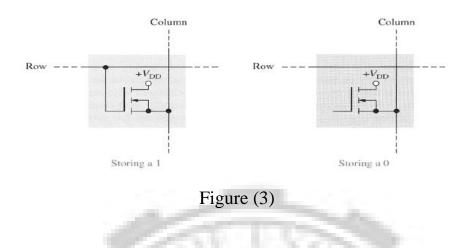

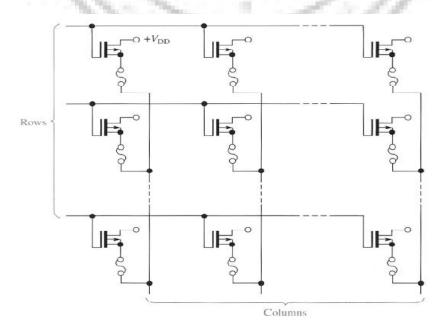

**The Mask ROM:** The mask ROM is usually referred to simply as a ROM. It is permanently programmed during the manufacturing process to provide widely used standard functions, such as popular conversions, or to provide user-specified functions, once the memory is programmed. It cannot be changed. Most IC ROMs utilize the presence or absence of a transistor connection at a row /column junction to represent a 1 or a 0.

Figure (3) shows MOS ROM cells. The presence of a connection from a row line to the gate of a transistor represents a 1 at that location because when the row line is taken HIGH; all transistors with a gate connection to that row line turn on and connect the HIGH (1) to the associated column lines. At row/column junctions

where there are no gate connections, the column lines remain LOW (0) when the row is addressed.

**<u>PROMs</u>**: A PROM uses some type of fusing process to store bits, in which a memory *link* is burned open or left intact to represent a 0 or a 1. The fusing process is irreversible: once a PROM is programmed, it cannot be changed.

Figure (4) illustrates a MOS PROM array with fusible links. The fusible links are manufactured into the PROM between the source of each cell's transistor and its column line. In the programming process, a sufficient current is injected through the fusible link to burn it open to create a stored 0. The link is left intact for a stored 1.

Figure (4)

**EPROMs:** An EPROM is an erasable PROM. Unlike an ordinary PROM, an EPROM can be reprogrammed if an existing program in the memory array is erased first.

An EPROM uses an NMOSFET array with an isolated-gate structure. The isolated transistor gate has no electrical connections and can store an electrical charge for indefinite periods of time. The data bits in this type of array are represented by the presence or absence of a stored gate charge. Erasure of a data bit is a process that removes the gate charge. Two basic types of erasable PROMs are the ultraviolet erasable PROM (UV EPROM) and the electrically erasable PROM (EEPROM).

*UV EPROMs* You can recognize the UV EPROM device by the transparent quartz lid on the package, as shown in Figure (5). The isolated gate in the FET of an ultraviolet EPROM is "floating" within an oxide insulating material. The programming process causes electrons to be removed from the floating gate. Erasure is done by exposure of the memory array chip to high-intensity ultraviolet radiation through the quartz window on top of the package. The positive charge stored on

Figure (5) Ultraviolet erasable PROM package

the gate is neutralized after several minutes to an hour of exposure time.

*EEPROMs* An electrically erasable PROM can be both erased and programmed with electrical pulses. Since it can be both electrically written into and electrically erased, the EEPROM can be rapidly programmed and erased in-circuit for reprogramming.

#### Word-Length Expansion

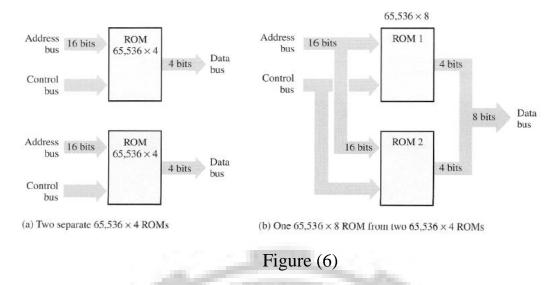

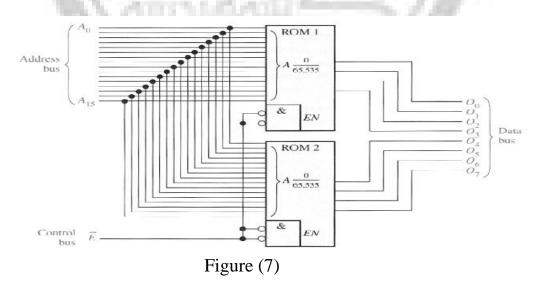

To increase the word length of a memory, the number of bits in the data bus must be increased. For example, an 8-bit word length can be achieved by using two memories, each with 4-bit words as illustrated in Figure (6- a). As you can see in part (b), the 16-bit address bus is commonly connected to both memories so that the combination memory still has the same number of addresses ( $2^{16} = 65,536$ ) as each individual memory. The 4-bit data buses from the two memories are combined to form an 8-bit data bus. Now when an address is selected, eight bits arc produced on the data bus—four from each memory. Example 12-2 shows the details of 65,536 x 4 to 65,536 x 8 expansions.

EXAMPLE: Expand the 65,536 x 4 ROM (64k x 4), to form a 64k x 8 ROM?

*Solution* Two 64k x 4 ROMs are connected as shown in Figure (7). Notice that a spa-ilk address is accessed in ROM 1 and ROM 2 at the same time. The four bits from a selected address in ROM 1 and the four bits from the corresponding address in ROM 2 go out in parallel to form an 8-bit word on the data bus. Also notice that a LOW on the chip enable line, E. which farms a simple control bus, enables both memories.

## Programmable Logic Devices (PLDs)

The three major types of programmable logic are SPLD, CPLD, and FPGA. Each major type generally has several manufacturer-specific subcategories.

<u>SPLDs</u> (simple programmable logic devices) are the least complex form of PLDs. An SPLD can typically replace several fixed-function SSI or MSI devices and their interconnections. The SPLD was the first type of programmable logic available A few categories of SPLD are listed below, some of which are unique to a specific manufacturer. A typical package has 24 to 28 pins.

*PAL* (programmable array logic)

GAL (generic array logic)

*PLA* (programmable logic array)

*PROM* (programmable read-only memory)

<u>CPLDs</u> (complex programmable logic devices) have a much higher capacity than SPLDs, permitting more complex logic circuits to be programmed into them. A typical CPLD is the equivalent of from two to sixty-four SPLDs. The development of these devices followed the SPLD as advances in technology permitted higher-density chips to be implemented. There are several forms of CPLD, which vary in complexity and programming capability. CPLDs typically come in 44-pin to 160-pin packages depending on the complexity.

**FPGAs** (field-programmable gate arrays) are different from SPLDs and CPLDs in their internal organization and have the greatest logic capacity. FPGAs consist of an array of anywhere from sixty-four to thousands of logic-gate groups that are sometimes called logic blocks. Two basic classes of FPGA are course-grained and fine-grained. The course-grained FPGA has large logic blocks, and the fine-grained FPGA has much smaller logic blocks. FPGAs come in packages ranging up to 1000 pins or more.

## Programmable Arrays

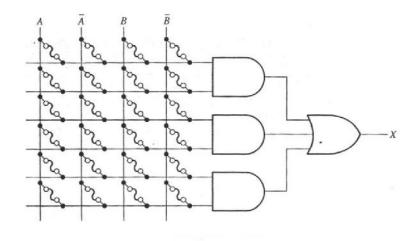

All PLDs consist of programmable arrays. A programmable array is essentially a grid of conductors that form rows and columns with a fusible link at each cross point. Arrays can be either fixed or programmable. The earliest type of programmable array, dating back to the 1960s, was a matrix with a diode at each cross point of the matrix.

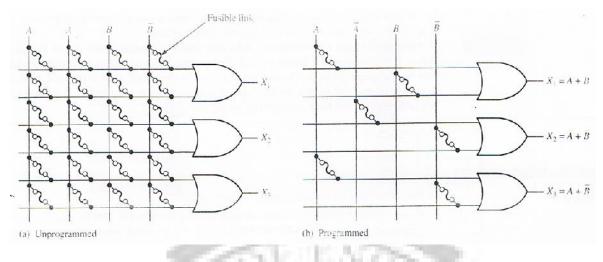

*The OR Array* The original diode array evolved into the integrated OR array, which consists of an array of OR gates connected to a programmable matrix with fusible links at each cross point of a row and column, as shown in Figure (8- a). The array is programmed by blowing fuses to eliminate selected variables from the output functions, as illustrated in part (b) for a specific case. For each input to an

7

OR gate, only one fuse is left intact in order to connect the desired variable to the gate input. Once a fuse is blown, it cannot be reconnected.

Figure (8)

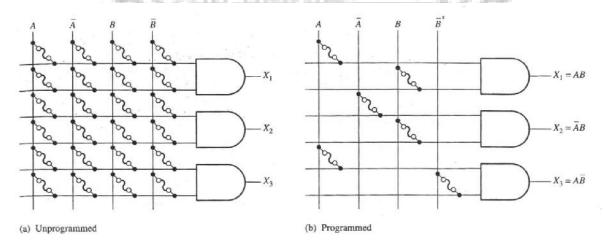

*The AND Array* This type of array consists of AND gates connected to a programmable matrix with fusible-links at each cross point, as shown in Figure (9-a). Like the OR array, the AND array is programmed by blowing fuses to eliminate variables from the output function, as illustrated in part (b). For each input to an AND gate, only one fuse is left intact in order to connect the desired variable to the gate input. Also like the OR array, the AND array with fusible links is one-time programmable.

Figure (9)

### Classifications of PLDs

PLDs are classified according to their *architecture*, which is basically the internal functional arrangement of the elements that give a device its particular operating characteristic.

8

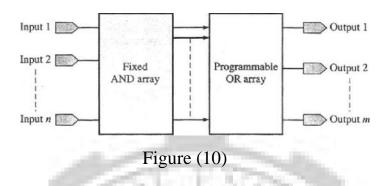

**Programmable Read-Only Memory** The **PROM** consists of a set of fixed (nonprogrammable) AND gates connected as a decoder and a programmable OR array, as shown in the generalized block diagram of Figure (10). The PROM is used primarily as an addressable memory and not as a logic device because of limitations imposed by the fixed AND gates.

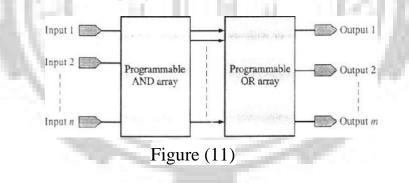

**Programmable Logic Array (PLA)** The **PLA** is a PLD that consists of a programmable AND array and a programmable OR array, as shown in Figure (11). The PLA was developed to overcome some of the limitations of the PROM. The PLA is also called an FPLA (field-programmable logic array) because the user in the field, not the manufacturer, programs it.

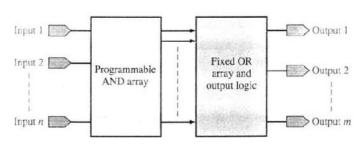

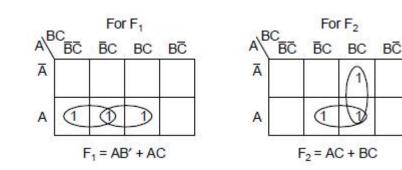

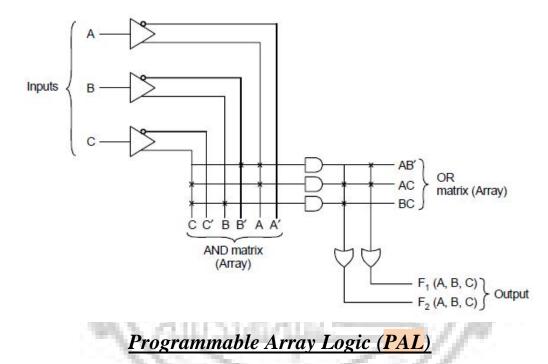

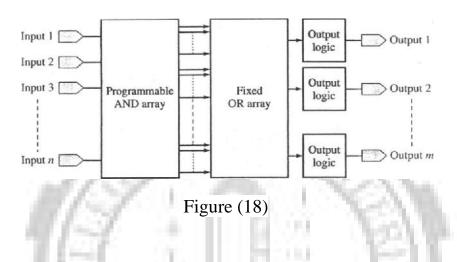

**Programmable Array Logic (PAL)** The **PAL** is a PLD that was developed to overcome certain disadvantages of the PLA, such as longer delays due to the additional fusible links that result from using two programmable arrays and more circuit complexity. The basic PAL consists of a programmable AND array and a fixed OR array with output logic, as shown in Figure (12). The PAL is the most common one-time programmable logic device (OTP) and is implemented with bipolar technology (TTL or ECL).

Figure (12)

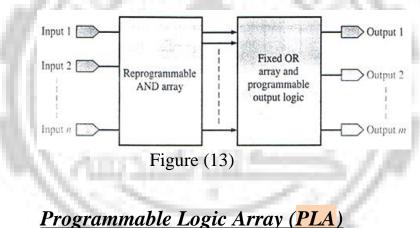

*Generic Array Logic (GAL)* The GAL has a reprogrammable AND array and a fixed OR array with programmable output logic. The two main differences between GAL and PAL devices are (a) the GAL is *reprogrammable* and (b) the GAL has programmable output configurations. The GAL can be reprogrammed again and again because it uses  $E^2CMOS$  (electrically erasable CMOS) technology instead of bipolar technology and fusible links. The block diagram of a GAL is shown in Figure (13).

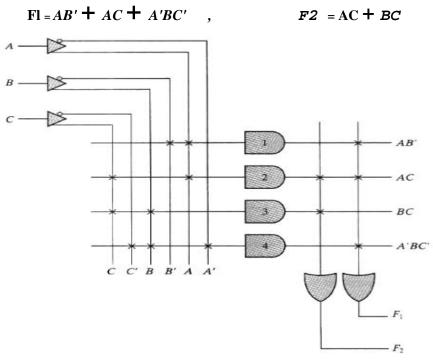

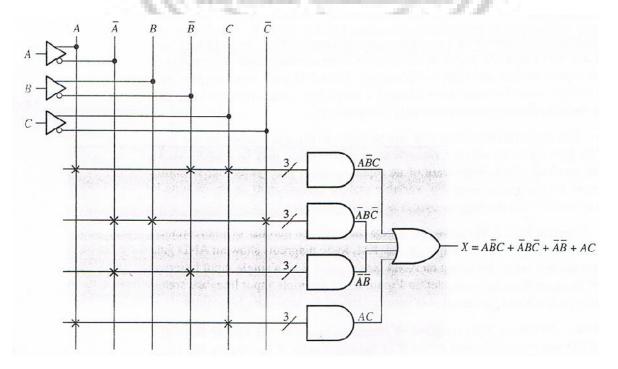

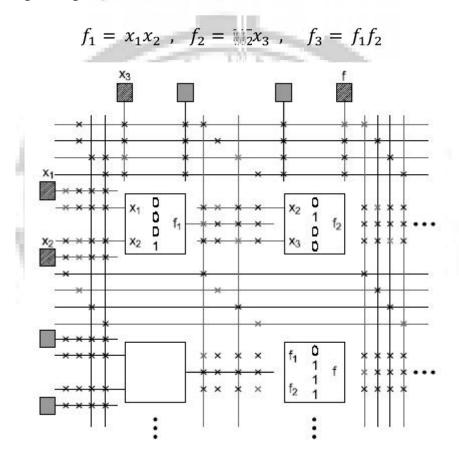

The PLA is similar in concept to the PROM, except that the PLA does not provide full decoding of the variables and does not generate all the minters. The decoder is replaced by an array of AND gates that can be programmed to generate any product term of the input variables. The product terms are then connected to OR gates to provide the sum of products for the required Boolean functions. The internal logic of a PLA with three inputs and two outputs is shown in Figure bellow. Such a circuit is too small to be useful commercially, but is presented here to demonstrate the typical logic configuration of a PLA. The diagram uses the array logic graphic symbols for complex circuits. Each input goes through a buffer-inverter combination, shown in the diagram with a composite graphic symbol, that has both the true and complement

outputs. Each input and its complement is connected to the inputs of each AND gate, as indicated by the intersections between the vertical and horizontal lines. The outputs of the AND gates are connected to the inputs of each OR gate. The particular Boolean functions implemented in the PLA of Fig. bellow are:

PLA with three inputs, four product terms, and two outputs

<u>Ex:</u> Implement the following functions using 3-input, 3 product terms and 20utput PLA.

$$F1 = (4, 5, 7) F2 = (3, 5, 7)$$

Solution: Step 1. Derive the truth table for the combinational circuit.

| Inputs |   |   | Outp  | outs  |

|--------|---|---|-------|-------|

| A      | В | C | $F_2$ | $F_1$ |

| 0      | 0 | 0 | 0     | 0     |

| 0      | 0 | 1 | 0     | 0     |

| 0      | 1 | 0 | 0     | 0     |

| 0      | 1 | 1 | 1     | 0     |

| 1      | 0 | 0 | 0     | 1     |

| 1      | 0 | 1 | 1     | 1     |

| 1      | 1 | 0 | 0     | 0     |

| 1      | 1 | 1 | 1     | 1     |

Step 2. Simplify functions using K-map.

Step 3. Draw the logic diagram

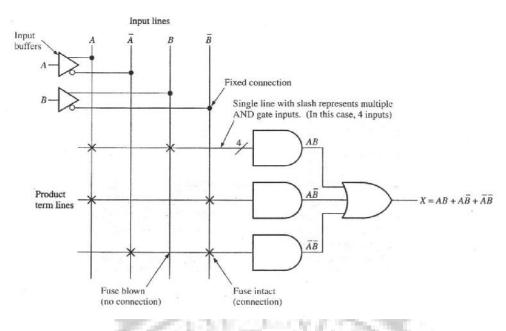

The PAL consists of a programmable array of AND gates that connects to a fixed array of OR gates. This structure allows any sum-of-products (SOP) logic expression with a defined number of variables to be implemented. The basic structure of a PAL is illustrated in Figure (14) for two input variables and one output although most PALs have many inputs and many outputs. As you know, a programmable array is essentially a grid of conductors forming rows and columns with a fusible link at each cross point. Each fused cross point of a row and column is called a cell and is the programmable element of a PAL. Each row is connected to the input of an AND gate and each column is connected to an input variable or its complement. By using the presence or absence of fused connections created by programming, any combination of input variables or complements can be applied to an AND gate to form any desired product term.

Figure (14)

*Implementing a Sum-of-Products Expression* In its simplest form, each cell in a basic AND array consists of a fusible link connecting a row and a column as represented in Figure (14). When the connection between a row and column is required, the fuse is left intact. When no connection between a row and column is required, the fuse is blown open during the programming process.

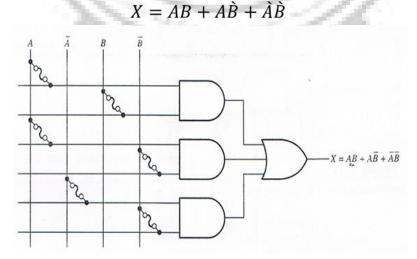

As an example, a simple array is programmed as shown in Figure (15) so that the product term AB is produced by the top AND gate, AB by the middle AND gate, and A B by the bottom AND gate. As you can see, the fusible links are left intact to connect the desired variables or their complements to the appropriate AND gate inputs. The fusible links are opened where a variable or its complement is not used in a given product term. The final output from the OR gate is the SOP expression,

Figure (15)

### Simplified Symbols

What you have seen so far represents a small segment of a typical PAL. Actual PALs have many AND gates and many OR gates in addition to other circuitry and are capable of handling many input variables and their complements. Since PALs are very complex integrated circuit devices, manufacturers have adopted a simplified notation for the logic diagrams to keep them from being overwhelmingly complicated.

*Input Buffers* The input variables to a PAL are buffered to prevent loading by the large number of AND gate inputs to which a variable or its complement may be connected. An inverting buffer produces the complement of an input variable. The symbol representing the **buffer** circuit that produces both the variable and its complement on its outputs is shown in Figure (16) where the bubble output is the complement.

AND Gates A typical PAL AND array has an extremely large number of interconnecting lines, and each AND gate has multiple inputs. PAL logic diagrams show an AND gate that actually has several inputs by using an AND gate symbol with a single input line representing all of its input lines, as indicated Figure (16). Also, multiple input lines are sometimes indicated by a slash and the number of lines as shown in the top AND gate for the case of four lines.

**PAL Connections** To keep a logic diagram as simple as possible, the fusible links in a programmed AND array are indicated by an X at the cross point if the fuse is left intact and by the absence of an X if the fuse is blown, as indicated in Figure (16). Fixed connections use the standard dot notation, as also indicated.

Figure (16)

<u>EX:</u> Show how a PAL is programmed for the following 3-variable logic function:

$$X = A\dot{B}C + \dot{A}B\dot{C} + \dot{A}\dot{B} + AC$$

*Solution* The programmed array is shown in Figure (17). The intact fusible links are indicated by small Xs. The absence of an X means that the fuse has been blown.

#### The PAL Block Diagram

A block diagram of a PAL is shown in Figure (18). The AND array outputs go to the OR array, and the output of each OR gate goes to its associated output logic. A typical PAL has eight or more inputs to its AND array and up to eight outputs from its output logic as indicated, where n = 8 and m = 8. Some PALs provide a combined input and output (I/O) pin that can be programmed as either an output or an input. The symbol  $\square$  means that a pin can be either an input or an output.

#### PAL Output Combinational Logic

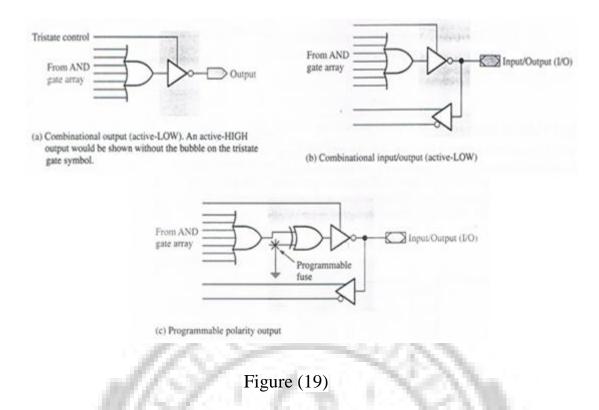

There are several basic types of PAL output logic that allows you to configure the device for a specific application. In this chapter, only the aspects of the output logic related to combinational logic functions are discussed. Figure (19) shows three basic types of combinational output logic with tri-state outputs and the associated OR gate. The following are types of PAL output logic:

*Combinational output:* This output is used for an SOP function and is usually available as either an active-LOW or an active-HIGH output.

*Combinational input/output (I/O):* This output is used when the output function must feed back to be an input to the array or be used to make the I/O pin an input only)

*Programmable polarity output* This output is used for selecting either the output function or its complement by programming the exclusive-OR gate for inversion or no inversion. The fusible link on the exclusive-OR input is blown open for inversion and left intact for no inversion.

#### Standard PAL Numbering

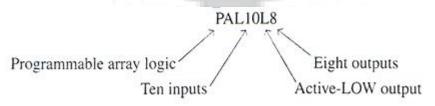

Standard PALs come in a variety of configurations, each of which is identified by a unique part number. This part number always begins with the prefix PAL. The first two digits following PAL indicate the number of inputs, which includes outputs that can be configured as inputs. The letter following the number of inputs designates the type of output: L—active- LOW, H— active-HIGH, or P—programmable polarity. The one or two digits that follow the output type is the number of outputs. The following number is an example.

In addition, a PAL part number may carry suffixes that specify speed, package type, and temperature range. As an example of a PAL configuration, a block diagram of the PAL16L8 and PAL16R4 are shown in Figure (20).

Generic Array Logic (GAL)

The GAL basically consists of a reprogrammable array of AND gates that connects to a fixed array of OR gates. Just as in a PAL, this structure allows any sum-of-products (SOP) logic expression with a defined number of variables to be implemented.

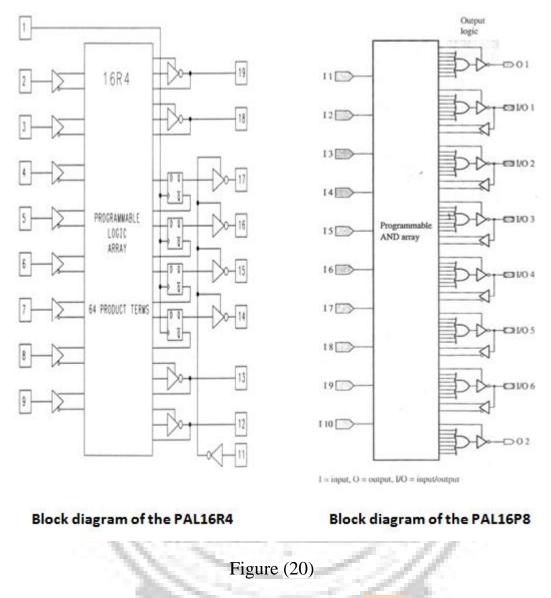

The basic structure of a GAL is illustrated in Figure (21) for two input variables and one output although most GALs have many inputs and many outputs. The reprogrammable array is essentially a grid of conductors forming rows and columns with an electrically erasable CMOS ( $E^2$ CMOS) cell at each cross point, rather than a fuse as in a PAL. These cells are shown as blocks in the figure.

Each row is connected to the input of an AND gate, and each column is connected to an input variable or its complement. By programming each  $E^2$ CMOS

cell to be either *on* or *off*, any combination of input variables or complements can be applied to an AND gate to form any desired product term. A cell that is *on* effectively connects its corresponding row and column, and a cell that is *off* disconnects the row and column. The cells can be electrically erased and reprogrammed. A typical  $E^2CMOS$  cell can retain its programmed state for 20 years or more.

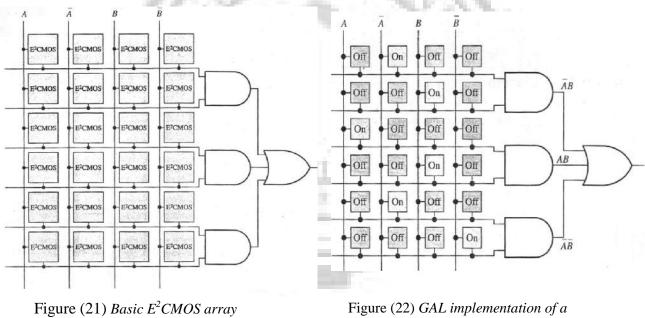

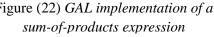

**Implementing a Sum-of-Products Expression** As an example, a simple GAL array is programmed as shown in Figure (22) so that the product term *AB* is produced by the top AND gate, AB by the middle AND gate, and A B by the bottom AND gate. As shown, the E2CMOS cells are on to connect the desired variables or their complements to the appropriate AND gate inputs. The E2CMOS cells are off where a variable or its complement is not used in a given product term. The final output from the OR gate is an SOP expression.

<u>Ex:</u> Show how a GAL is programmed for the following 3-variable logic function:

$$X = \dot{A}B\dot{C} + \dot{A}BC + BC + A\dot{B}$$

*Solution* The programmed array using simplified notation is shown bellow. Cells that are *on* are indicated by small Xs. The absence of an X means that the cell is *off*

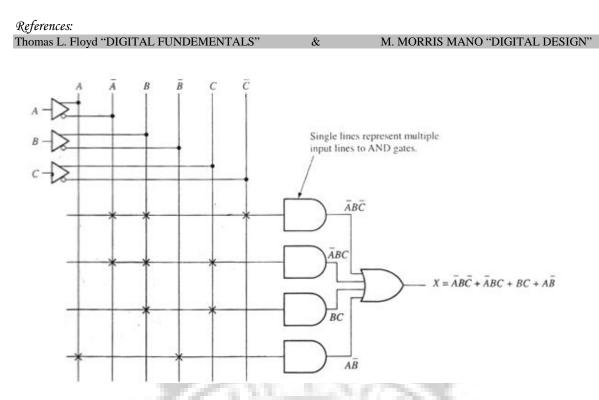

The GAL Block Diagram A block diagram of a GAL is shown in Figure (23). The AND array outputs go to the output logic macrocells (OLMC), which contain the OR gates and programmable logic. A typical GAL has eight or more inputs to its AND array and eight or more input/outputs (I/Os) from its OLMCs as indicated, where n = 8 and m = 8. The OLMC is made up of logic circuits that can be programmed as either *combinational logic* or as *registered logic*. The OLMC provides much more flexibility than the fixed output logic in a PAL.

Figure (23)

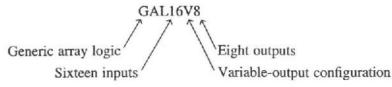

**Standard GAL Numbering** GALs come in a variety of configurations, each of which is identified by a unique part number. This part number always begins with the prefix GAL. The first two digits following the prefix indicate the number of inputs, which includes outputs that can be configured as inputs. The letter V following the number of inputs designates a variable-output configuration. The

one or two digits that follow the output type is the number of outputs. The following

### <u>THE GAL22V10</u>

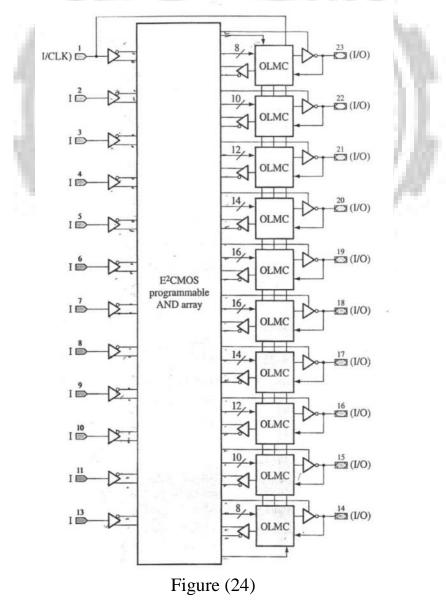

The GAL22V10 contains twelve dedicated inputs and ten input/outputs (I/Os) as shown in the block diagram of Figure 7-18. This device is available in either a 24-pin DIP (dual in-line package) or a 28-pin PLCC (plastic chip carrier), as shown in Figure (24). This device is also available in a low-voltage version, the GAL22LV10.

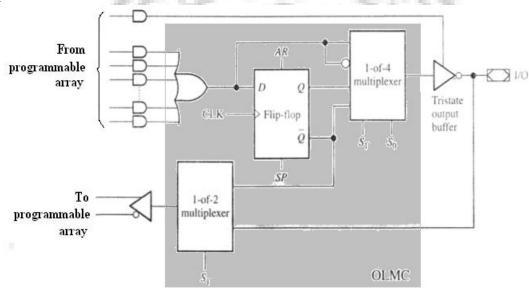

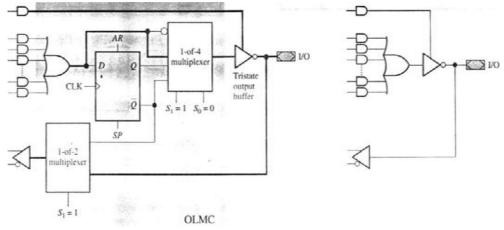

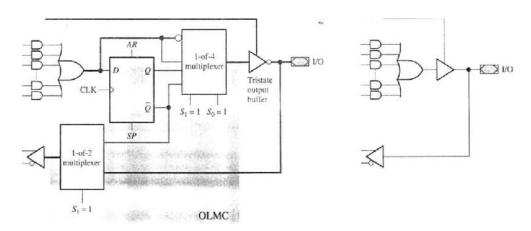

### The Output Logic Macrocells (OLMCs)

As stated in the discussion of GALs, an OLMC contains programmable logic circuits that can be configured either for a combinational output or input or for a registered output. In the registered mode, the output comes from a flip-flop.

As indicated by the notation in the block diagram of Figure (24), of the ten available GAL22V10 OLMCs, two have eight product terms (lines from the AND array to the OR gate), two have ten product terms, two have twelve product terms, two have fourteen product terms, and two have sixteen product terms. Each OLMC can be programmed for either an active-HIGH or an active-LOW output. Also, each OLMC can be programmed as an input.

*Logic Diagram* A basic logic diagram for the GAL22V10 OLMC is shown in Figure (25). The inputs from the AND gates to the OR gate vary from ten to sixteen, as mentioned. The logic inside the gray box consists of a flip-flop and two multiplexers.

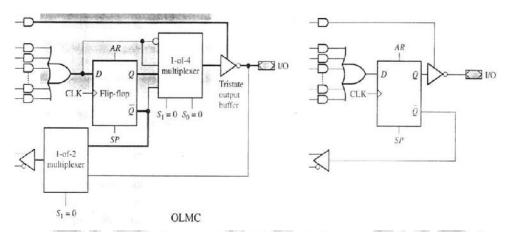

The 1-of-4 multiplexer connects one of its four input lines to the tri-state output buffer, based on the states of two select inputs,  $S_0$  and  $S_1$ . The inputs to the 1-of-4 multiplexer are the OR gate output, the complement of the OR gate output, the flip-flop output Q, and the complement of the flip-flop output  $\overline{Q}$ . This allows the output of the OLMC to be either active-HIGH or active-LOW in each mode. The 1of-2 multiplexer connects either the output of the tri-state buffer or the  $\overline{Q}$  output of the flip-flop back through a buffer to the AND array based on the state of  $S_1$ . The select bits,  $S_0$  and  $S_1$ , for each OLMC are programmed into a dedicated group of cells in the array by the compiler software, so the user does not have to directly manipulate these bits. The OLMC of the type shown in Fig.(25) can be configured to produce four different outputs depending upon the selection inputs. These include the following:

- 1.  $S_1S_0 = 00$ : registered mode with active LOW output, Fig. (26- a).

- 2.  $S_1S_0 = 01$ : registered mode with active HIGH output, Fig. (26- b).

- 3.  $S_1S_0 = 10$ : combinational mode with active LOW output, Fig. (26- c).

- 4.  $S_1S_0 = 11$ : combinational mode with active HIGH output, Fig. (26- d).

(a) OLMC in the active-LOW registered mode and the effective logic diagram

(b) OLMC in the active-HIGH registered mode and the effective logic diagram

(c) OLMC in the active-LOW combinational mode and the effective logic diagram

(d) OLMC in the active-HIGH combinational mode and the effective logic diagram  $Figure\ (26)$

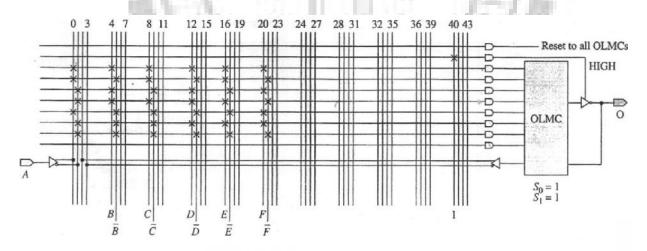

<u>EX:</u> Show how the following 6-variable SOP function is implemented with the GAL22V10.

$X = ABCDEF + A\overline{B}C\overline{D}E\overline{F} + \overline{A}B\overline{C}D\overline{E}F + \overline{A}BCDE\overline{F} + A\overline{B}\overline{C}\overline{D}\overline{E}F + \overline{A}\overline{B}\overline{C}DEF + \overline{A}\overline{B}\overline{C}\overline{D}\overline{E}\overline{F}$

*Solution* The programmed portion of the array with the associated OLMC is shown in Figure bellow. The rest of the array remains unused in this case. The Xs represent  $E^2$ CMOS cells that are programmed to the *on* state.

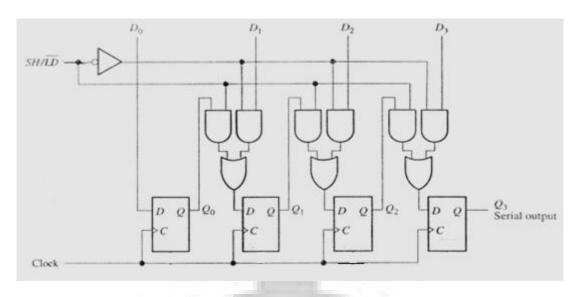

<u>EX:</u> Implement Hand 4-bit parallel in/serial out shift register in Figure below by using (a Hand LA and Flip-flops, (b) - GAL22V10. The SH/1100 input is the Shift/mind. When this input is LOW, the parallel data are loaded into the register, and when it is HIGH, data are shifted from left to right.  $D_0$  through  $D_3$  are the parallel data inputs and  $Q_3$  is the serial data output.

&

# FIELD-PROGRAMMABLE GATE ARRAYS (FPGA)

Field Programmable Gate Array (FPGA) devices were introduced by Xilinx in the mid 1980s. They differ from CPLDs in architecture, storage technology, number of built-in features, and cost, and are aimed at the implementation of high performance, large-size circuits.

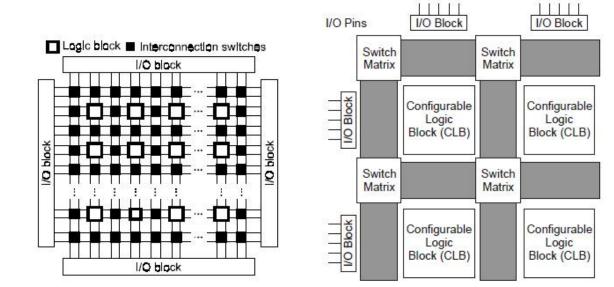

FPGAs are flexible, programmable devices with a broad range of capabilities. Their basic structure consists of an array of universal, programmable logic cells embedded in a configurable connection matrix. There are three key parts of FPGA structure: logic blocks, interconnect, and I/O blocks. The I/O blocks form a ring around the outer edge of the part. Each of these provides individually selectable input, output, or bidirectional access to one of the general-purpose I/O pins on the exterior of the FPGA package.

Inside the ring of I/O blocks lies a rectangular array of logic blocks. And connecting logic blocks to logic blocks and I/O blocks to logic blocks is the programmable interconnect wiring.

In FPGAs, CPLD's PLDs are replaced with a much smaller *logic block*. The logic blocks in an FPGA are generally nothing more than a couple of logic gates or a look-up table (LUT) and a flip-flop. The FPGAs use a more flexible and faster interconnection structure than the CPLDs. In the FPGAs, the logic blocks are embedded in a mesh or wires that have programmable interconnect points that can be used to connect two wires together or a wire to a logic block as shown in Fig. (1).

Figure (1)

Figure (2)

There are several architectures for FPGAs available but the two popular architectures are that, used by Xilinx and Altera. The Xilinx chips utilize an "island-type" architecture, where logic functions are broken up into small islands of 4–6 term arbitrary functions, and connections between these islands are computed. Fig.(2) illustrates the basic structure of the Xilinx FPGA. Altera's architecture ties the chip

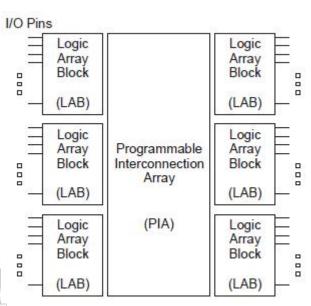

inputs and outputs more closely to the logic blocks, as shown in Fig.(3). This

Figure (3)

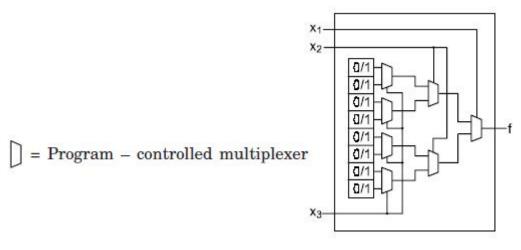

architecture places the logic blocks around one central, highly connected routing array. The circuits used to implement combinational logic in logic blocks are lookup tables (LUT). The structure of LUT's in Altera FPGAs is as shown in Fig. (4).

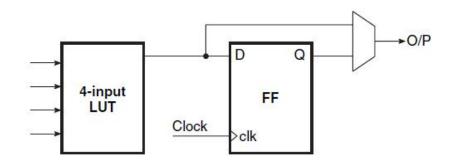

Figure (5) shows a typical logic block of an FPGA. It consists of a four-input look-up table (LUT) whose output feeds a clocked flip-flop. The output can either be a registered output or an unregistered LUT output. Selection of the output takes place in the multiplexer. An LUT is nothing but a small one-bit wide memory array with its address lines representing the inputs to the logic block and a one-bit output acting as the LUT output. An LUT with n inputs can realize any logic function of n inputs by programming the truth table of the desired logic function directly into the memory.

ĸ

Figure (5)

• As example of programmed FPGA, when :

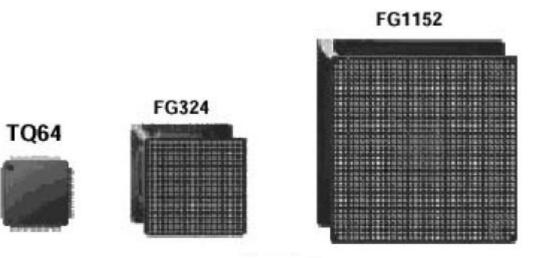

A few examples of FPGA packages are illustrated in Fig.(6), which shows one of the smallest FPGA packages on the left (64 pins), a medium-size package in the middle (324 pins), and a large package (1,152 pins) on the right.

# State Machine Design with SM Charts

# Algorithmic State Machine (ASM)

Finite state machines are a powerful tool for designing sequential circuits, but they are lacking in that they do not explicitly represent the algorithms that compute the transition or output functions, nor is timing information explicitly represented. Flowcharts are useful in the hardware design of digital systems. A special type of flowchart is called a state machine flowchart, or SM chart for short. SM charts are also called ASM (algorithmic state machine) charts. The SM chart offers several advantages:

- It is often easier to understand the operation of a digital system by inspection of the SM chart instead of the equivalent state graph.

- A given SM chart can be converted into several equivalent forms, and each form leads directly to a hardware realization.

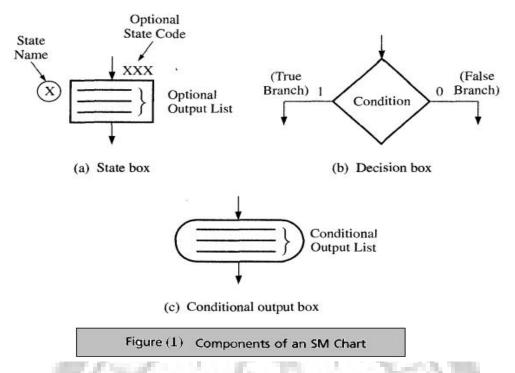

An SM chart differs from an ordinary flowchart in that certain specific rules must be followed in constructing the SM chart. When these rules are followed, the SM chart is equivalent to a state graph, and it leads directly to a hardware realization. Figure (1) shows the three principal components of an SM chart.

The state of the system is represented by a state box. The state box may contain an output list, and a state code may be placed outside the box at the top. The state name is placed in a circle to the left of the state box. A decision box is represented by a diamond-shaped symbol with true and false branches. The condition placed in the box is a Boolean expression that is evaluated to determine which branch to take. The conditional output box, which has curved ends, contains a conditional output list. The conditional outputs depend on both the state of the system and the inputs.

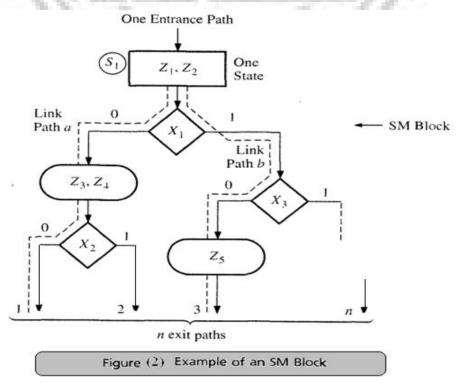

Figure (2), when state  $S_1$  is entered, outputs  $Z_1$  and  $Z_2$  become 1. If inputs  $X_1$  and  $X_2$  are both equal to 0,  $Z_3$  and  $Z_4$  are also 1, and at the end of the state time the machine goes to the next state via exit path 1. On the other hand, if  $X_1 = 1$  and  $X_3 = 0$ , the output  $Z_5$  is 1 and exit to the next state will occur via exit path 3.

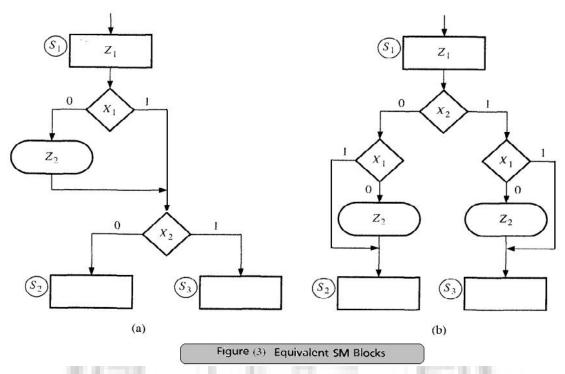

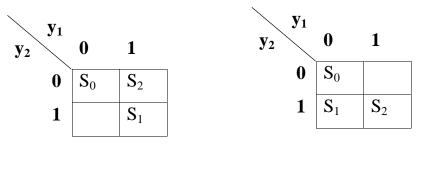

Figure (3) shows two equivalent SM blocks. In both (a) and (b), the output  $Z_2=1$  if  $X_1=0$ ; the next state is  $S_2$  if  $X_2=0$  and  $S_3$  if  $X_2=1$ .

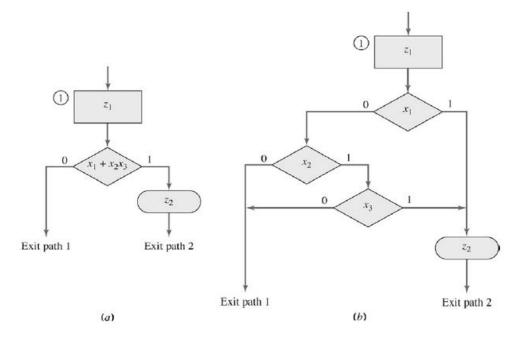

Figure (4) shows two equivalent ASM blocks. (a) Using a single decision box. (b) Using several decision boxes.

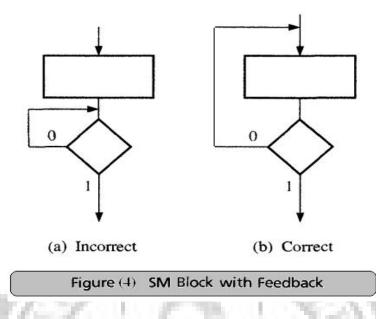

Figure (5) shows an incorrect and correct way of drawing an SM block with feedback.

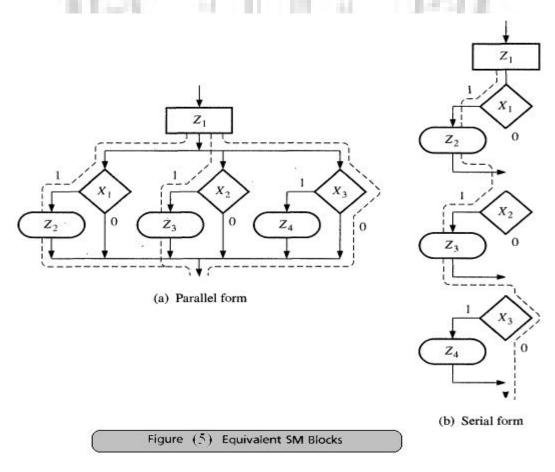

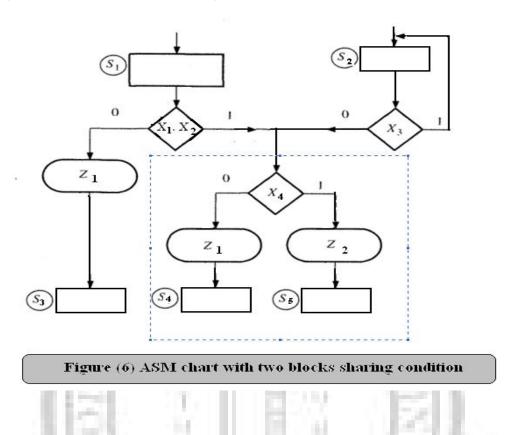

Figure (6-a) shows a parallel SM block, which is equivalent to Fig. (6-b). The link path for  $X_1 = X_2 = 1$  and  $X_3 = 0$  is shown with a dashed line, and the outputs encountered on this path are  $Z_1$ ,  $Z_2$ , and  $Z_3$ .

#### Figure (7) shows ASM sharing:

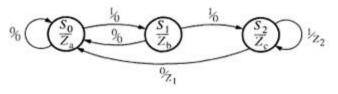

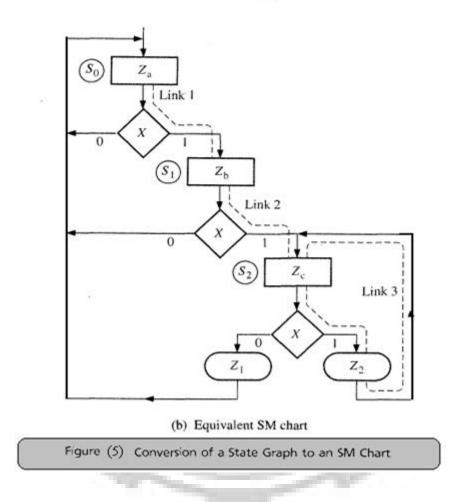

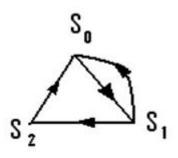

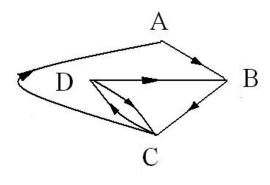

A state graph for a sequential machine is easy to convert to an equivalent SM chart. The state graph of Fig.(7-a) has both "Moore" and "Mealy" outputs. The equivalent SM chart has three blocks- one for each state. The "Moore" outputs ( $Z_a$ ,  $Z_b$ ,  $Z_c$ ) are placed in the state boxes since they do not depend on the input. The "Mealy" outputs ( $Z_1$ ,  $Z_2$ ) appear in conditional output boxes since they depend on both the state and input. In this example, each SM block has only one decision box since only one input variable must be tested. For both the state graph and SM chart,  $Z_c$  is always 1 in state  $S_2$ . If X = 0 in state  $S_2$ ,  $Z_1 = 1$  and the next state is  $S_0$ . If X = 1,  $Z_2 = 1$  and the next state is  $S_2$ .

(a) State graph

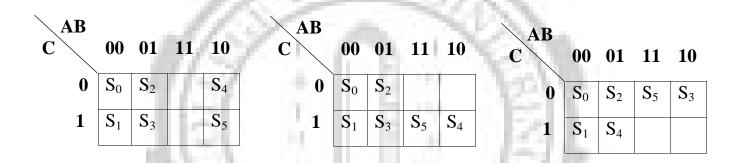

• *State Assignment:* we write the transition without slink as:

Assignment graph

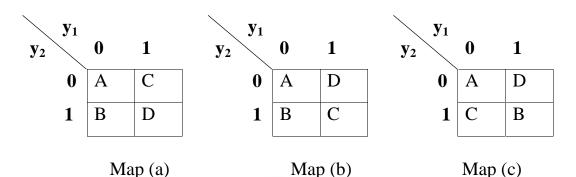

Now we draw K-maps :

| Map | (b) |

|-----|-----|

|-----|-----|

Map (a)

Now, fond a minimum state locus assignment for the ASM chart:

| 16                        | bit distance<br>map(a) | bit distance<br>map(b) |

|---------------------------|------------------------|------------------------|

| $S_0 \longrightarrow S_1$ | 1                      | 2                      |

| $S_1 \longrightarrow S_0$ | 1                      | 2                      |

| $S_1 \longrightarrow S_2$ | 1                      | 1                      |

| $S_2 \longrightarrow S_0$ | 2                      | 1                      |

| State locus               | 5                      | 6                      |

We choose the less map distance, therefore map (a), from map (a)

|                | <i>y</i> 1 <i>y</i> 2 |

|----------------|-----------------------|

| S <sub>0</sub> | 00                    |

| $S_{I}$        | 01                    |

| $S_2$          | 11                    |

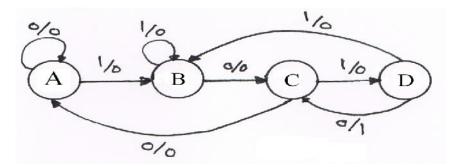

<u>EX:</u> A circuit is required to produce an output (1) when the sequence (1010) is detected and zero output at all other inputs?

(a) State diagram

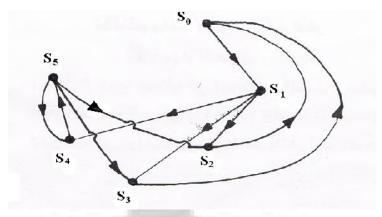

• *State Assignment:* we write the transition without slink as:

Now we draw K-maps:

|                       | bit distance<br>map(a) | bit distance<br>map(b) | bit distance<br>map(c) |  |  |  |

|-----------------------|------------------------|------------------------|------------------------|--|--|--|

| AB                    | 1.                     | 1                      | 2                      |  |  |  |

| $B \longrightarrow C$ | 2                      | 1/1/                   | 1                      |  |  |  |

| D→ B                  | 1                      | 2                      | 1                      |  |  |  |

| C → A                 | 1                      | 2                      | 1                      |  |  |  |

| C → D                 | 1                      | 1                      | 2                      |  |  |  |

| $D \longrightarrow C$ | 1                      | 1                      | 2                      |  |  |  |

| State locus           | 7                      | 8                      | 9                      |  |  |  |

| We choose the less map distance, therefore map (a) | 111 | <i>y</i> 1 <i>y</i> 2 |

|----------------------------------------------------|-----|-----------------------|

| because it should be minimums, from map (a):       | A   | 00                    |

|                                                    | В   | 01                    |

|                                                    | С   | 10                    |

|                                                    | D   | 11                    |

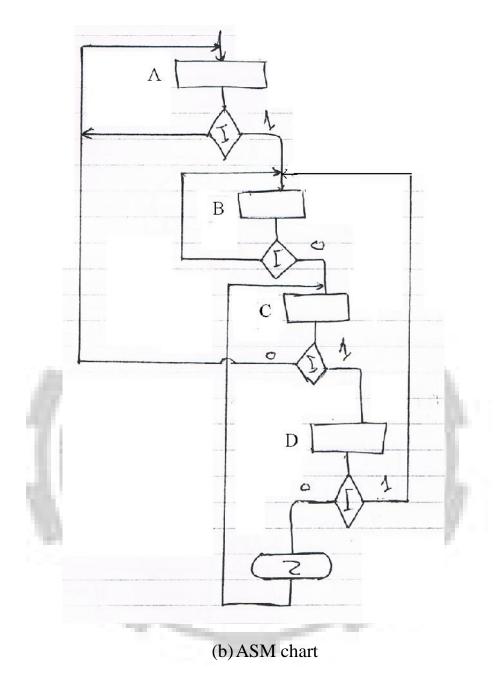

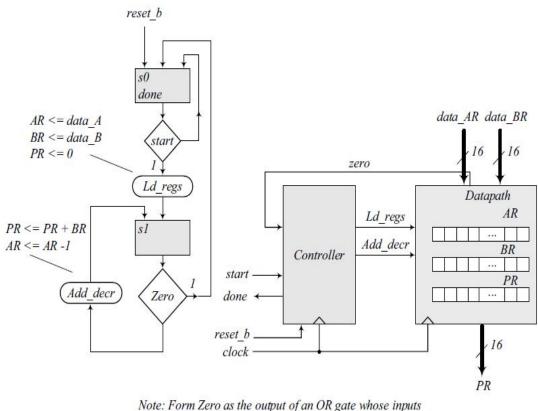

Ex: Develop a block diagram and an ASM chart for a digital *circuit* it multiply two binary numbers by the repeated-addition method. *For* example, *to* multiply 5 X 4, the digital system evaluates the product by adding the multiplication four times: 5 + 5 + 5 + 5 = 20. Design the circuit. Let the multiplicand be in register *BR*. the multiplier in register *AR*. add the product in register PR. An adder circuit adds the contents of BR to PR. A zero detection signal indicates whether AR is 0.

<u>Sol</u>: The internal architecture of the data path consists of a double-width register to hold the product (PR), a register to hold the multiplier (AR), a register to hold the multiplicand (BR), a double-width parallel adder, and single-width parallel adder. The single-width adder is used to implement the operation of decrementing the multiplier unit. Adding a word consisting entirely of 1s to the multiplier accomplishes the 2's complement subtraction of 1 from the multiplier. Figure below shows the ASM chart.

Note: Form Zero as the output of an OR gate whose inputs are the bits of the register AR.

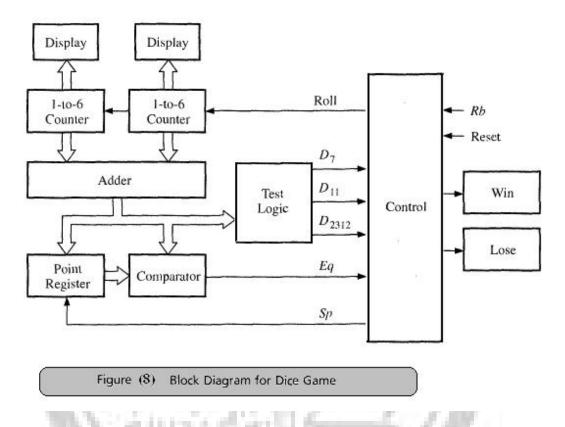

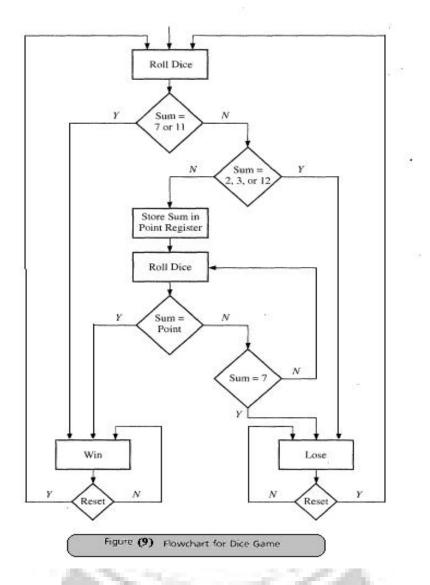

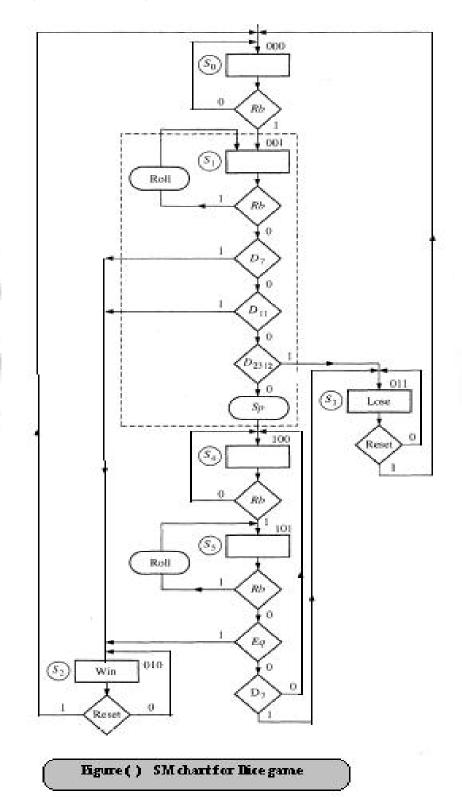

As another example of SM chart construction, we will design an electronic dice game. Figure (8) shows the block diagram for the dice game. Two counters are used to simulate the roll of the dice. The rules of the game are as follows:

1. After the first roll of the dice, the player wins if the sum is 7 or 11. He loses if the sum is 2, 3, or 12. Otherwise, the sum which he obtained on the first roll is referred to as his "point" and he must roll the dice again.

2. On the second or subsequent roll of the dice, he wins if the sum equals his point, and he loses if the sum is 7. Otherwise, he must roll again until he finally wins or loses.

The inputs to the dice game come from two push buttons,  $\mathbf{R}_{\mathbf{B}}$  (roll button) and *Reset. Reset* is used to initiate a new game. When the roll button is pushed, the dice counters count at a high speed, so the values cannot be read on the display. When the roll button is released, the values in the two counters are displayed and the game can proceed. If the *Win light* or *Lose light* is not on, the player must push the roll button again.

Figure (9) shows a flowchart for the dice game. After rolling the dice, the sum is tested. If it is 7 or 11, the player wins; if it is 2, 3, or 12, he *loses*. Otherwise the sum is saved in the point register and the player rolls again. If the new sum equals the point, he *wins*; if it is 7, he *loses*. Otherwise, he *rolls* again. After winning or losing, he must push *Reset* to begin a new game.

Input signals to the control network are defined as follows:

$D_7 = 1$  if the sum of the dice is 7

$D_{11} = 1$  if the sum of the dice is 11

$D_{2,3,12} = 1$  if the sum of the dice is 2, 3, or 12

$E_q = 1$  if the sum of the dice equals the number stored in the point register

$R_B = 1$  when the roll button is pressed

Reset = 1 when the reset button is pressed

Outputs from the control network are defined as follows:

Roll = 1 enables the dice counters

Sp = 1 causes the sum to be stored in the point register

Win = 1 turns on the win light

Lose = 1 turns on the lose light