FET Small Signal Analysis

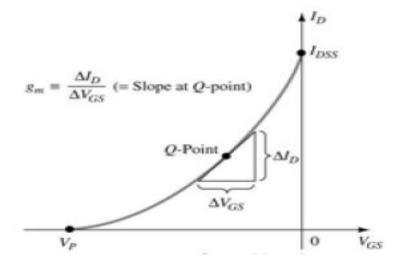

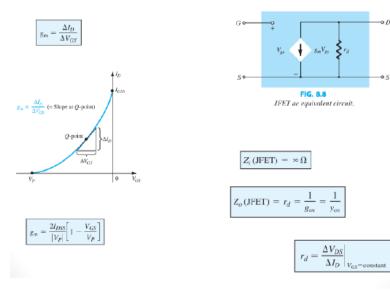

Mathematical Definition of gm

$$\begin{split} g_{m} &= \frac{\Delta I_{D}}{\Delta V_{GS}} = \frac{\partial I_{D}}{\partial V_{GS}} & I_{D} = I_{DSS} \bigg( 1 - \frac{V_{GS}}{V_{p}} \bigg)^{2} \\ & \left[ g_{m} = \frac{2I_{DSS}}{|V_{p}|} \bigg[ 1 - \frac{V_{GS}}{V_{p}} \bigg] \right] \\ g_{m} & \text{for } V_{GS} = 0 V; \qquad g_{m0} = \frac{2I_{DSS}}{|V_{p}|} \\ & \text{for } 1 - \frac{V_{GS}}{V_{p}} = \sqrt{\frac{I_{D}}{I_{DSS}}} & \left[ g_{m} = g_{m0} \sqrt{\frac{I_{D}}{I_{DSS}}} \right] \end{split}$$

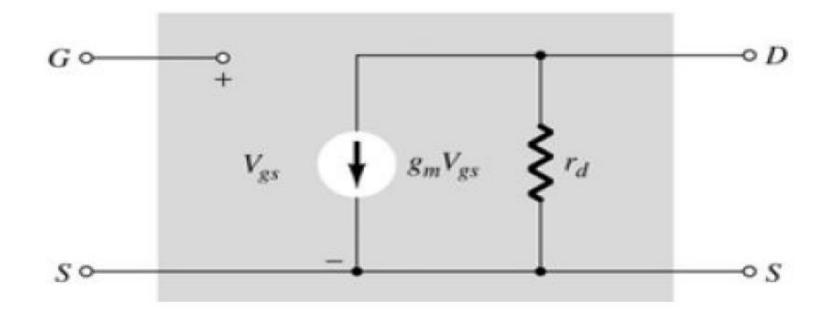

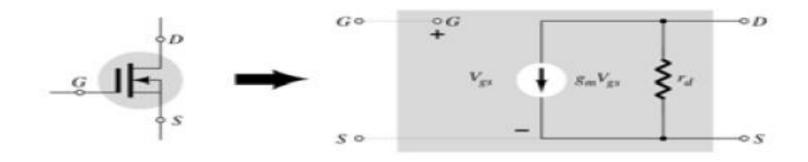

FET AC Equivalent Circuit

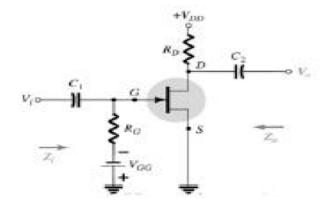

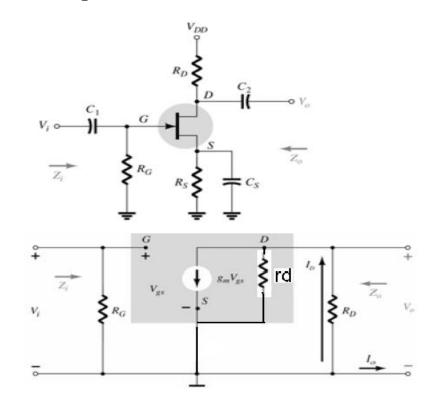

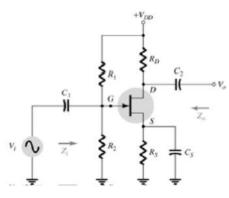

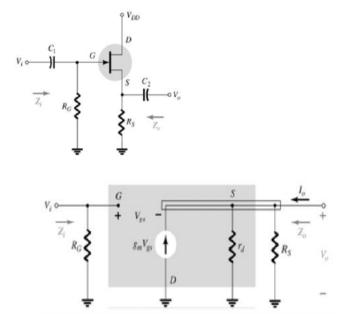

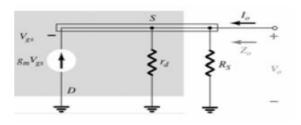

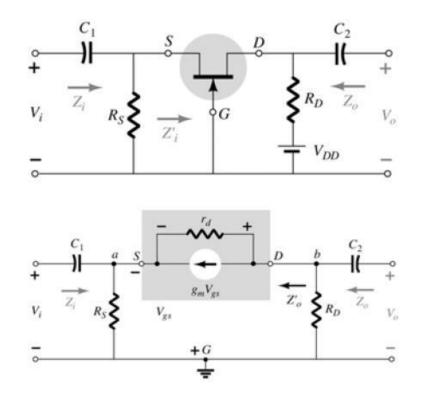

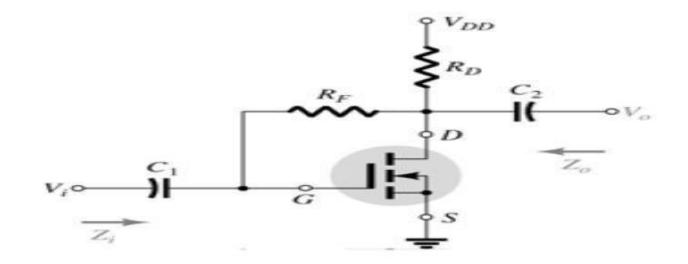

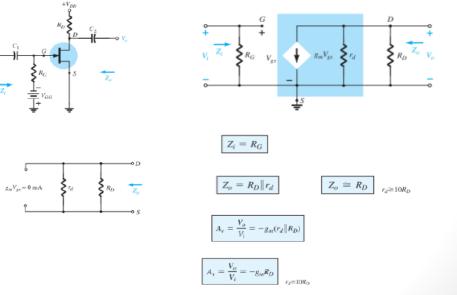

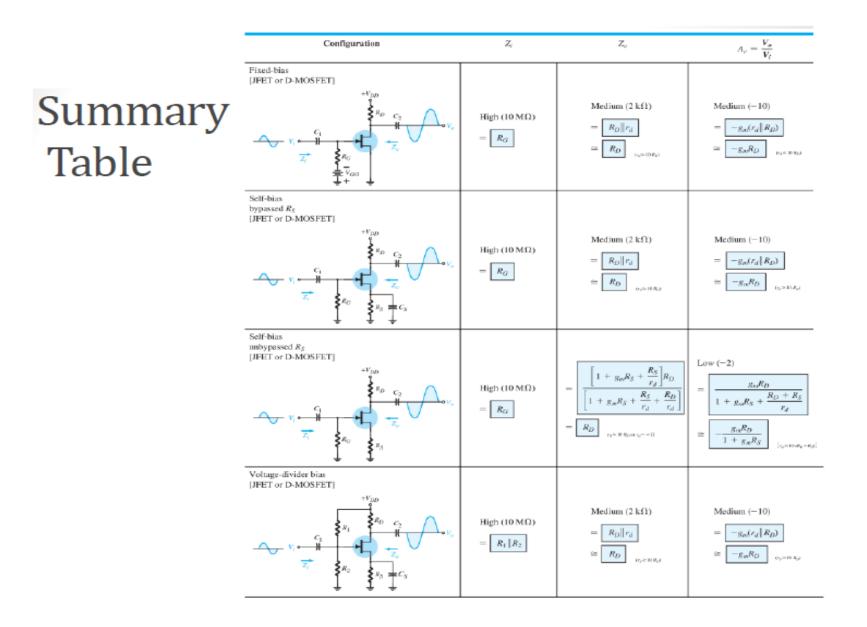

#### JFET Common-Source (CS) Fixed-Bias Configuration

- The input is on the gate and the output is on the drain.

- Fixed bias configuration includes the coupling capacitors c1 and c2 that isolate the dc biasing arrangements from the applied signal and load.

- They act as short circuit equivalents for the ac analysis.

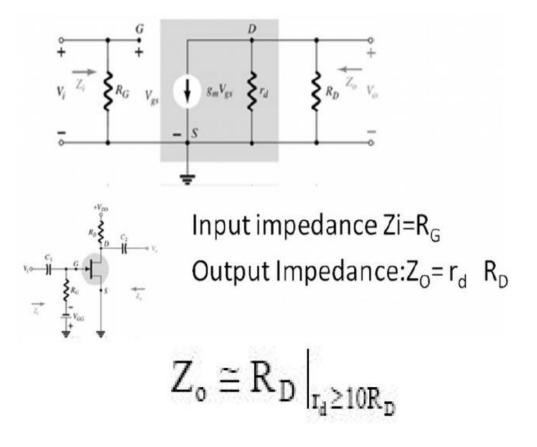

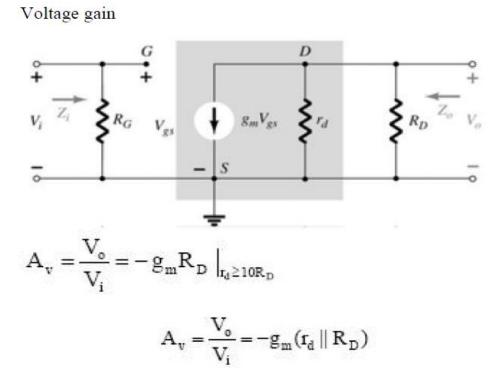

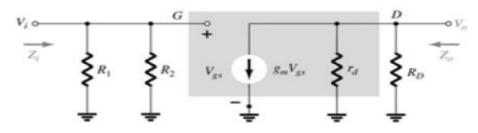

### AC Equivalent Circuit

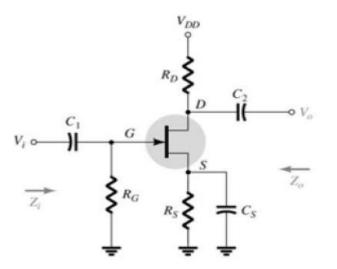

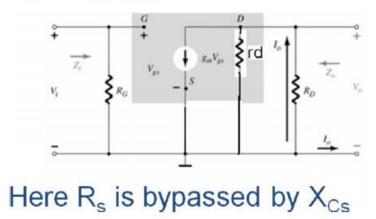

JFET Self bias configuration

- Main disadvantage of fixed bias configuration requires two dc voltage sources.

- Self bias circuit requires only one DC supply to establish the desired operating point.

#### Self bias configuration

If Cs is removed, it affects the gain of the circuit

#### AC Equivalent Circuit

# • The capacitor across the source resistance assumes its short circuit equivalent for dc allowing RS to define the operating point.

- Under ac conditions the capacitors assumes short circuit state and short circuits the Rs.

- If RS is left un-shorted, then ac gain will be reduced.

Redrawn equivalent circuit:

Circuit parameters:

- Since the resulting circuit is same as that of fixed bias configuration, all the parameter expression remains same as evaluated for fixed bias configuration.

- Input impedance Zi=RG

- Output Impedance :Zo= rd parallel RD

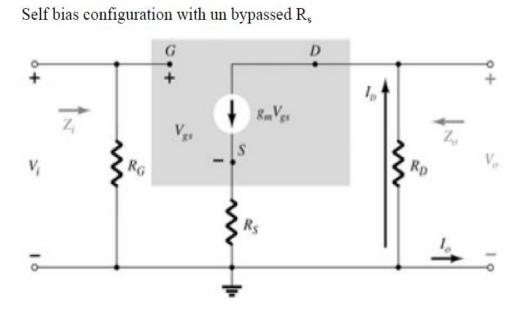

- Leaving Rs un-bypassed helps to reduce gain variations from device to device by providing degenerative current feedback. However, this method for minimizing gain variations is only effective when a substantial amount of gain is sacrificed.

$$\mathbf{A}_{\mathrm{v}} = -\mathbf{g}_{\mathrm{m}}(\mathbf{r}_{\mathrm{d}} || \mathbf{R}_{\mathrm{D}})$$

$$\mathbf{A}_{\mathrm{v}} = -\mathbf{g}_{\mathbf{m}} \mathbf{R}_{\mathbf{D}} \Big|_{\mathbf{r}_{\mathrm{d}} \ge 10 \mathbf{R}_{\mathrm{D}}}$$

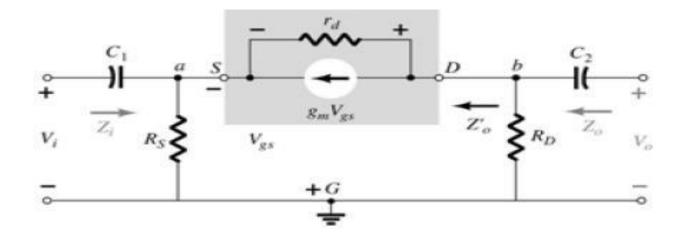

• Here R<sub>s</sub> is part of the equivalent circuit .

- Here Rs is part of the equivalent circuit .

- There is no way to reduce the network with lowest complexity.

- Carefully all the parameters have to be calculated by considering all polarities properly.

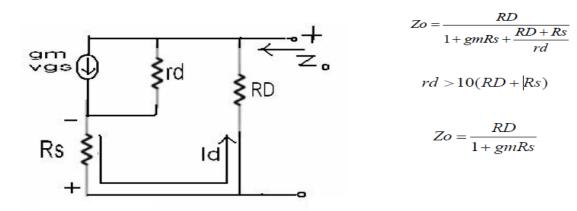

Output impedance is defined by

- ZO= Vo/Io at vi=0

- Setting Vi=0 results in following circuit

Setting Vi=0 results in following circuit.

· ----

Voltage gain:

$$Av = \frac{Vo}{Vi} = \frac{gmRD}{1+gmRs + \frac{RD+Rs}{rd}}$$

$$rd \ge 10(RD+Rs), Av = -\frac{gmRD}{1+gmRs}$$

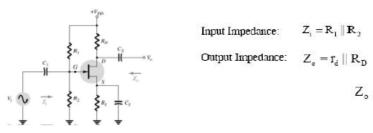

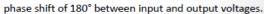

#### JFET voltage divider configuration

AC equivalent circuit

$Z_{\mathsf{o}} \cong R_{\mathsf{D}} \left|_{\mathsf{I}_{\mathsf{d}} \geq 10 \mathsf{R}_{\mathsf{D}}} \right|$

Voltage gain:

$\mathbf{A}_{\mathrm{v}} = -\mathbf{g}_{\mathrm{m}}(\mathbf{r}_{\mathrm{d}} \parallel \mathbf{R}_{\mathrm{D}})$

$$\mathbf{A}_{v} = -\mathbf{g}_{m} \mathbf{R}_{D} \left|_{\mathbf{r}_{d} \ge 10 \mathbf{R}_{D}}\right|$$

Note

- Equations for ZO and Av are same as in fixed bias.

- Only Zi is now dependent on parallel combination of R1 and R2.

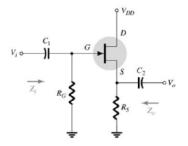

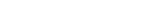

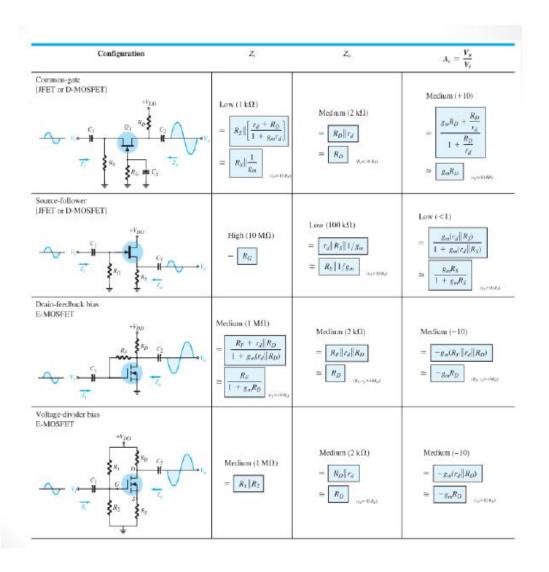

#### JFET source follower

- Input and output impedance:

- Input impedance : Zi=RG

- Output impedance :

- setting Vi=0V will result in the gate terminal being connected directly to ground as shown in figure below.

• Applying KCL at output node

$$I_{o} + g_{m}V_{gs} = I_{rd} + I_{RS}$$

$$= \frac{V_{o}}{r_{d}} + \frac{V_{o}}{R_{s}}$$

$$result : I_{o} = V_{o} \left[\frac{1}{r_{d}} + \frac{1}{R_{s}}\right] - g_{m}V_{gs}$$

$$= V_o \left[ \frac{1}{r_d} + \frac{1}{R_s} \right] - g_m V_{gs}$$

$$Z_o = \frac{V_o}{I_o} = \frac{V_o}{\left[\frac{1}{r_d} + \frac{1}{R_s} + g_m\right]} \frac{1}{V_0}$$

$$= \frac{1}{\left[\frac{1}{r_d} + \frac{1}{R_s} + g_m\right]}$$

$$Z_{o} \cong R_{s} \parallel \frac{1}{g_{m}} \mid _{r_{d} \ge 10R_{s}}$$

rd, Rs and gm are all in parallel. Voltage gain

$$\begin{aligned} \mathbf{A}_{v} = & \frac{\mathbf{V}_{o}}{\mathbf{V}_{i}} = \frac{\mathbf{g}_{m}(\mathbf{r}_{d} \parallel \mathbf{R}_{s})}{1 + \mathbf{g}_{m}(\mathbf{r}_{d} \parallel \mathbf{R}_{s})} \\ \\ \mathbf{A}_{v} = & \frac{\mathbf{g}_{m}\mathbf{R}_{s}}{1 + \mathbf{g}_{m}\mathbf{R}_{s}} \begin{vmatrix} \\ \mathbf{r}_{d} \ge 10\mathbf{R}_{s} \end{vmatrix} \end{aligned}$$

• Since denominator is larger by a factor of one, the gain can never be equal to or greater than one. (as in the case of emitter follower of BJT)

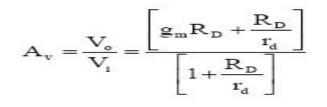

JFET common gate configuration

• The input is on source and the output is on the drain. Same as the common base in BJT

Input Impedance:

$$Z_i = R_s \parallel \left[ \frac{r_d + R_D}{1 + g_m r_d} \right]$$

$Z_i \cong R_s \parallel \frac{1}{g_m} \mid_{r_d \ge 10R_D}$

Output Impedance:  $Z_o = R_D || r_d$

$$Z_{\circ} \cong R_{D} \mid_{r_{d} \ge 10R_{D}}$$

$\mathbf{A}_{\mathrm{v}} = \mathbf{g}_{\mathrm{m}} \mathbf{R}_{\mathrm{D}} \mid_{\mathbf{r}_{\mathrm{d}} \ge 10 \mathbf{R}_{\mathrm{D}}}$

## **D-MOSFET ac equivalent model**

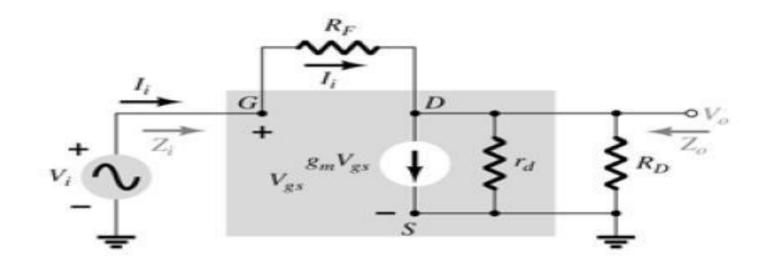

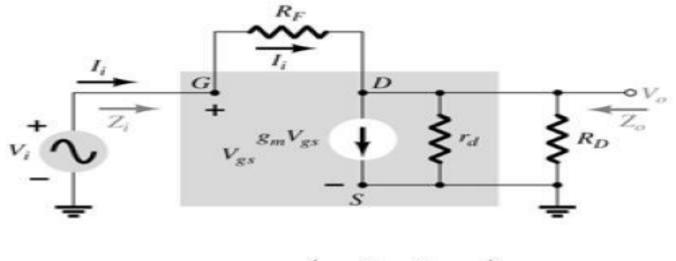

### **EMOSFET drain feedback configuration**

Input Impedance:

$$Z_i = \frac{R_F + r_d \parallel R_D}{1 + g_m(r_d \parallel R_D)}$$

Output Impedance:  $Z_o = R_F \parallel r_d \parallel R_D$

$Z_i \cong \frac{R_F}{1 + g_m R_D} \Big|_{R_F >> r_d \parallel R_D, r_d \ge 10R_D}$

$Z_o \cong R_D \Big|_{R_F >> r_d \parallel R_D, r_d \ge 10R_D}$

$$\begin{split} \mathbf{A}_{\mathrm{v}} &= -\mathbf{g}_{\mathrm{m}} \big( \mathbf{R}_{\mathrm{F}} \parallel \mathbf{r}_{\mathrm{d}} \parallel \mathbf{R}_{\mathrm{D}} \big) \\ \mathbf{A}_{\mathrm{v}} &\cong - \left. \mathbf{g}_{\mathrm{m}} \mathbf{R}_{\mathrm{D}} \right|_{\mathbf{R}_{\mathrm{F}} \gg \left. \mathbf{r}_{\mathrm{d}} \parallel \mathbf{R}_{\mathrm{D}}, \right. \left. \mathbf{r}_{\mathrm{d}} \ge 10 \mathbf{R}_{\mathrm{D}} \right] \end{split}$$

# JFET small signal Model

# **Fixed-Bias Configuration**

### **VOLTAGE-DIVIDER CONFIGURATION**

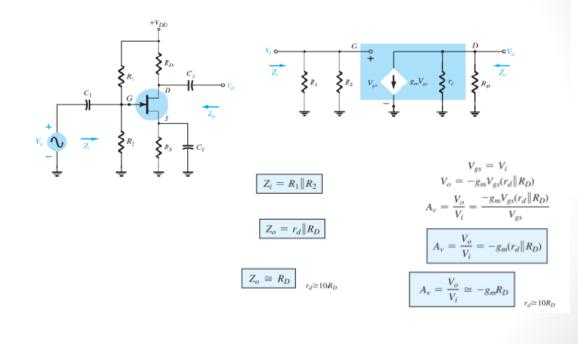

# Design FET Amplifier Network

**EXAMPLE 8.14** Choose the values of  $R_D$  and  $R_S$  for the network of Fig. 8.44 that will result in a gain of 8 using a relatively high level of  $g_{m}$  for this device defined at  $V_{GS_{0}} = \frac{1}{4}V_{P}$ .

$$= 5 \text{ mS} \left( 1 - \frac{(-1 \text{ V})}{(-4 \text{ V})} \right) = 3.75 \text{ mS}$$

The magnitude of the ac voltage gain is determined by

$|A_r| = g_m(R_D \| r_d)$

$$8 = (3.75 \text{ mS})(R_D || r_d)$$

$$R_D \| r_d = \frac{8}{3.75 \text{ mS}} = 2.13 \text{ k}\Omega$$

and

$$r_d = \frac{1}{g_{os}} = \frac{1}{20 \,\mu\text{S}} = 50 \,\text{k}\Omega$$

$$R_D \| 50 \,\text{k}\Omega = 2.13 \,\text{k}\Omega$$

$R_D = 2.2 \text{ k}\Omega$

The level of  $R_S$  is determined by the dc operating conditions as follows:

$$V_{GS_Q} = -I_D R_S$$

$$-1 \nabla = -(5.625 \text{ mA})R_S$$

$$R_S = \frac{1 \nabla}{5.625 \text{ mA}} = 177.8 \Omega$$

The closest standard value is 180  $\Omega$ . In this example,  $R_S$  does not appear in the ac design because of the shorting effect of  $C_{S^1}$

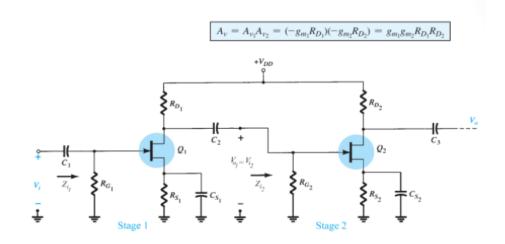

# **Cascaded Configuration**