Diyala University Computer & Software Engineering Department

# **Chapter 4**

### Sequential Logic Circuits

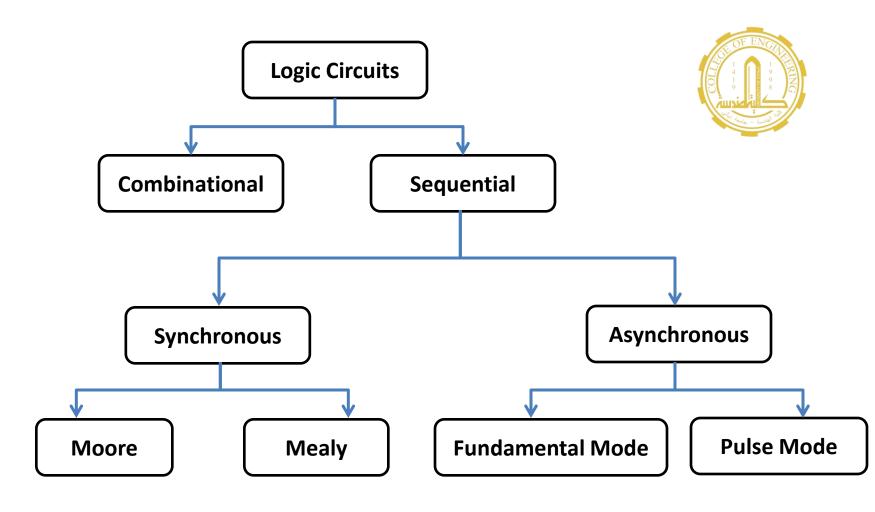

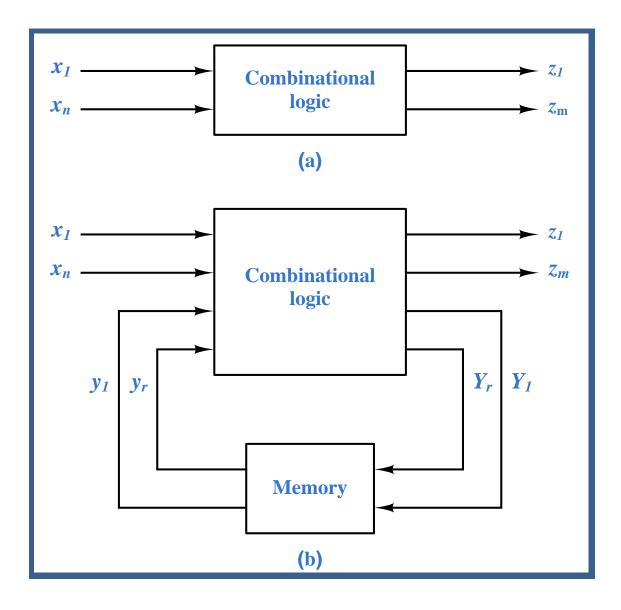

# **Types of Logic Circuits**

Combinational logic circuits:

- Outputs depend only on its current inputs.

- A combinational circuit may contain an arbitrary number of logic gates and inverters but no feedback loops.

- A feedback loop is a connection from the output of one gate to propagate back into the input of that same gate

- The function of a combinational circuit represented by a logic diagram is formally described using logic expressions and truth tables.

- Sequential logic circuits:

- Outputs depend not only on the current inputs but also on the past sequences of inputs.

- Sequential logic circuits contain combinational logic in addition to memory elements formed with feedback loops.

- The behavior of sequential circuits is formally described with state transition tables and diagrams.

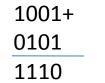

## **Combinational circuits example:**

9+5=14

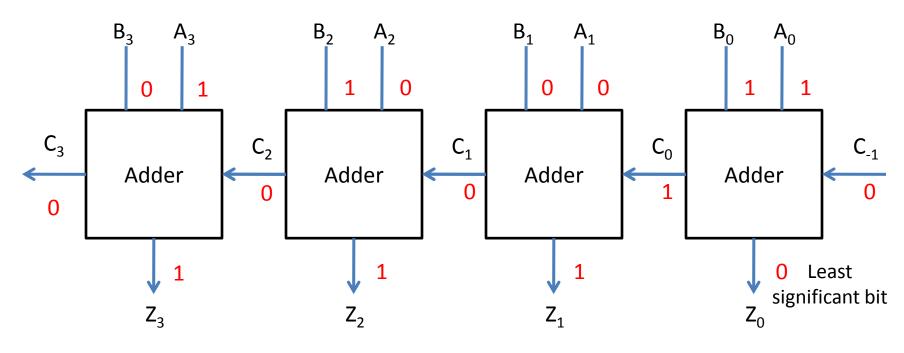

# Sequential circuits example:

### The Circuit Model

### Truth table for edge triggered flip flop

| Inp | uts  |   | Οι | utputs | Comment             |

|-----|------|---|----|--------|---------------------|

| J   | K    | С | Q  | Q'     |                     |

| 0   | 0    | + | Q  | Q'     | NC                  |

| 0   | 1    | + | 0  | 1      | Reset ( store<br>0) |

| 1   | 0    | + | 1  | 0      | Set(store 1)        |

| 1   | 1    | + | Q' | Q      | Toggle              |

| Inp | outs |   | Οι | utputs | Comment             |

| S   | R    | С | Q  | Q'     |                     |

| 0   | 0    | x | Q  | Q'     | NC                  |

| 0   | 1    | + | 0  | 1      | Reset ( store<br>0) |

| 1   | 0    | + | 1  | 0      | Set(store 1)        |

| 1   | 1    | + | ?  | ?      | Invalid             |

### Truth table for edge triggered flip flop

| Inputs | 5 | 0  | Comment |                  |

|--------|---|----|---------|------------------|

| D      | С | Q  | Q'      |                  |

| 1      | + | 1  | 0       | Set( store 1)    |

| 0      | + | 0  | 1       | Reset ( store 0) |

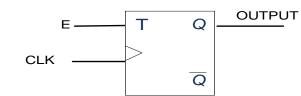

| Inputs |   | Οι | utputs  | Comment          |

| Т      | С | Q  | Q'      |                  |

| 1      | + | Q' | Q       | Reset(store 0)   |

| 0      | + | Q  | Q       | set ( store 1)   |

### **Excitation table**

| State tra                                | nsitior | ı                     |                                   |   | Ехс | itatio | on inp | outs |   |   |    |

|------------------------------------------|---------|-----------------------|-----------------------------------|---|-----|--------|--------|------|---|---|----|

| PS (q)                                   | N       | S (Q)                 | D                                 | 1 | -   | J      | К      | S    | R | J | К' |

| 0                                        |         | 0                     | 0                                 | C | )   | 0      | Х      | 0    | Х | 0 | X  |

| 0                                        |         | 1                     | 1                                 | 1 | -   | 1      | Х      | 1    | 0 | 1 | X  |

| 1                                        |         | 0                     | 0                                 | 1 | _   | Х      | 1      | 0    | 1 | Х | 0  |

| 1                                        |         | 1                     | 1                                 | C | )   | Х      | 0      | Х    | 0 | Х | 1  |

| present state (PS)<br>output Signal<br>q |         | ernal<br>signals<br>R | next state (I<br>output sigr<br>Q | - |     |        |        |      | 5 | J |    |

| 0                                        | 0       | 0                     | 0                                 |   |     |        |        |      |   |   |    |

| 0                                        | 0       | 1                     | 0                                 |   |     |        |        |      |   |   |    |

| 0                                        | 1       | 0                     | 1                                 |   |     |        |        |      |   |   |    |

| 0                                        | 1       | 1                     | 0                                 |   |     |        |        |      |   |   |    |

| 1                                        | 0       | 0                     | 1                                 |   |     |        |        |      |   |   |    |

| 1                                        | 0       | 1                     | 0                                 |   |     |        |        |      |   |   |    |

| 1                                        | 1       | 0                     | 1                                 |   |     |        |        |      |   |   |    |

| 1                                        | 1       | 1                     | 0                                 |   |     |        |        |      |   |   |    |

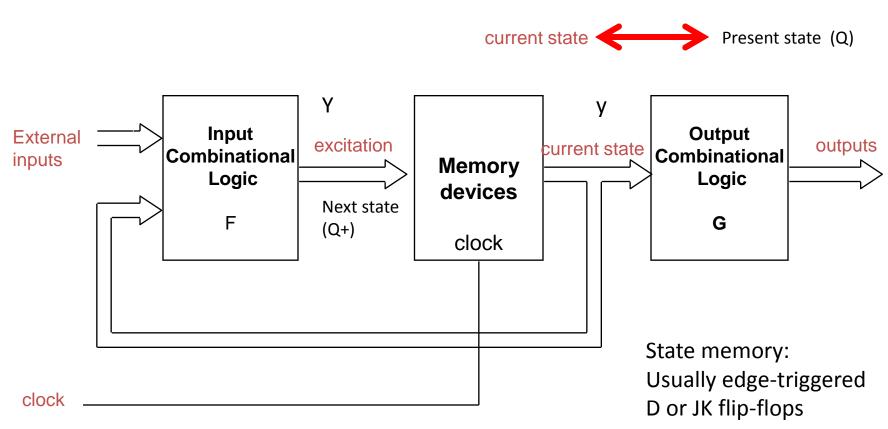

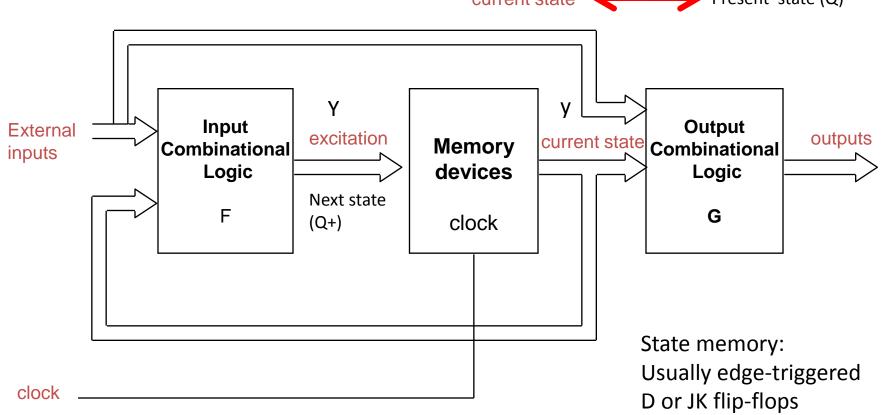

### Synchronous sequential logic circuits Clocked Synchronous State-Machines

- Such machines have the characteristics:

- Sequential circuits designed using flip-flops.

- All flip-flops use a common clock (clocked synchronous).

- A machine using n flip-flops (state memory) has n state variables (the outputs of the flip-flops) and 2<sup>n</sup> states.

- In general, the next state and output of the machine both depend on the current state of the machine and on the current input:

```

Next state = F(current state, input)

```

```

output = G(current state, input)

```

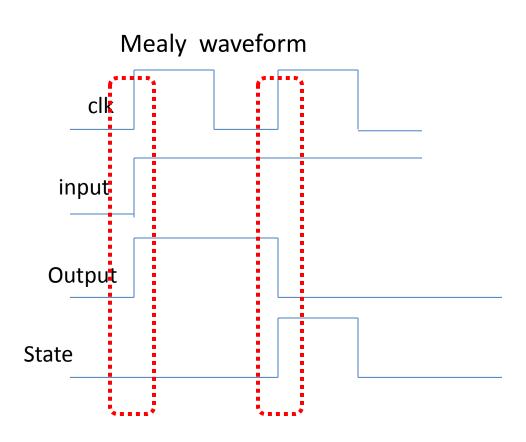

This type of state machine is called Mealy Machine

In some cases the next output depends only on the current state and not directly on the current input

```

Next state = F(current state, input)

```

```

output = G(current state)

```

Such machines are called Moore machines.

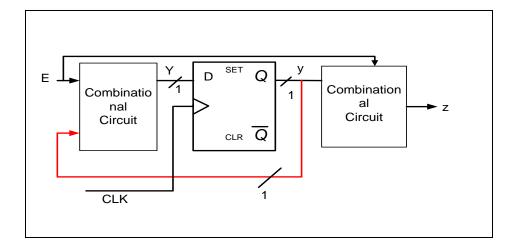

# Clocked Synchronous State-Machine Model

**Moore Machine**

# Clocked Synchronous State-Machine Model

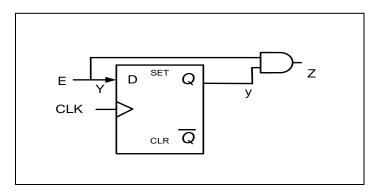

#### **Mealy machine**

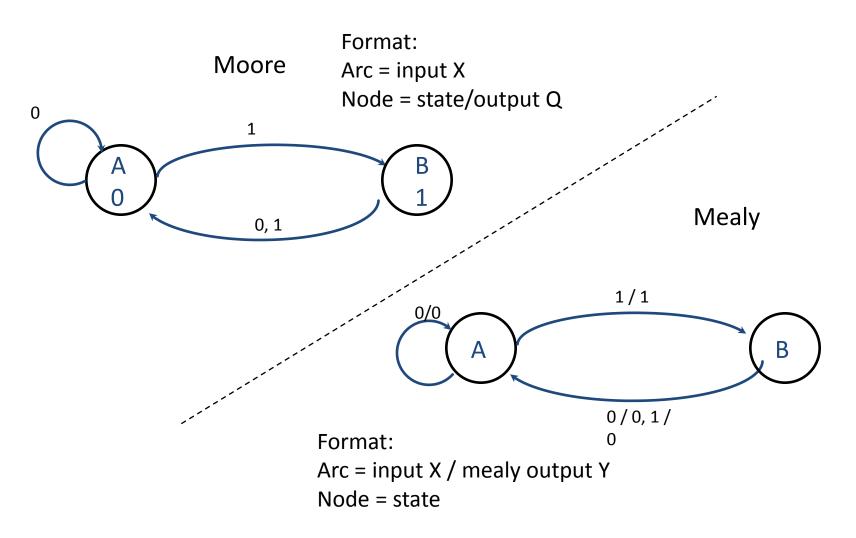

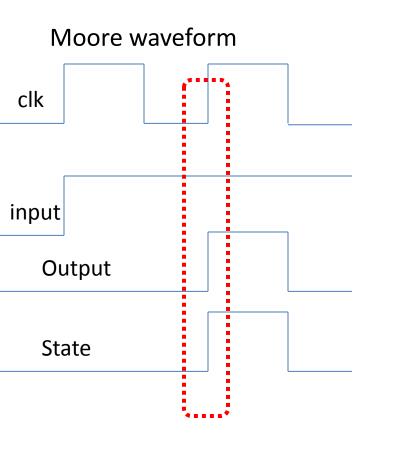

# Moore vs. Mealy

| Moore                                                                                                            | Mealy                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Next state = F(current state, input)<br>Output = G(current state)<br>Such machines are called Moore<br>machines. | Next state = F(current state, input)<br>Output = G(current state, input)<br>This type of state machine is<br>called Mealy Machine                                                                                         |

| •All state and output transitions occur<br>after falling/rising clock edge (Moore<br>don't have glitch)          | <ul> <li>State transitions occur after falling/rising clock edge (as with Moore machine)</li> <li>Output transitions occur in response to both input and state transition.</li> <li>(Mealy may be have glitch)</li> </ul> |

# )Moore vs. Mealy (State Diagram

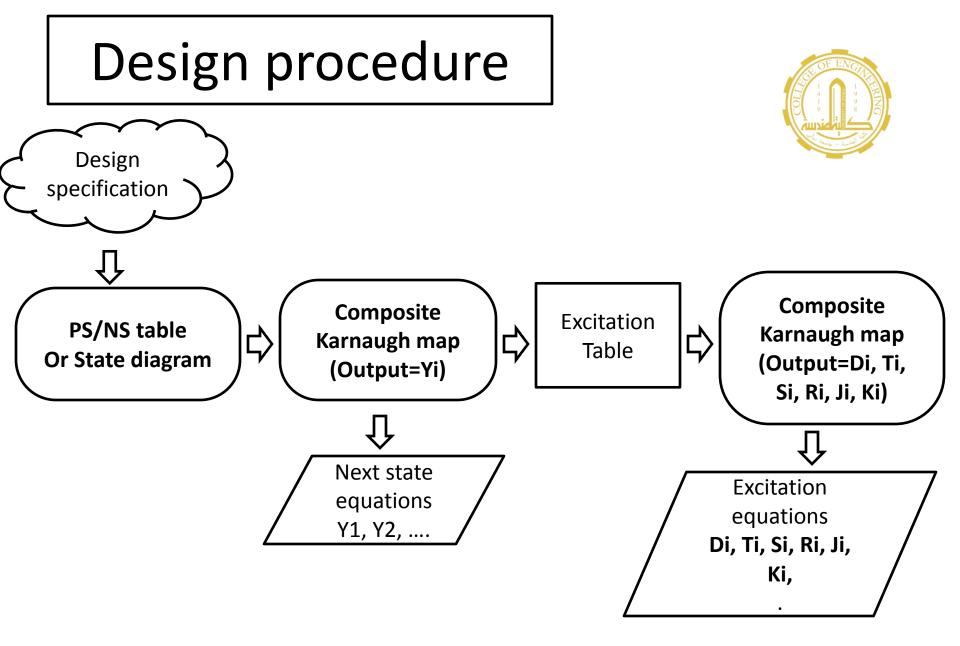

# **State Machine Design Procedure**

- **Step1**: Organize design specifications into a PS/NS table , state diagram, ASM chart, flow map or timing diagram from word description.

- **Step2**: Minimize number of states (optional, can result fewer flip-flops).

- **Step3**: State Assignment: Choose state variables (one variable for each flip-flop) and assign a unique code to each state.

Step 4: Choose flip-flop type (D, J-K, etc.)

- Build excitation table for flip-flop inputs from transition table.

- Derive excitation equations from excitation table.

- Derive output equations from PS/NS table.

<u>Step 5</u>: Draw logic diagram with excitation logic, output logic, and state memory elements.

#### Simple example 1

#### The specification :

An idle system is activated when an input, A is given. Then, an output, B is produced after two interval time or cycles later Next the system will be back to produced after two interval time or cycles later. Next, the system will be back to the idle state, waiting for the next triggering input A.

Step 1: Understand the specs

- Get a sample input/ output relationship

E:001001110

- Z:000010010

- Draw a simple block diagram

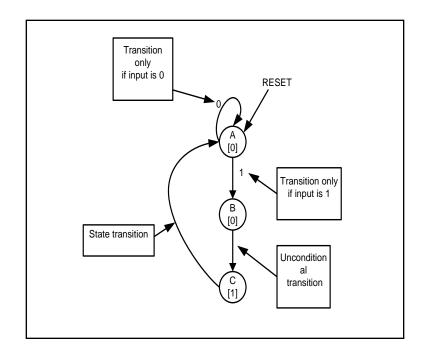

Step 2: Draw state diagram

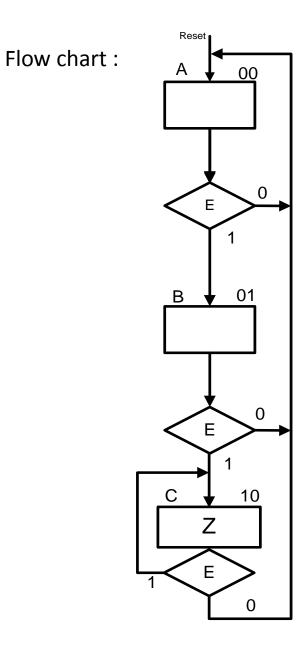

State table or state assignment

|       | E  |    |   |

|-------|----|----|---|

| S     | 0  | 1  | Z |

| А     | A  | В  | 0 |

| В     | C  | С  | 0 |

| С     | A  | A  | 1 |

|       |    | E  |   |

| y2 y1 | 0  | 1  | Z |

| 0 0   | 00 | 01 | 0 |

| 0 1   | 10 | 10 | 0 |

| 1 0   | 00 | 00 | 1 |

|       |    |    |   |

## State transition diagram 'STD'

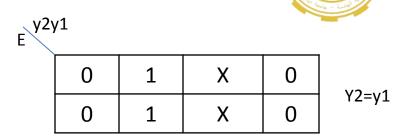

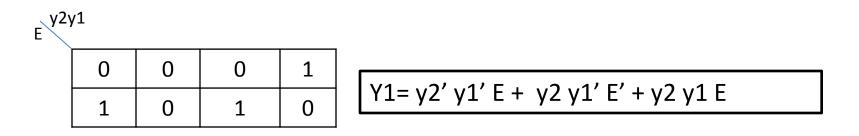

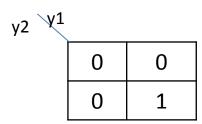

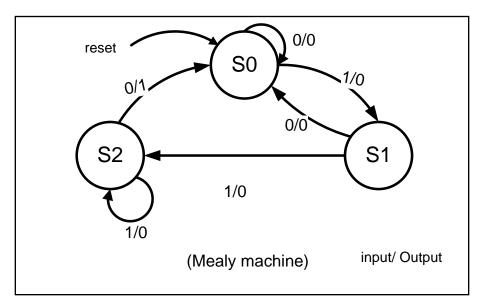

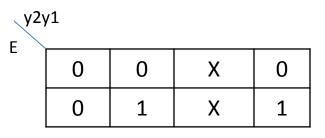

#### Next state &output equation

|      |           |    | E v2y1      |             |   |      |          |            |   |     |       |

|------|-----------|----|-------------|-------------|---|------|----------|------------|---|-----|-------|

|      |           |    |             |             |   | . [  | 0        | 1          | Х | 0   |       |

| Pr   | esent sta | te | Next        | Next state  |   |      | 0        | 1          | Х | 0   | Y2=y1 |

| (y2) | (y1)      | E  | y2+<br>(Y2) | y1+<br>(Y1) | Z | V    | 0.71     |            |   |     |       |

| 0    | 0         | 0  | 0           | 0           |   | E V2 | .у⊥<br>` |            |   |     | 7     |

| 0    | 0         | 1  | 0           | 1           | 0 |      | 0        | 0          | X | 0   |       |

| 0    | 1         | 0  | 1           | 0           | 0 |      | 1        | 0          | X | 0   |       |

| 0    | 1         | 1  | 1           | 0           | 0 |      | V1-v     | · <u> </u> |   |     |       |

| 1    | 0         | 0  | 0           | 0           | 1 |      | y2       | 2 y1 I     | _ |     |       |

| 1    | 0         | 1  | 0           | 0           | 1 |      | y Z      | 0          | 0 |     |       |

| 1    | 1         | 0  | Х           | Х           | x |      |          | 1          | X | OUT | =y2=Z |

| 1    | 1         | 1  | Х           | Х           |   |      |          |            |   |     |       |

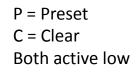

Another method and continue step: Step 3: get symbolic state table

| Present<br>state | Input | Next<br>state | Output |

|------------------|-------|---------------|--------|

|                  | Е     |               | Z      |

| SO               | 0     | SO            | 0      |

| 30               | 1     | S1            | 0      |

| <b>C1</b>        | 0     | S2            | 0      |

| S1               | 1     | S2            | 0      |

| 62               | 0     | SO            | 1      |

| S2               | 1     | SO            | 1      |

| Step 4 : | auto - and |       |        |  |  |  |  |  |

|----------|------------|-------|--------|--|--|--|--|--|

| -        | assignment |       |        |  |  |  |  |  |

| Present  | Input      | Next  | Output |  |  |  |  |  |

| state    |            | state |        |  |  |  |  |  |

|          | E          |       | Z      |  |  |  |  |  |

| S0=00    | 0          | 00    | 0      |  |  |  |  |  |

| 50-00    | 1          | 01    | 0      |  |  |  |  |  |

| 61-01    | 0          | 10    |        |  |  |  |  |  |

| S1=01    | 1          | 10    | 0      |  |  |  |  |  |

| 62, 10   | 0          | 00    | 1      |  |  |  |  |  |

| S2=10    | 1          | 00    | 1      |  |  |  |  |  |

| S3=11    | 0          | 11    | v      |  |  |  |  |  |

| 33-11    | 1          | 11    | X      |  |  |  |  |  |

#### Next state & output equation

|    | sent<br>ate | Input | Next state |    | Outpu<br>t |

|----|-------------|-------|------------|----|------------|

| y2 | y1          | E     | Y2         | Y1 | Z          |

| 0  | 0           | 0     | 0          | 0  | 0          |

| 0  | 0           | 1     | 0          | 1  | 0          |

| 0  | 1           | 0     | 1          | 0  | 0          |

| 0  | 1           | 1     | 1          | 0  | 0          |

| 1  | 0           | 0     | 0          | 0  | 1          |

| 1  | 0           | 1     | 0          | 0  | 1          |

| 1  | 1           | 0     | Х          | Х  | , v        |

| 1  | 1           | 1     | Х          | Х  | Х          |

$$\begin{array}{ccccc}

Y1 = & y2' & y1' & E \\

y2 & & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

& & & \\

&$$

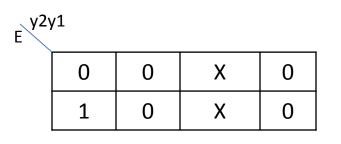

Z=y2

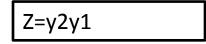

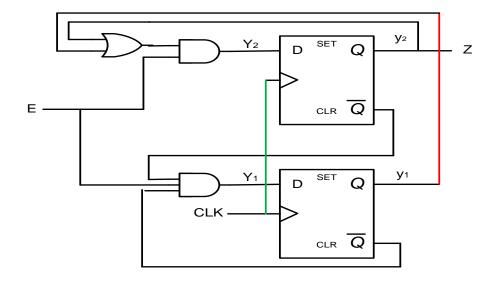

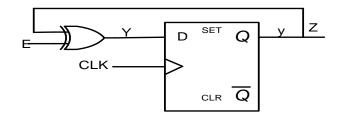

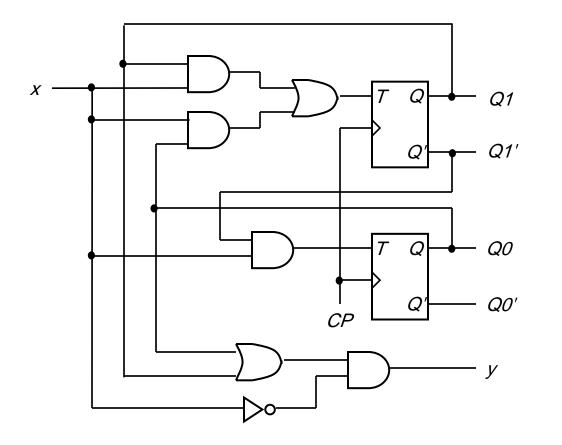

### Circuit diagram

Timing diagram : in class

### Example 2 State Machine Design :110 Detector " MOORE"

- Word description (110 input sequence detector):

- Design a state machine with input" E" and output "Z".

- Z should be 1 whenever the sequence 110 has been detected on "E" on the last 3 consecutive rising clock edges (or ticks).

- Otherwise, Z = 0

- Note: this is a Moore machine, that is the output, Z, depends only on inputs at previous clocks rising edges, not on the current input.

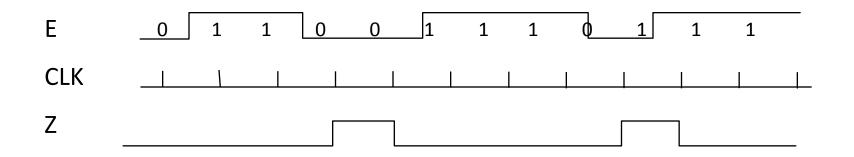

- Timing diagram interpretation of word description (only rising clock edges are shown):

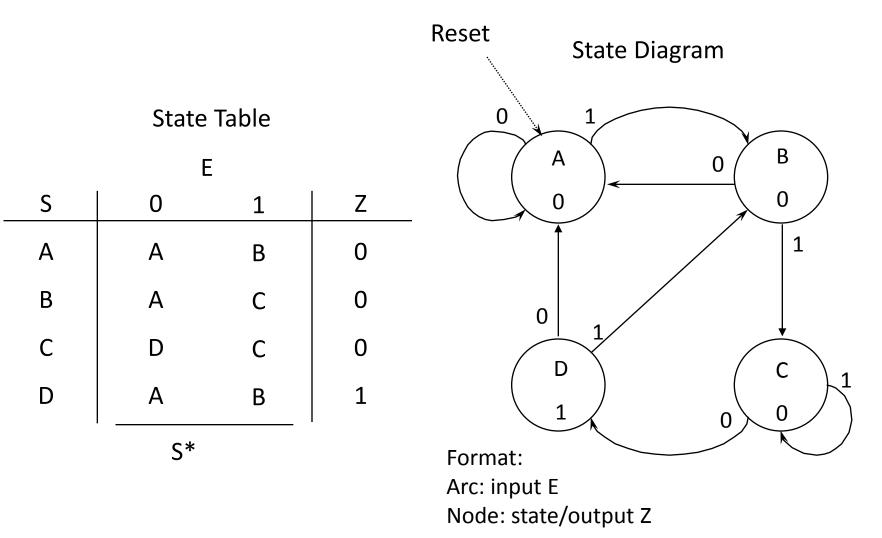

### State Machine Design Example 2: 110 Detector Step1: Choosing States

Possible states (What does the state machine need to remember?):

| <ul> <li>Initial</li> </ul> | : power up, no clocks yet         | Z = 0 |       |

|-----------------------------|-----------------------------------|-------|-------|

| – A                         | : first 1 not found               | Z = 0 |       |

| — B                         | : first 1 found                   |       | Z = 0 |

| - C                         | : at least 2 consecutive 1s found |       | Z = 0 |

| – D                         | : found 1 1 0                     |       | Z = 1 |

- Are all the states needed?

- Notice: Initial is equivalent to

- We can drop the state Initial and replace it with state

### State Machine Design Example 2: 110 Detector Step 1: State/Output Table and Diagram

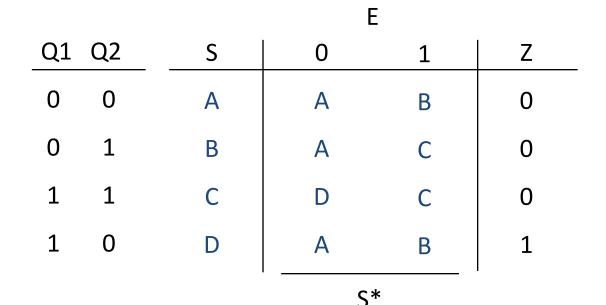

### State Machine Design Example 2: 110 Detector Step 3: State Assignment

- Choose state variable assignments:

- Initial state all 0s

- $Q2 = last E, so Q2^* = E$

- minimize number of transitions

### State Machine Design Example 2: 110 Detector Step 4: Transition/Output Table

Step 4: Build transition/output table from state/output table by substituting state variable combinations instead of state names.

|     | F                               |                                                        |                                                        | -                                                      | -                                                     |                                                       |

|-----|---------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 0   | - 1                             | Z                                                      | Q1 Q2                                                  | 0                                                      | 1                                                     | Z                                                     |

| 00  | 01                              | 0                                                      | SO                                                     | S0                                                     | S1                                                    | 0                                                     |

| 00  | 11                              | 0                                                      | S1                                                     | SO                                                     | S3                                                    | 0                                                     |

| 10  | 11                              | 0                                                      | S3                                                     | S2                                                     | S3                                                    | 0                                                     |

| 00  | 01                              | 1                                                      | S2                                                     | SO                                                     | S1                                                    | 1                                                     |

| 01  | *                               | I                                                      |                                                        | <del>(</del> 1* (                                      | 22*                                                   |                                                       |

| =D1 | D2 ←                            | — Step 6                                               |                                                        |                                                        |                                                       | –Step 6                                               |

|     | 0<br>00<br>00<br>10<br>00<br>Q1 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

- Step 4: Choose D Flip-Flops , so Q\*= D

- Step 4: Excitation table:

Same as Transition/output table with Q1\*=D1, Q2\*=D2

Symbolic state table

#### Encoded State table

| Present<br>state | Input | Next<br>States | Output |

|------------------|-------|----------------|--------|

|                  | E     |                | Z      |

| SO               | 0     | SO             | 0      |

|                  | 1     | S1             |        |

| S1               | 0     | SO             | 0      |

|                  | 1     | S3             |        |

| S2               | 0     | SO             | 0      |

|                  | 1     | S1             |        |

| S3               | 0     | S2             | 1      |

|                  | 1     | S3             |        |

| Present state |    | Input | Next States |    | Output   |

|---------------|----|-------|-------------|----|----------|

| y2            | y1 | E     | Y2          | Y1 | Z        |

| 0             | 0  | 0     | 0           | 0  | 0        |

| 0             | 0  | 1     | 0           | 1  |          |

| 0             | 1  | 0     | 0           | 0  | 0        |

| 0             | 1  | 1     | 1           | 1  |          |

| 1             | 0  | 0     | 0           | 0  | 0        |

| 1             | 0  | 1     | 0           | 1  |          |

| 1             | 1  | 0     | 1           | 0  | 1        |

| 1             | 1  | 1     | 1           | 1  | <u> </u> |

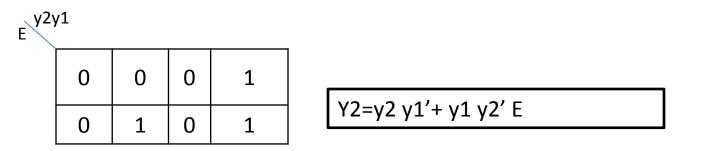

### State Machine Design Example 2: 110 Detector Steps 4: Excitation/Output Equations

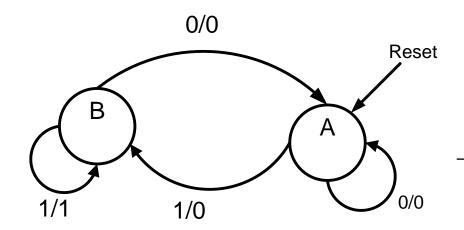

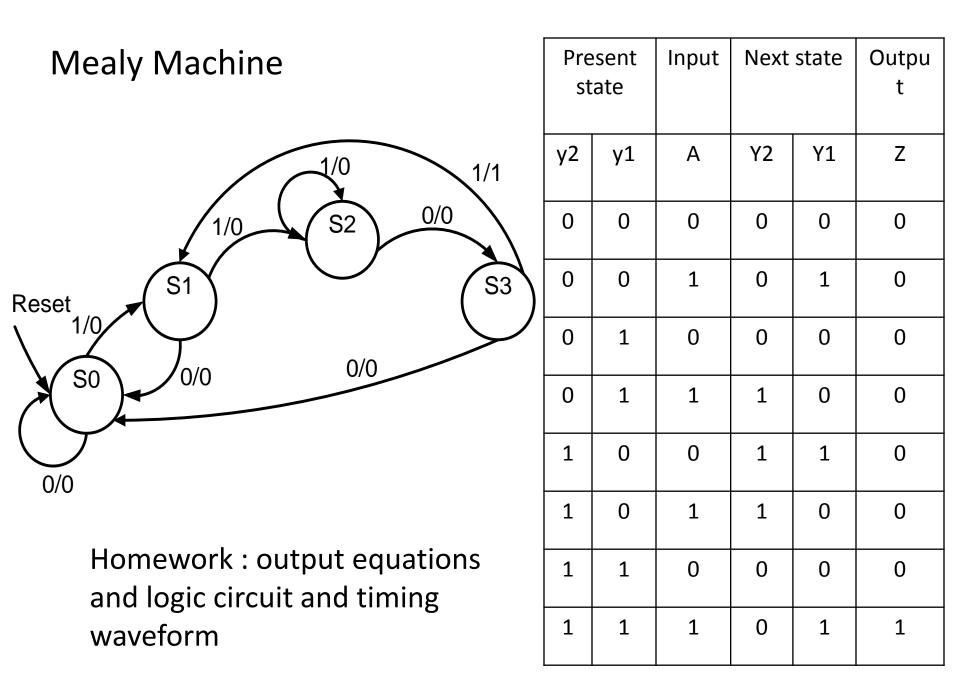

#### Example 2 State Machine Design :110 Detector " MEALY "

From specification example 2: understand the problem, S0 means 0 bit found, S1=1 bit found, S2=bits found . If all the third bit is detected (110) completed while S2 reset go to S0 while at the same time outputting a 1

| Present<br>state | Input | Next<br>States | Output |

|------------------|-------|----------------|--------|

|                  | E     |                | Z      |

| 0.2              | 0     | SO             | 0      |

| SO               | 1     | S1             | 0      |

| S1               | 0     | SO             | 0      |

| 51               | 1     | S2             | 0      |

| S2               | 0     | SO             | 1      |

| 52               | 1     | S2             | 0      |

#### State assignment table

| Present state |    | Input | Next States |    | Output |

|---------------|----|-------|-------------|----|--------|

| y2            | y1 | E     | Y2          | Y1 | Z      |

| 0             | 0  | 0     | 0           | 0  | 0      |

| 0             | 0  | 1     | 0           | 1  | 0      |

| 0             | 1  | 0     | 0           | 0  | 0      |

| 0             | 1  | 1     | 1           | 0  | 0      |

| 1             | 0  | 0     | 0           | 0  | 1      |

| 1             | 0  | 1     | 1           | 0  | 0      |

| 1             | 1  | 0     | Х           | Х  | Х      |

| 1             | 1  | 1     | Х           | Х  | Х      |

HOME WORK : circuit diagram

$Y1=y\overline{2} y\overline{1} E$

Z=y2 E

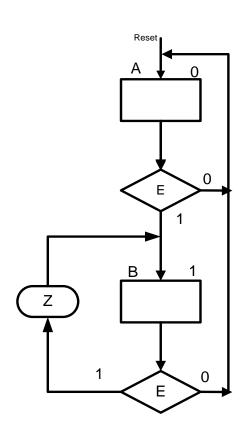

#### Example: "Moore"

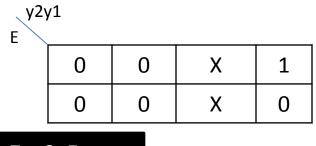

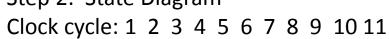

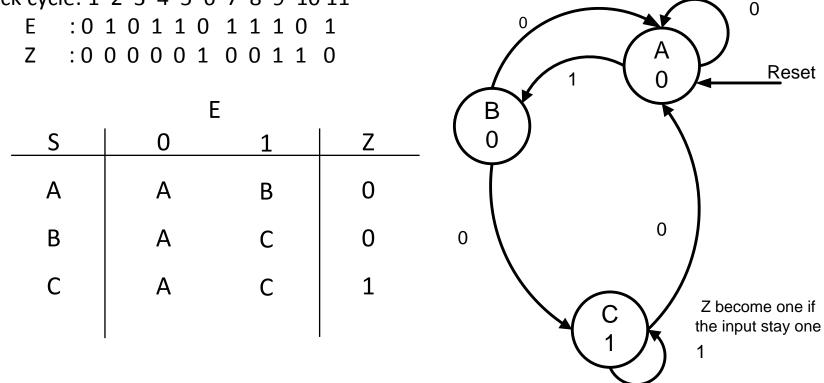

Design sequence logic circuit has one input, E, and one output, Z. All changes in the circuit occur on the positive edge of a clock signal. The output Z is equal to 1 if during two immediately preceding clock cycles the input E was equal to 1. Otherwise, the value of Z is equal to 0. Step 1: understand the question

Thus, the circuit detects if two or more consecutive 1s occur on its input E. Circuits that detect the occurrence of a particular pattern on its inputs are referred to as sequence detectors. Step 2: State Diagram

### State assignment table

| Present<br>state | Input | Next<br>States | Output |  |

|------------------|-------|----------------|--------|--|

|                  | E     |                | Z      |  |

| SO               | 0     | SO             | 0      |  |

| 50               | 1     | S1             |        |  |

| S1               | 0     | SO             | 0      |  |

| 51               | 1     | S2             | 0      |  |

| S2               | 0     | SO             | 1      |  |

| 52               | 1     | S2             |        |  |

| S3               | 0     | S3             | х      |  |

| 35               | 1     | S3             | ^      |  |

| Present state |    | Input | Next States |    | Output |

|---------------|----|-------|-------------|----|--------|

| y2            | y1 | E     | Y2          | Y1 | Z      |

| 0             | 0  | 0     | 0           | 0  | 0      |

| 0             | 0  | 1     | 0           | 1  |        |

| 0             | 1  | 0     | 0           | 0  | 0      |

| 0             | 1  | 1     | 1           | 0  | U      |

| 1             | 0  | 0     | 0           | 0  | 1      |

| 1             | 0  | 1     | 1           | 0  | 1      |

| 1             | 1  | 0     | Х           | Х  | v      |

| 1             | 1  | 1     | Х           | Х  | X      |

#### Logic circuit diagram

Same example : Mealy

Moore

Clock cycle: 1 2 3 4 5 6 7 8 9 10 11 E : 0 1 0 1 1 0 1 1 0 1 Z : 0 0 0 0 1 0 0 1 1 0 0 Clock cycle: 1 2 3 4 5 6 7 8 9 10 11 E : 0 1 0 1 1 0 1 1 0 1 Z : 0 0 0 0 0 1 0 0 1 1 0

| E(Y) |            |   |    |  |  |

|------|------------|---|----|--|--|

| S(y) | 0          | 1 | Z  |  |  |

| А    | А          | В | 00 |  |  |

| В    | А          | В | 01 |  |  |

|      |            |   | 1  |  |  |

|      | Y=E<br>Z=E |   |    |  |  |

|      | Z-C        | У |    |  |  |

#### Flow chart :

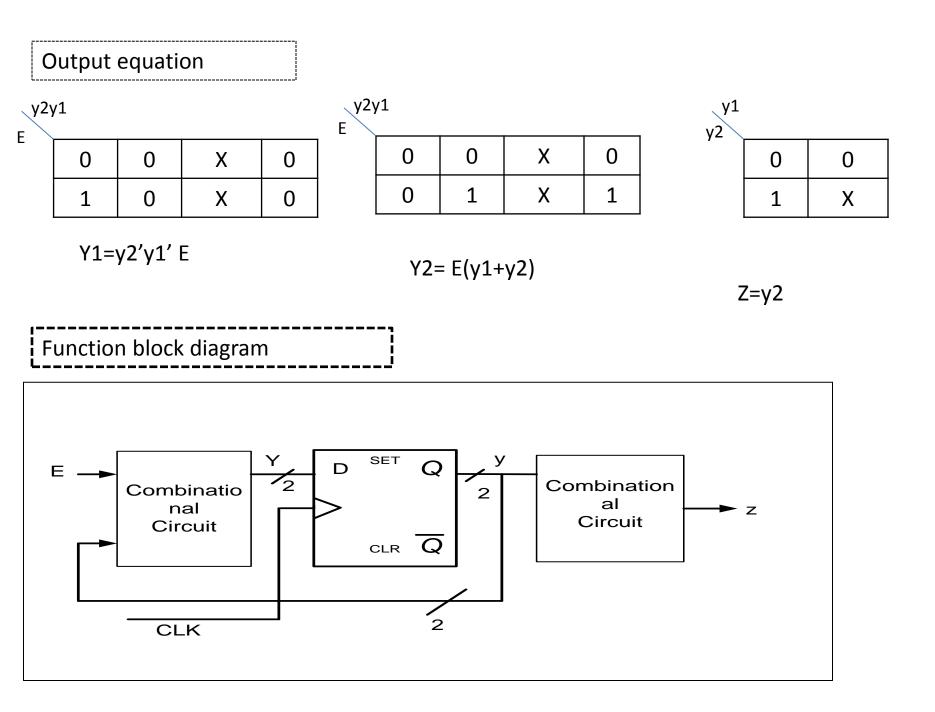

#### Function block diagram

#### Logic circuit diagram

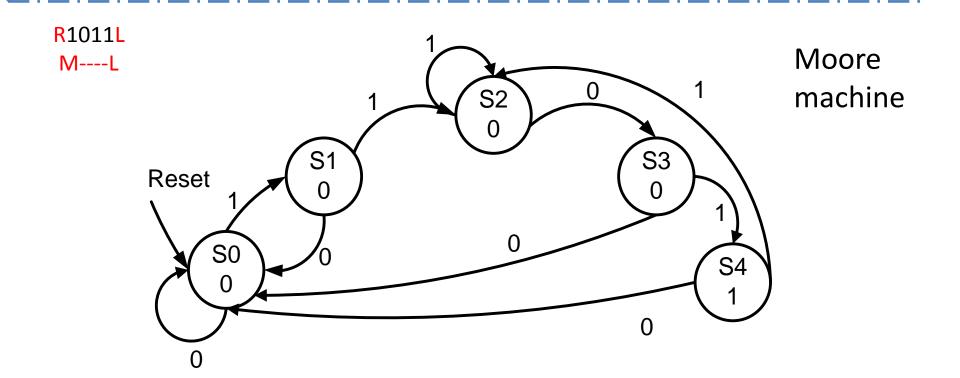

#### Example: Robotic Smile

Designer owns a pet robotic snail with an FSM brain. The snail crawls from left to right along a paper tape containing a sequence of 1's and 0's. On each clock cycle, the snail crawls to the next bit. The snail smiles when the last four bits that it has crawled over are, from left to right, 1011. Design the FSM to computer when the snail should smile. The input A is the bit underneath the snail's antennae. The output Y is true when the snail

smiles. Compare Moore and Mealy state machine designs. Sketch a timing diagram for each machine showing the input, states and output as your snail crawls along the sequence 111011010.

| Preset<br>y | Input<br>(E) | NEXT<br>STATE (Y) | OUTPUT<br>(Z) |  |

|-------------|--------------|-------------------|---------------|--|

| SO          | 0            | SO                | 0             |  |

| SO          | 1            | S1                | 0             |  |

| S1          | 0            | SO                | 0             |  |

| S1          | 1            | S2                | 0             |  |

| S2          | 0            | S3                | 0             |  |

| S2          | 1            | S2                | 0             |  |

| S3          | 0            | SO                | 0             |  |

| S3          | 1            | S4                | 0             |  |

| S4          | 0            | SO                | 1             |  |

| S4          | 1            | S2                | 1             |  |

Homework : output equations and logic circuit and timing waveform

|    | Prese | t  | Input | NEXT STATE |    | output |   |

|----|-------|----|-------|------------|----|--------|---|

| y2 | y1    | y0 | E     | Y2         | Y1 | YO     | Z |

| 0  | 0     | 0  | 0     | 0          | 0  | 0      | 0 |

| 0  | 0     | 0  | 1     | 0          | 0  | 1      | 0 |

| 0  | 0     | 1  | 0     | 0          | 0  | 0      | 0 |

| 0  | 0     | 1  | 1     | 0          | 1  | 0      | 0 |

| 0  | 1     | 0  | 0     | 0          | 1  | 1      | 0 |

| 0  | 1     | 0  | 1     | 0          | 1  | 0      | 0 |

| 0  | 1     | 1  | 0     | 0          | 0  | 0      | 0 |

| 0  | 1     | 1  | 1     | 1          | 0  | 0      | 0 |

| 1  | 0     | 0  | 0     | 0          | 0  | 0      | 1 |

| 1  | 0     | 0  | 1     | 0          | 1  | 0      |   |

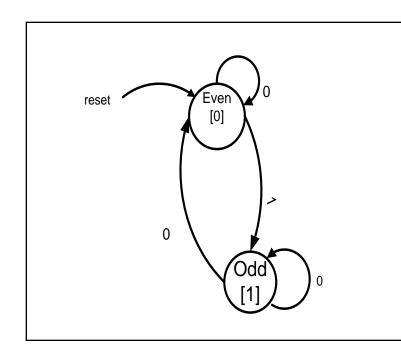

Example 3: odd parity checker Introduction:

UART (universal asynchronous receiver transmitter) is an example. Recovery from the error is usually done by retransmitting the data that use in telecommunication. Consider an *even parity scheme* using nine bit codewords. The code comprises 8 data bits followed by a parity bit. The following examples would make the parity scheme clear:

The parity of the data 1111 1110 is odd since there are 7 numbers of '1' bits in the data. The parity bit will be 1, giving the code word 1111 1110 1.

The parity of the data 1111 1111 is even as there are 8 numbers of '1' bits . The parity bit is 0, giving the code word 1111 1111 0.

The parity of the data 0000 0000 is even (zero being an even number). The parity bit is 0, giving the code word 0000 0000 0.

A null or non-existent bit stream also has zero '1' bits and, therefore, it would get the parity bit 0 in an even parity scheme. The specification: Assert output whenever input bit stream has odd # of 1's. Step 1: understand the specs.

Get sample input/output relationship. In class

Step 2 : draw state diagram, step 3: symbolic state table,

| Present  | Next state(Y) |      | Out (7) |

|----------|---------------|------|---------|

| (y)state | E=0           | E=1  | Out (Z) |

| Even     | Even          | odd  | 0       |

| Odd      | odd           | Even | 1       |

| Present<br>state | Input | Next state | Output |

|------------------|-------|------------|--------|

| Even             | 0     | Even       | 0      |

| Even             | 1     | Odd        | 0      |

| Odd              | 0     | Odd        | 1      |

| Odd              | 1     | Even       | 1      |

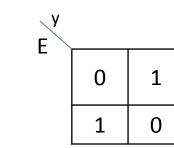

#### Step 4 :Encoded state transition table & Step 5 : output equations

| Present<br>state | Input | Next<br>state | Output |

|------------------|-------|---------------|--------|

| У                | E     | Y             | Z      |

| 0                | 0     | 0             | 0      |

| 0                | 1     | 1             | 0      |

| 1                | 0     | 1             | 1      |

| 1                | 1     | 0             | 1      |

Y=y ^ E

| Present<br>(y)state | Next s | Out (Z) |   |

|---------------------|--------|---------|---|

|                     | E=0    | E=1     |   |

| 0                   | 0      | 1       | 0 |

| 1                   | 1      | 0       | 1 |

Timing in class

#### Latch/Flip-Flop Characteristic Equations

<u>Device</u>

**Characteristic Equations**

S-R latch D latch

Edge-triggered D flip-flop Master/Slave S-R flip-flop Master/Slave J-K flip flop Edge Triggered J-K flip-flop T flip-flop with enable Q + = S + R'.Q Q + = D Q + = D Q + = S + R'.Q Q + = J.Q' + K'.Q Q + = J.Q' + K'.Q Q + = Q' + K'.QQ + = EN.Q' + EN'.Q

## **State Machine Analysis Procedure**

<u>Step1</u>: Assign s state variable to each flip-flop in the synchronous sequential logic circuit.

<u>Step2</u>: Analyze the combinational logic to determine flip-flop input (excitation) equations: Di = Fi (Q, inputs)

Also write the Moore and/or Mealy output equations.

<u>Step3</u>: Substitute excitation equations into flip-flop characteristic equations, to obtain the next state output equations.

<u>Step 4</u>: Obtain a composite Karnaugh map using the next state output equations and Moore and/or Mealy output equations

<u>Step 5</u>: Use the composite Karnaugh map to obtain a PS/NS table, state diagram, ASM chart, flow map or timing diagram to show the behavior of the circuit.

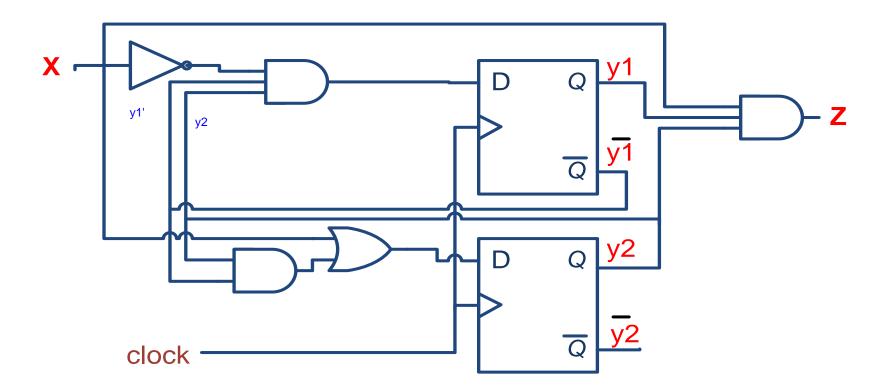

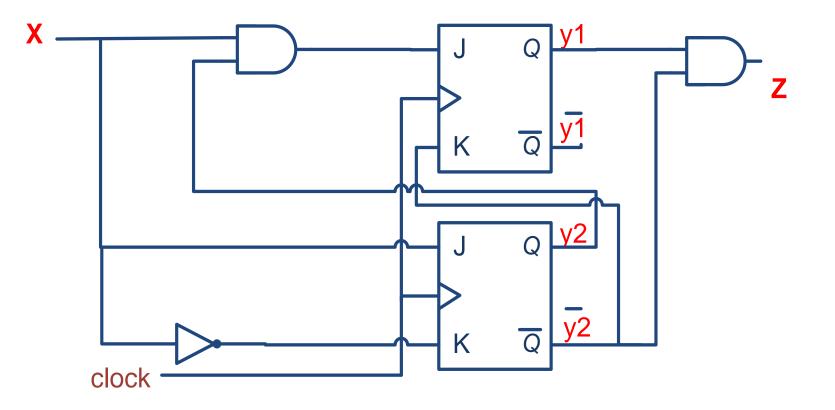

### Example 9-2/p515

• Analyze the synchronous Mealy machine in Figure below to obtain its state diagram.

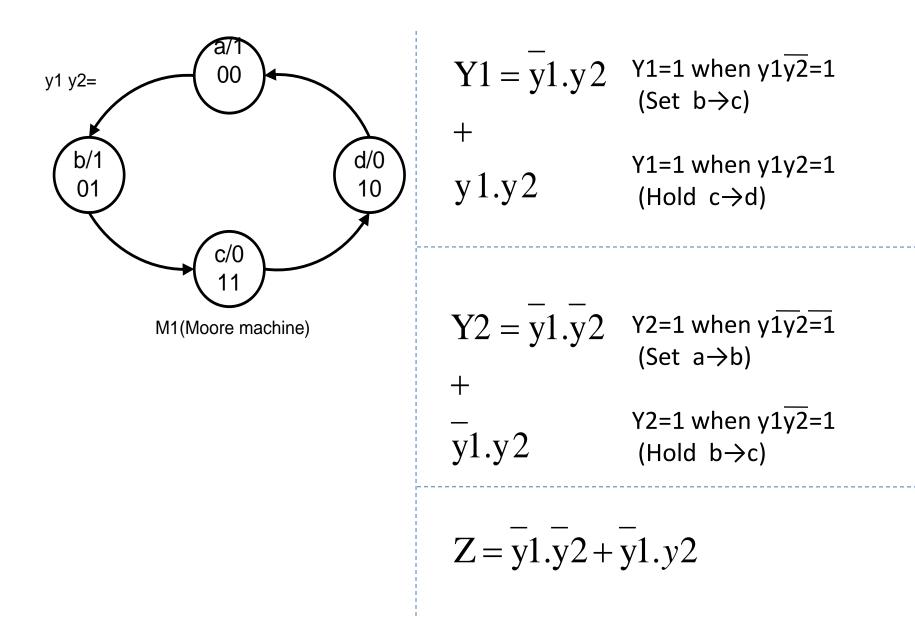

## Example 9-3/p517

Analyze the synchronous Moore machine in Figure below to obtain its state diagram.

#### Solution:-

$$Y = Q = q \cdot K + q \cdot J$$

$$J1 = y2 \cdot X$$

$$Y1 = y1 \cdot \overline{K1} + \overline{y1} \cdot J1 = y1 \cdot y2 + \overline{y1} \cdot y2 \cdot X$$

$$K1 = \overline{y2}$$

$$J2=X$$

$$Y2 = y2 \cdot \overline{K2} + \overline{y2} \cdot J2 = y2 \cdot X + \overline{y2} \cdot X = X$$

$$K2 = \overline{X}$$

$Z = y1 \cdot \overline{y2}$

#### Example 9-3

#### Example 9-3

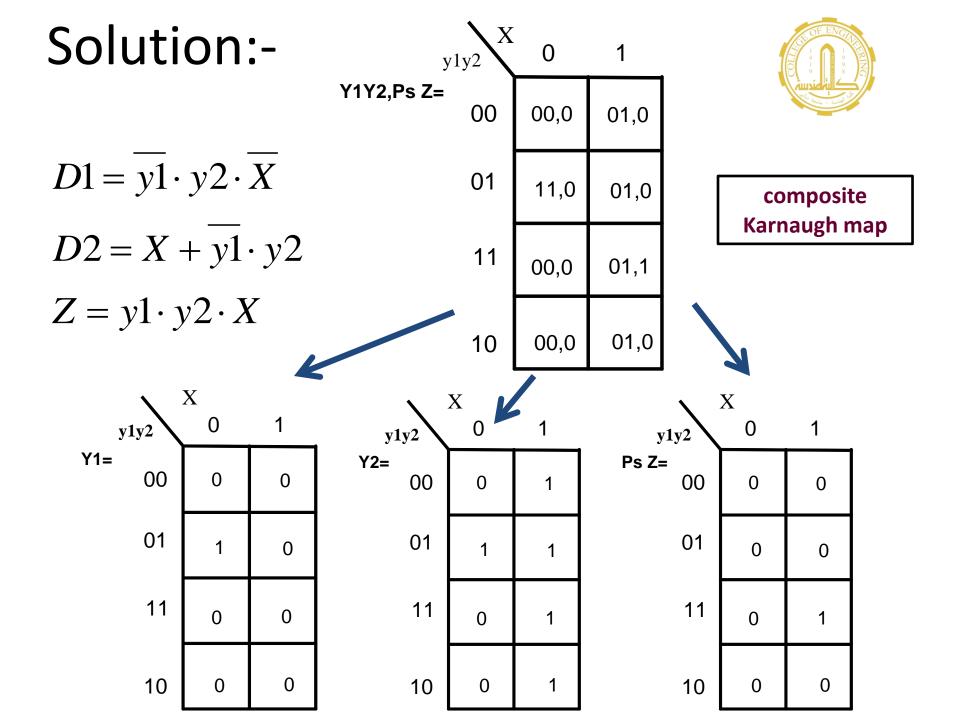

#### **State Machine Analysis Example**

Analyze the state machine:

This is a Mealy Machine since output = G(current state, input)

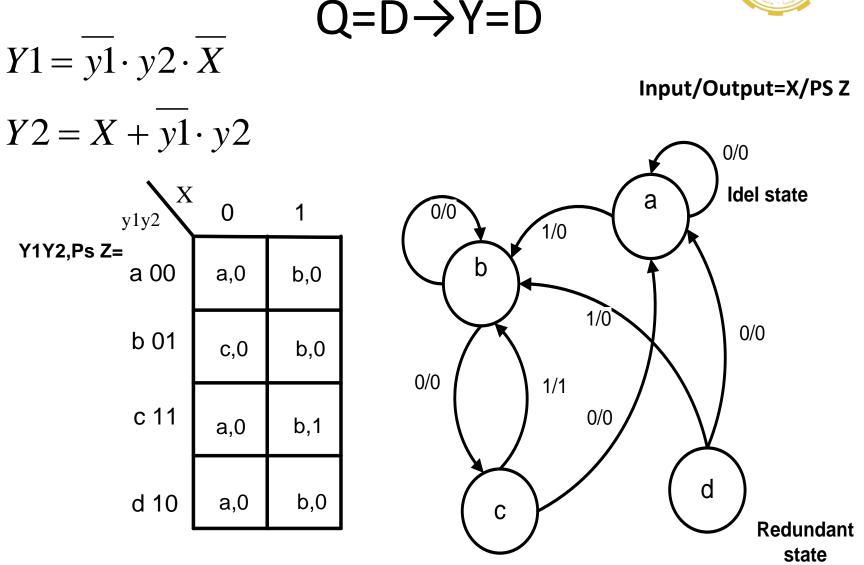

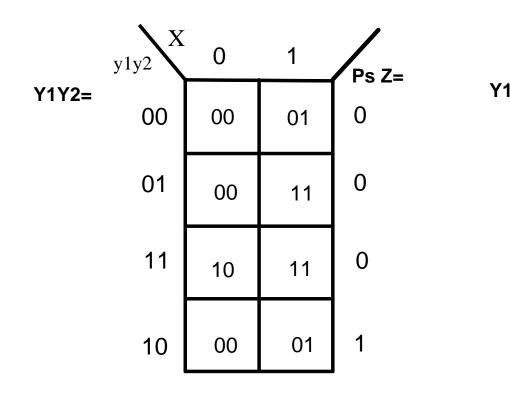

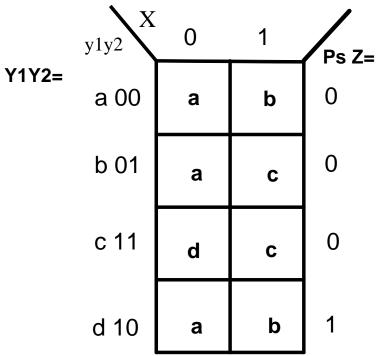

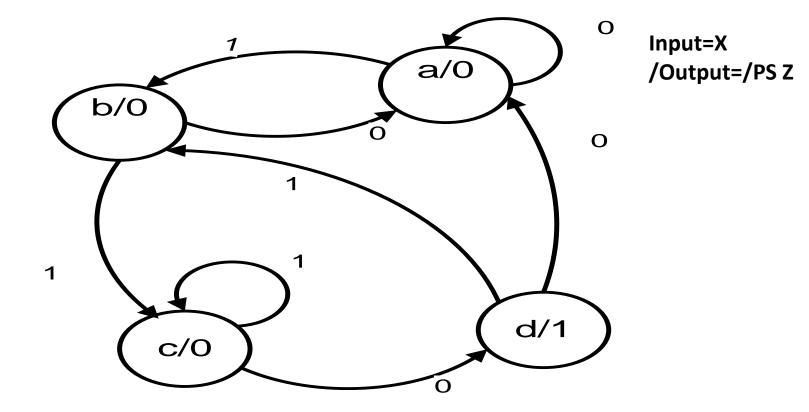

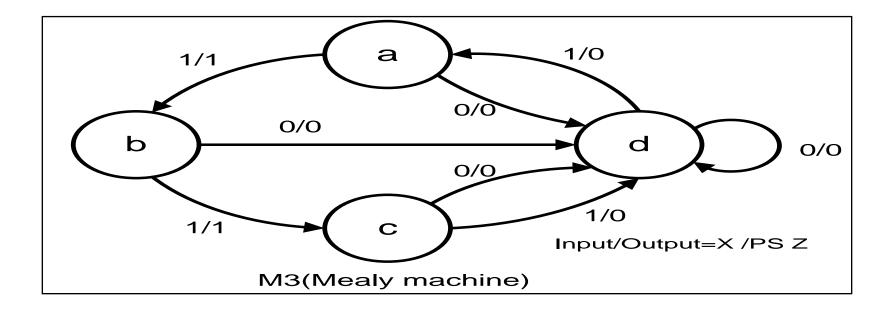

## Example 9-4/P521

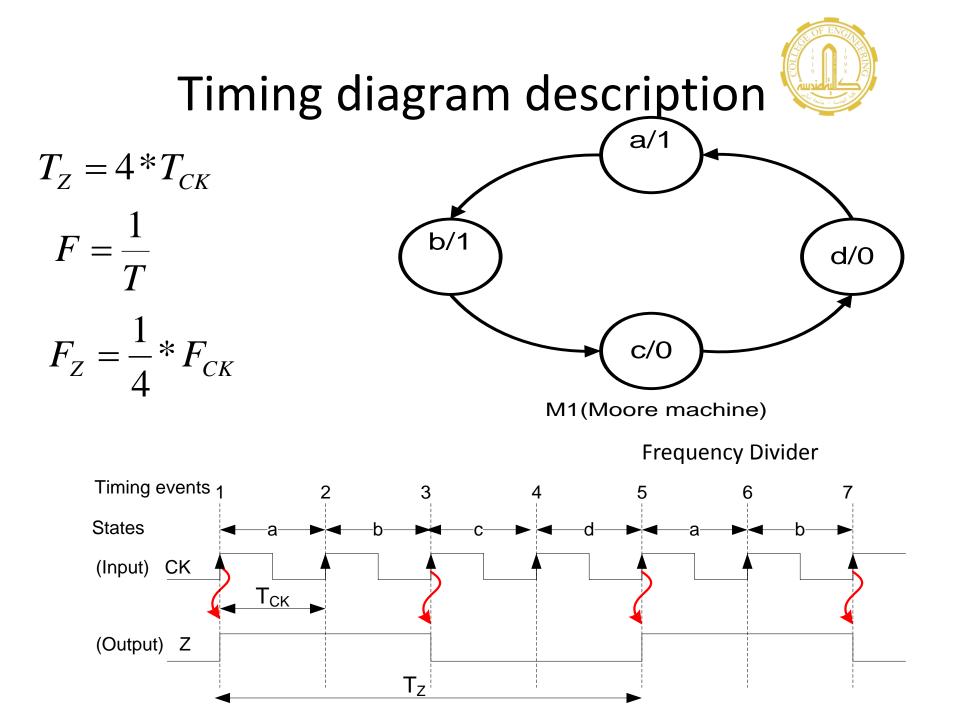

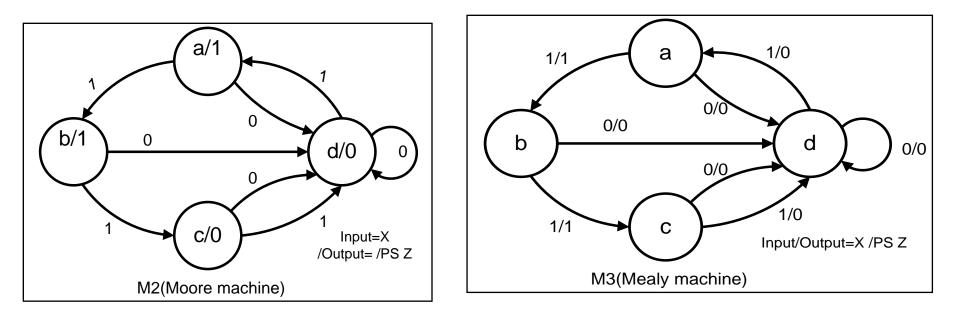

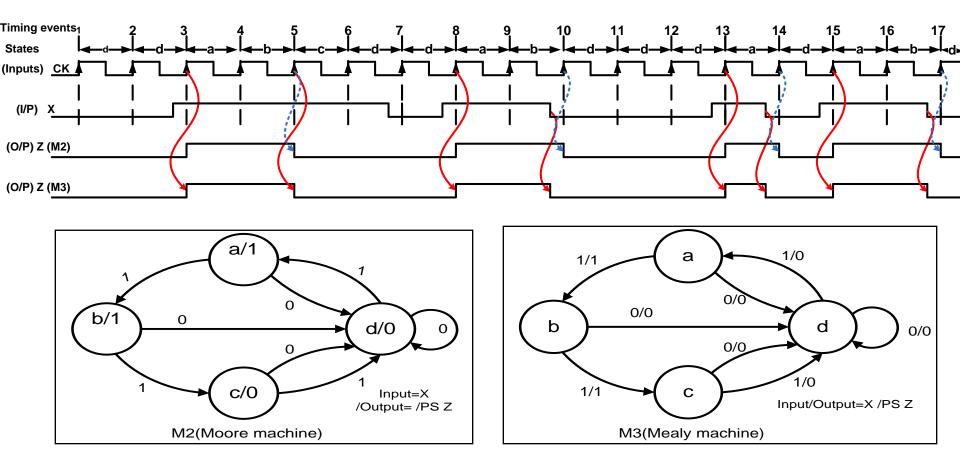

For both synchronous machines M2 and M3 we have one external input X. When the external input is 1, each provides an output signal Z is ¼ the frequency of the system clock signal, just like M1 in the timing diagram. When x is 0 on the next clock timing event, both M2 and M3 go to state d (an idle or reset state). both M2 and M3 stay in the idle state until X is 1 on the next clock timing event, allowing both machines to move to state a.

#### Example 9-4

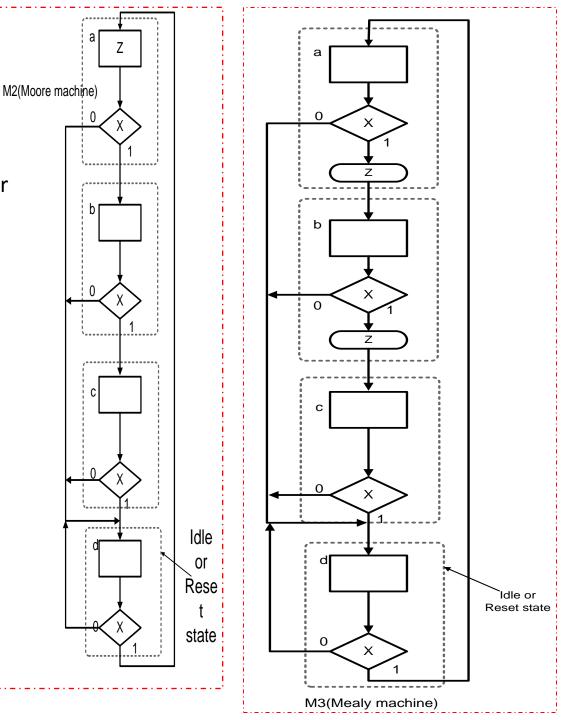

(a-) Draw an equivalent ASM chart for a Moore and Mealy machine for M2 and M3.

### Example 9-4

(b-) Draw a timing diagram for both M2 and M3 machine for the input sequence 00111101100010110 where the MSB in the binary number represent the first value of X in the sequence. Show the change in the asynchronous input X occurring approximately  $\frac{1}{4}$  of a cycle prior to the next clock timing event. Assume that output Z is initially o and the machine is in the idle state .

# D Flip-Flop Design procedure

- 1-General Method (composite Karnaugh map.)

- 2- Set or Hold Method

## 1-General Method (composite Karnaugh map.)

### 2- Set or Hold Method

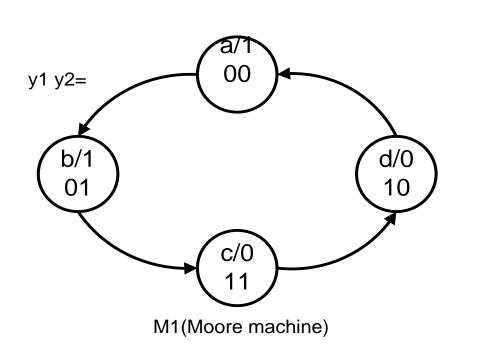

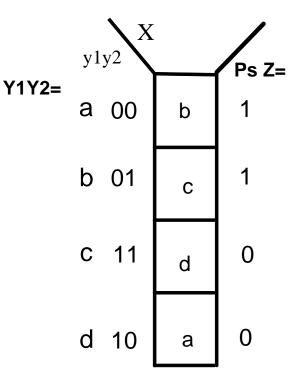

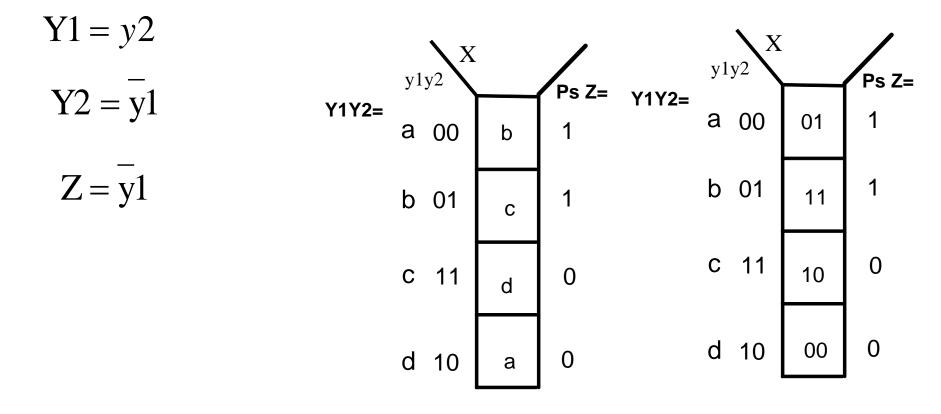

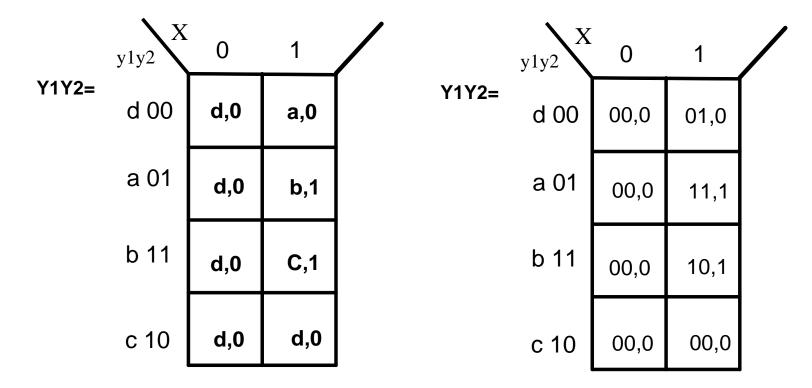

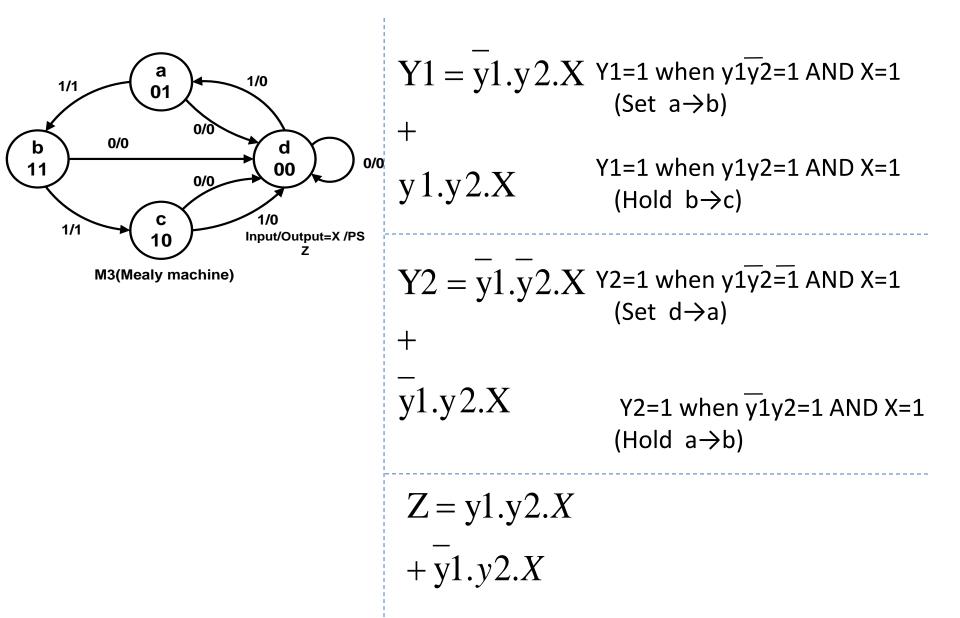

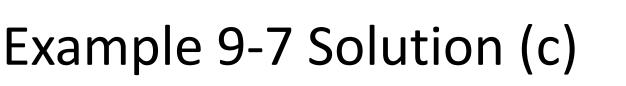

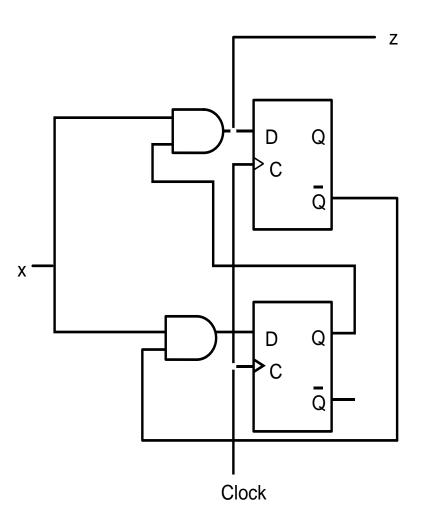

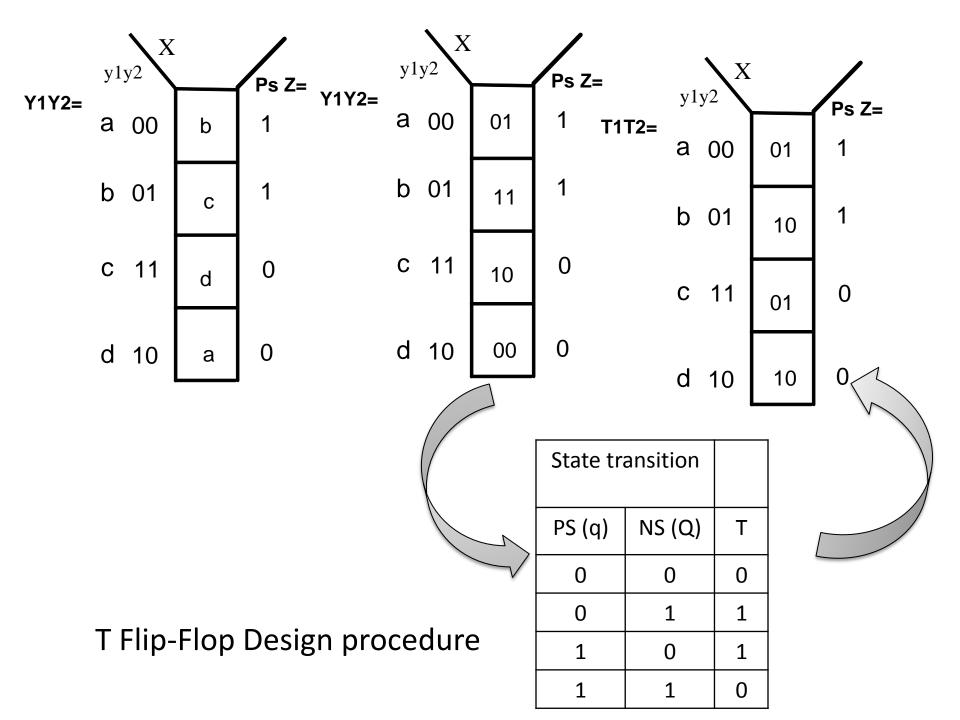

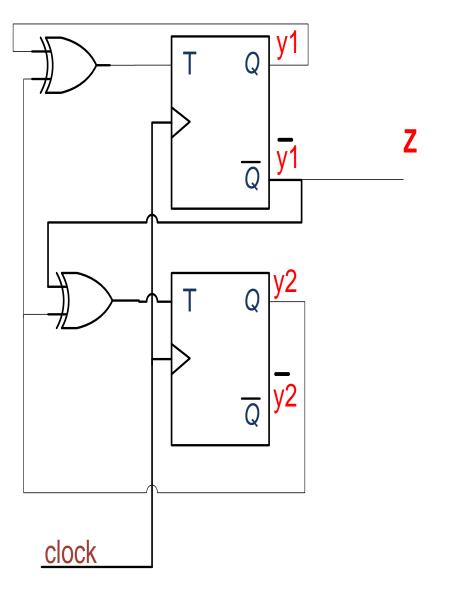

## Example 9-7/P531

Obtain the synchronous circuit equation for M3. Use the following state assignments y1y2=00 for d, 01 for a, 11 for b 10 for c).

- (a) Using a composite Karnaugh map.

- (b) Using Set or Hold method.

- (c) Use the reduced equation to obtain a circuit diagram using positive edgetriggered D flip-flops.

### Example 9-7 Solution (a)

Y1 = y2.X $Y2 = \overline{y1.X}$

Z = y2.X

## Example 9-7 Solution (b)

D1 = Y1 = y2.XD2 = Y2 = y1.X

$$Z = y2.X$$

#### $T1 = y1 \oplus y2$ $T2 = y1 \otimes y2 = \overline{y1} \oplus y2$ $Z = \overline{y1}$

## Example 9-9/p539

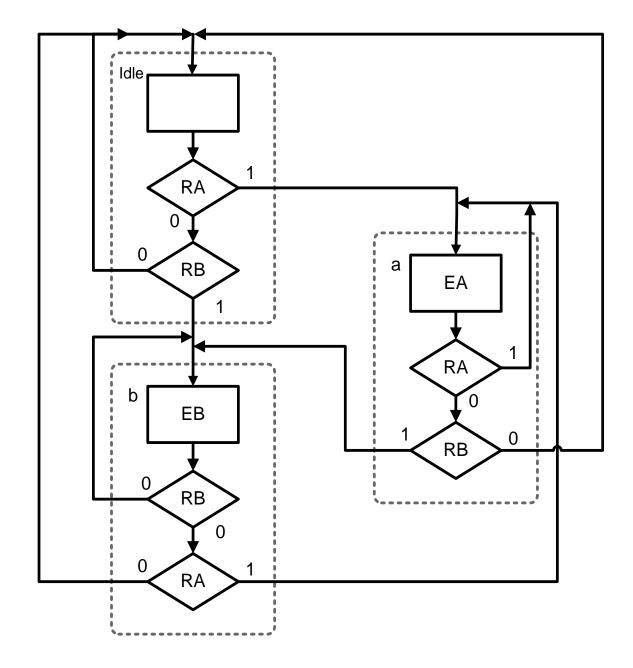

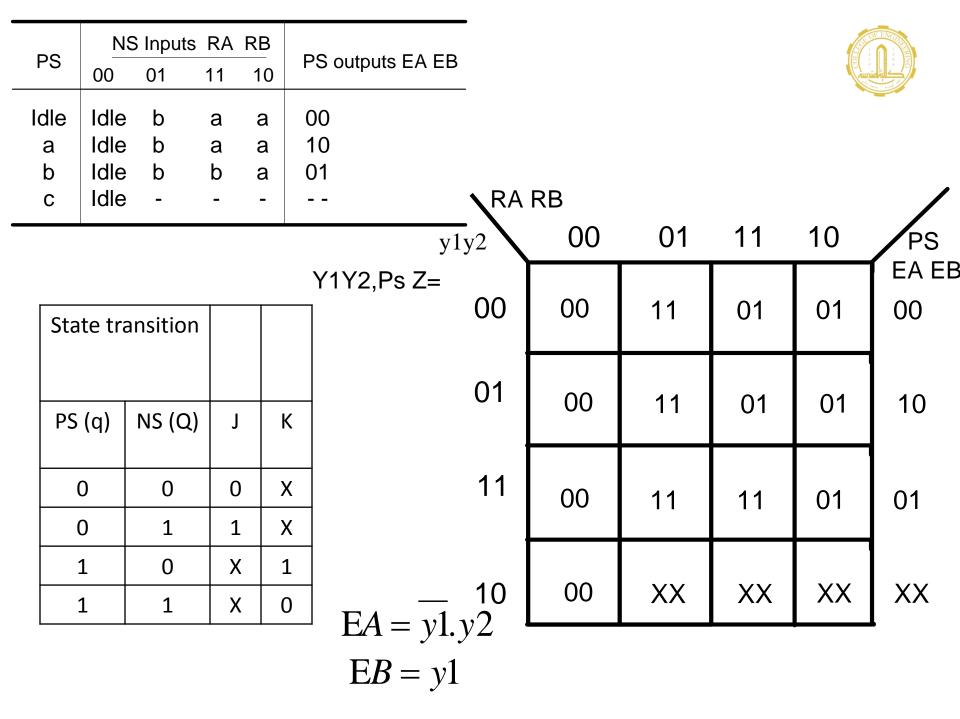

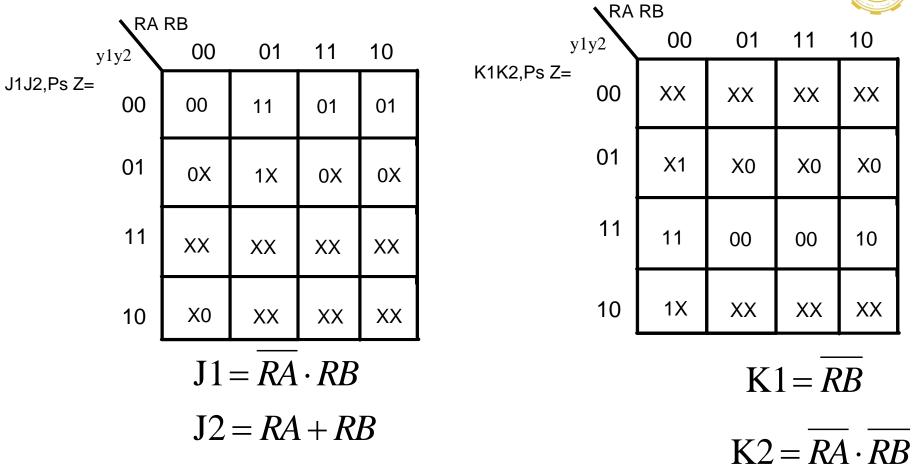

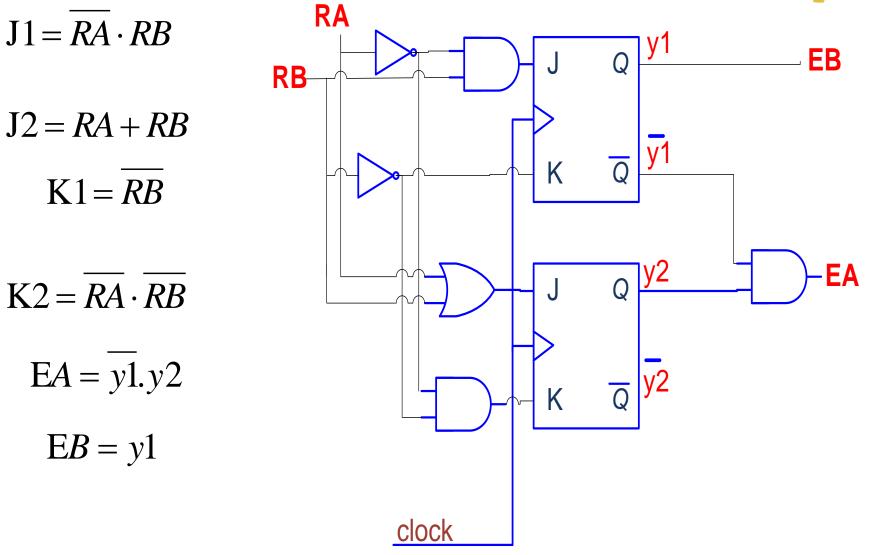

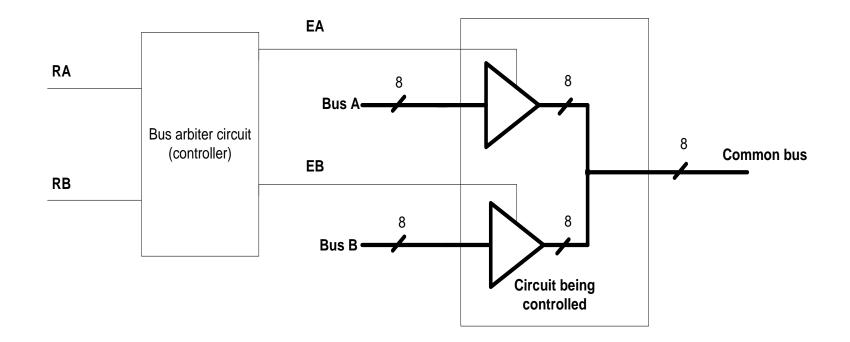

- RA RB represent bus request A and request B (input signal).

- EA EB represent bus enable A and enable B (output signal).

## Example 9-9/p539 Cont.

- Design bus arbiter circuit so the it behaves as following manner:

- 1-For the inputs RA RB=00 the circuit either goes to 'idle' state (outputs EA EB=00 disabling both bus A and B buffers), or remains in the 'idle' state.

- 2- When inputs RA RB change to 10 or 11 the circuit goes to 'a' state (outputs EA EB=10 enabling bus A and disabling bus B buffers).

- 3- When inputs RA RB change to 01 in the idle state, the circuit goes to 'b' state (outputs EA EB=01 disabling bus A and enabling bus B buffers)

- 4-To go from state 'a' to state 'b' requires inputs RA RB=01

- 5- To go from state 'b' to state 'a' requires inputs RA RB=10