University Of Diyala College Of Engineering Department of Computer Engineering

1

## Digital System Design II Microprogramming II-Part2

Dr. Yasir Al-Zubaidi Third stage 2021

- Instructions are stored in RAM or ROM as a program, the addresses for instructions are provided by a program counter (PC)

- Count up or load a new address

- The PC and associated control logic are part of the Control Unit

- A typical instruction specifies:

- Operands to use

- Operation to be performed

- Where to place the result, or which instruction to execute next

- Executing an instruction

- Activate the necessary sequence of operations specified by the instruction

- Be controlled by the control unit and performed in:

- datapath

- control unit

- external hardware such as memory or input/output

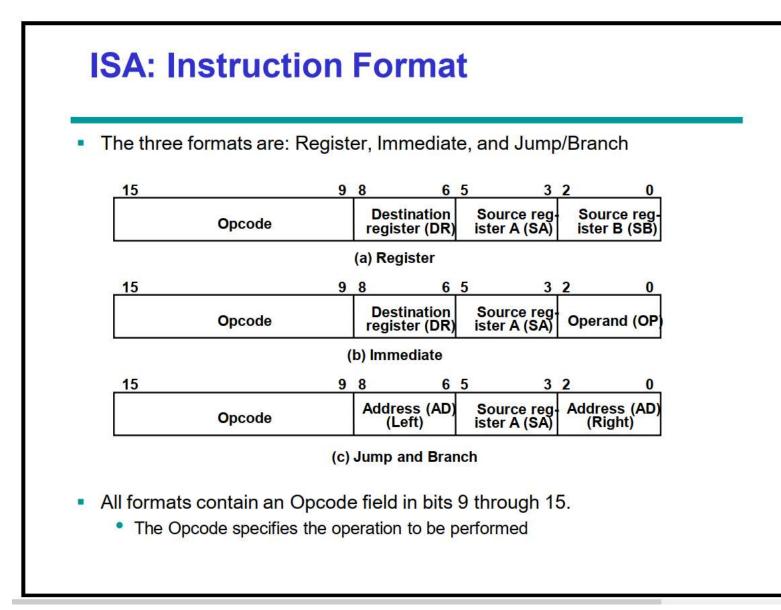

| 15 |        | 9 | 8 6                    | 5 3                         | 2 0                     |

|----|--------|---|------------------------|-----------------------------|-------------------------|

|    | Opcode |   | Address (AD)<br>(Left) | Source reg-<br>ister A (SA) | Address (AD)<br>(Right) |

- This instruction supports changes in the sequence of instruction execution by adding an extended, 6-bit, signed 2's-complement address offset to the PC value

- The SA field: permits jumps and branches on N or Z based on the contents of Source register A

- The Address (AD) field (6-bit) replaces the DR and SB fields

- Example: Suppose that a jump for the Opcode and the PC contains 45 (0...0101101) and AD contains – 12 (110100). Then the new PC value will be:

0...0101101 + (1...110100) = 0...0100001 (i.e., 45 + (-12) = 33)

| ISA: Inst<br>Instruction | Opcode  | Mnemonic | Format   | Description                              | Status<br>Bits |

|--------------------------|---------|----------|----------|------------------------------------------|----------------|

| Move A                   | 0000000 | MOVA     | RD,RA    | $R[DR] \leftarrow R[SA]$                 | N, Z           |

| Increment                | 0000001 | INC      | RD,RA    | $R[DR] \leftarrow R[SA] + 1$             | N, Z           |

| Add                      | 0000010 | ADD      | RD,RA,RB | $R[DR] \leftarrow R[SA] + R[SB]$         | N, Z           |

| Subtract                 | 0000101 | SUB      | RD,RA,RB | $R[DR] \leftarrow R[SA] - R[SB]$         | N, Z           |

| Decrement                | 0000110 | DEC      | RD,RA    | $R[DR] \leftarrow R[SA] - 1$             | N, Z           |

| AND                      | 0001000 | AND      | RD,RA,RB | $R[DR] \leftarrow R[SA] \land R[SB]$     | N, Z           |

| OR                       | 0001001 | OR       | RD,RA,RB | $R[DR] \leftarrow R[SA] \lor R[SB]$      | N, Z           |

| Exclusive OR             | 0001010 | XOR      | RD,RA,RB | $R[DR] \leftarrow R[SA] \oplus R[SB]$    | N, Z           |

| NOT                      | 0001011 | NOT      | RD,RA    | $R[DR] \leftarrow \overline{R[SA]}$      | N, Z           |

| Move B                   | 0001100 | MOVB     | RD,RB    | $R[DR] \leftarrow R[SB]$                 |                |

| Shift Right              | 0001101 | SHR      | RD,RB    | $R[DR] \leftarrow sr R[SB]$              |                |

| Shift Left               | 0001110 | SHL      | RD,RB    | $R[DR] \leftarrow sl R[SB]$              |                |

| Load Immediate           | 1001100 | LDI      | RD, OP   | $R[DR] \leftarrow zf OP$                 |                |

| Add Immediate            | 1000010 | ADI      | RD,RA,OP | $R[DR] \leftarrow R[SA] + zf OP$         |                |

| Load                     | 0010000 | LD       | RD,RA    | $R[DR] \leftarrow M[R[SA]]$              |                |

| Store                    | 0100000 | ST       | RA,RB    | $M[R[SA]] \leftarrow R[SB]$              |                |

| Branch on Zero           | 1100000 | BRZ      | RA,AD    | if $(R[SA] = 0) PC \leftarrow PC + se A$ | D              |

| Branch on Negative       | 1100001 | BRN      | RA,AD    | if $(R[SA] < 0) PC \leftarrow PC + se A$ | D              |

| Jump                     | 1110000 | JMP      | RA       | $PC \leftarrow R[SA]$                    |                |

# ISA:Example Instructions and Data in Memory

#### Memory Representation of Instruction and Data

| Decimal<br>Ad dress | Memory Contents     | Decimal<br>Opcode                   | Other Field            | Operation                  |  |  |

|---------------------|---------------------|-------------------------------------|------------------------|----------------------------|--|--|

| 25                  | 0000101 001 010 011 | 5 (Subtract)                        | DR:1, SA:2, SB:3       | R1 ← R2 - R3               |  |  |

| 35                  | 0100000 000 100 101 | 32 (Store)                          | SA:4, SB:5             | M[ R4] ← R5                |  |  |

| 45                  | 1000010 010 111 011 | <mark>66</mark> (Add<br>Im mediate) | DR: 2, SA :7, OP :3    | R2 ← R7 +3                 |  |  |

| 55                  | 1100000 101 110 100 | 96 (Branch<br>on Zero)              | AD: 44, SA:6           | lf R6 = 0,<br>PC ← PC - 20 |  |  |

| 70                  | 0000000 00110 0 000 | Data = 192. A<br>Data = 80.         | After execution of ins | truction in 35,            |  |  |

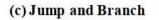

## **The Control Unit**

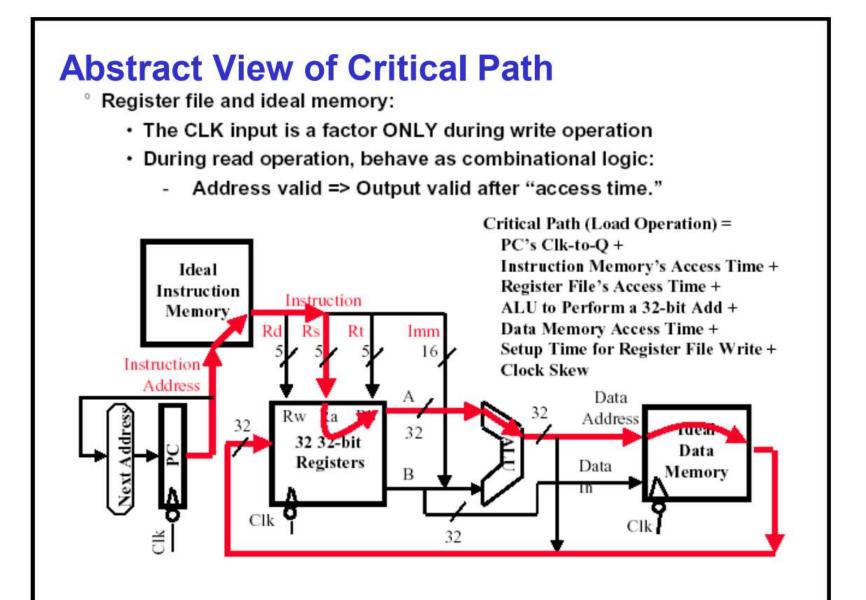

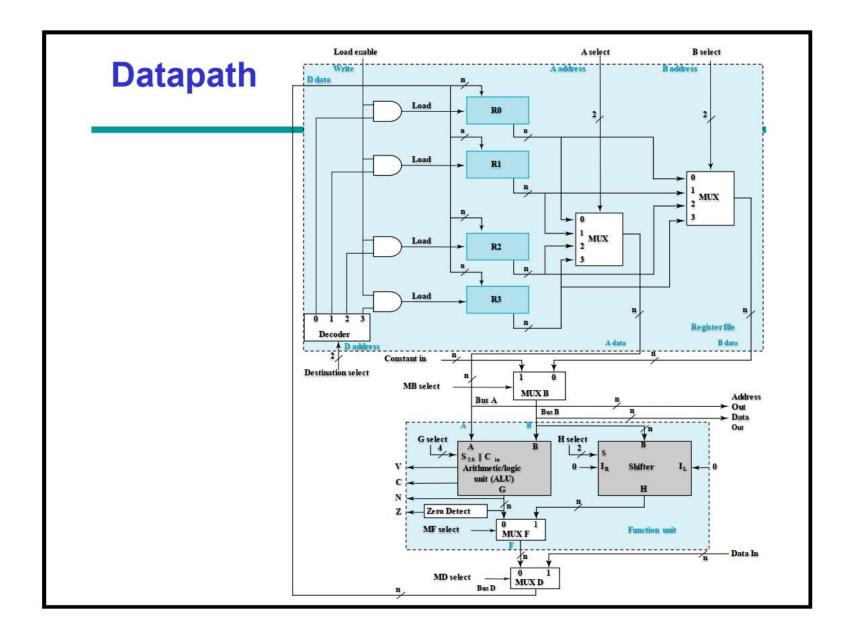

Datapath: the Data Memory has been attached to the Address Out, Data Out, and Data In lines of the Datapath.

#### Control Unit:

- The MW input to the Data Memory is the Memory Write signal from the Control Unit.

- The Instruction Memory address input is provided by the PC and its instruction output feeds the Instruction Decoder.

- Zero-filled IR(2:0) becomes Constant In

- Extended IR(8:6) || IR(2:0) and Bus A are address inputs to the PC.

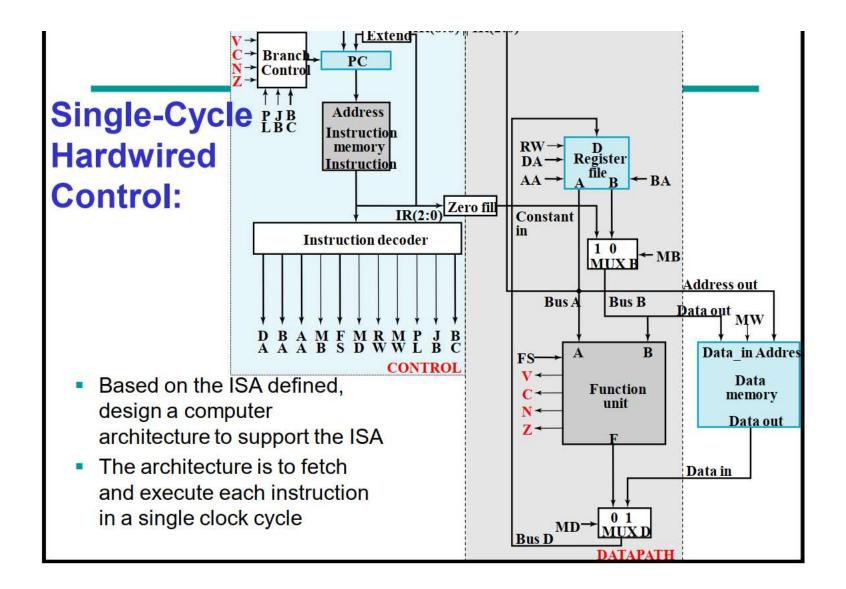

- The PC is controlled by Branch Control logic

PC function is based on instruction specifications involving jumps and branches:

| Branch on Zero     | BRZ | if (R[SA] = 0) PC $\leftarrow$ | PC + se A D |

|--------------------|-----|--------------------------------|-------------|

| Branch on Negative | BRN | if (R[SA] < 0) PC ←            | PC + se A D |

| Jump               | JMP | PC ← R[SA]                     |             |

- The first two transfers require addition to the PC of:

- Address Offset = Extended IR(8:6) || IR(2:0)

- The third transfer requires that the PC be loaded with:

- Jump Address = Bus A = R[SA]

- In addition to the above register transfers, the PC must implement the counting function:

• PC ← PC + 1

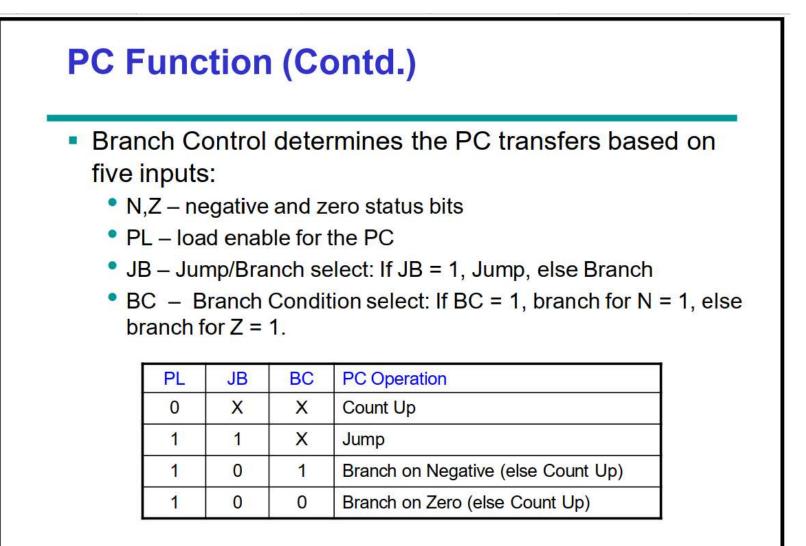

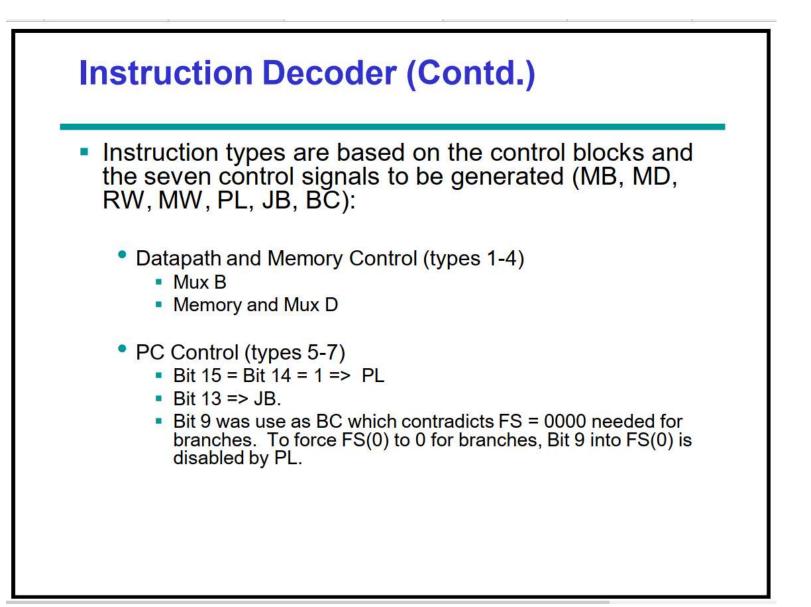

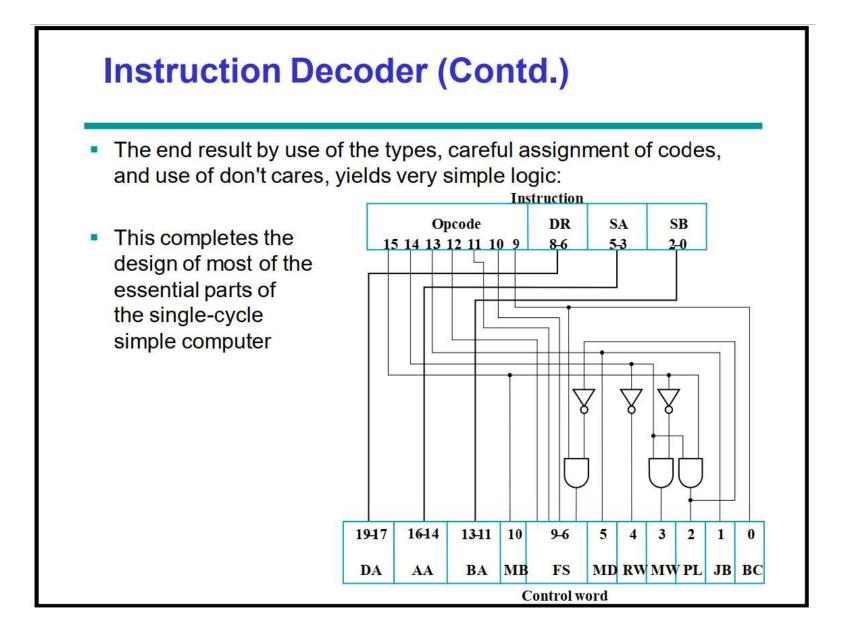

## **Instruction Decoder (Contd.)**

#### **Truth Table for Instruction Decoder Logic**

|                                                         | Instruction Bits |    |      |    | <b>Control Word Bits</b> |    |    |    |    |    |   |

|---------------------------------------------------------|------------------|----|------|----|--------------------------|----|----|----|----|----|---|

| Instruction Function Type                               | 15               | 14 | 13 9 | MB | MD                       | RW | MW | PL | JB | BC |   |

| 1. Function unit operations using registers             | 0                | 0  | 0    | X  | 0                        | 0  | 1  | 0  | 0  | X  | X |

| 2. Memory read                                          | 0                | 0  | 1    | X  | 0                        | 1  | 1  | 0  | 0  | X  | X |

| 3. Memory write                                         | 0                | 1  | 0    | X  | 0                        | X  | 0  | 1  | 0  | X  | X |

| 4. Function unit operations using register and constant | 1                | 0  | 0    | X  | 1                        | 0  | 1  | 0  | 0  | X  | X |

| 5. Conditional branch on zero (Z)                       | 1                | 1  | 0    | 0  | X                        | X  | 0  | 0  | 1  | 0  | 0 |

| 6. Conditional branch on negative                       | 1                | 1  | 0    | 1  | X                        | X  | 0  | 0  | 1  | 0  | 1 |

| (N)<br>7. Unconditional Jump                            | 1                | 1  | 1    | X  | X                        | X  | 0  | 0  | 1  | 1  | X |

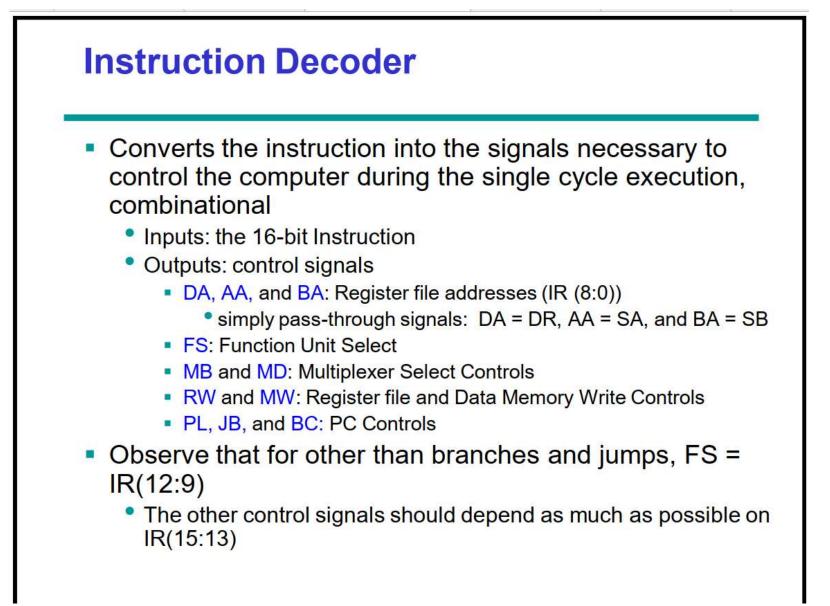

### **Example Instruction Execution**

Six Instructions for the Sirgle-Cycle Computer

| Operation | Symbo | ol ic       |                                           |                                                                                                          |    |    |    |    |    |    |    |

|-----------|-------|-------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|

| code      | name  | Fo rma t    | Description                               | Func tion                                                                                                | MB | MD | RW | MW | PL | JB | BC |

| 1000 010  | ADI   | Imme diate  | A dd immediate<br>operand                 | $R[DR] \leftarrow R[SA] + zf I(2:0)$                                                                     | 1  | 0  | 1  | 0  | 0  | 0  | 0  |

| 0010 000  | LD    | Register    | Load mem ory<br>content in to<br>register | <i>R</i> [DR] ← <i>M I</i> <u>R</u> [SA]]                                                                | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| 0100 000  | ST    | Register    | Store re gister<br>conten t in<br>memory  | M[R [SA]] ← R[SB]                                                                                        | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

| 0001 110  | SL    | Register    | Shift left                                | R[DR] ← sl R [SE]                                                                                        | 0  | 0  | 1  | 0  | 0  | 1  | 0  |

| 0001 011  | NOT   | Register    | Comple ment register                      | $R[DR] \leftarrow \overline{R[SA]}$                                                                      | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| 1100 000  | BRZ   | Jump/Branch | If R [SA] = 0, bra<br>to PC + se AD       | Inch If R[ SA] = 0,<br><i>PC</i> ← <i>PC</i> + se <i>AD</i> ,<br>If R[S A] ≠ 0, <i>PC</i> ← <i>P</i> C + |    | 0  | 0  | 0  | 1  | 0  | 0  |

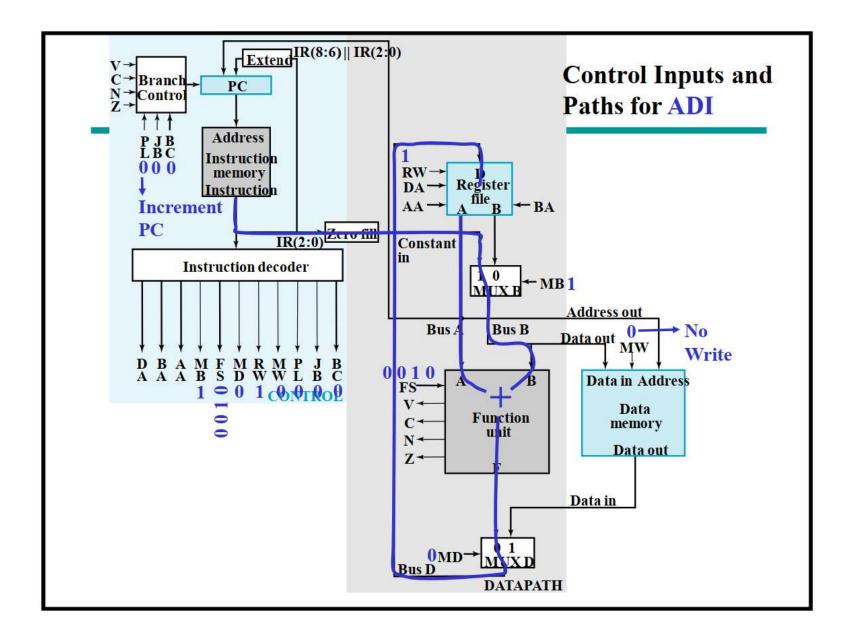

Decoding, control inputs and paths shown for ADI, LD and BRZ on next 6 slides

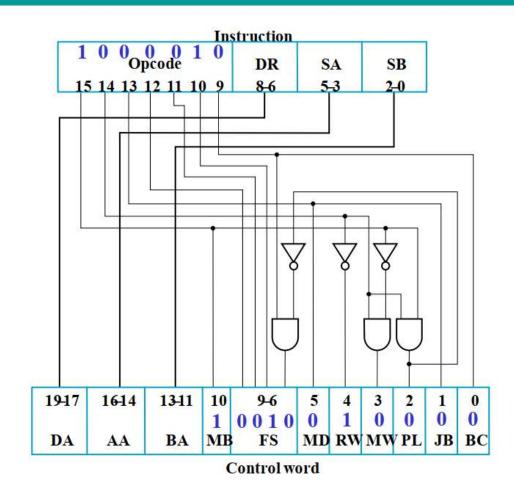

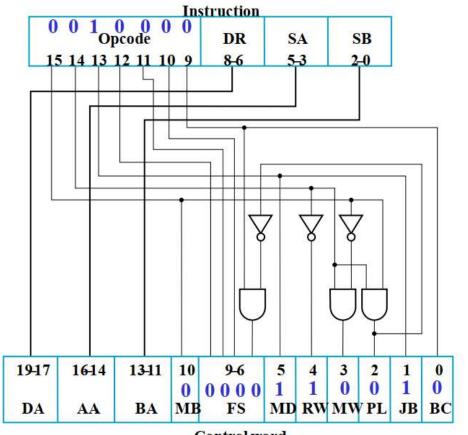

## **Decoding for ADI**

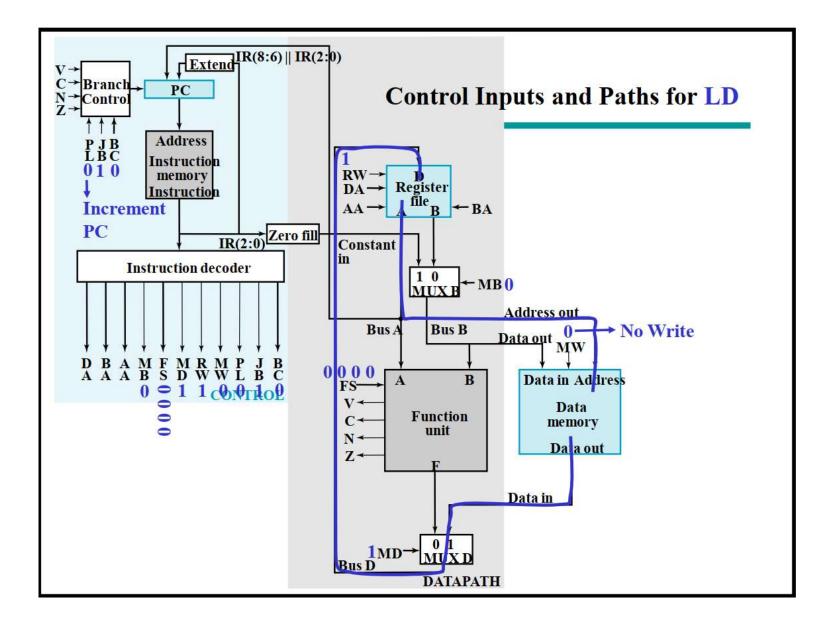

## **Decoding for LD**

**Control word**

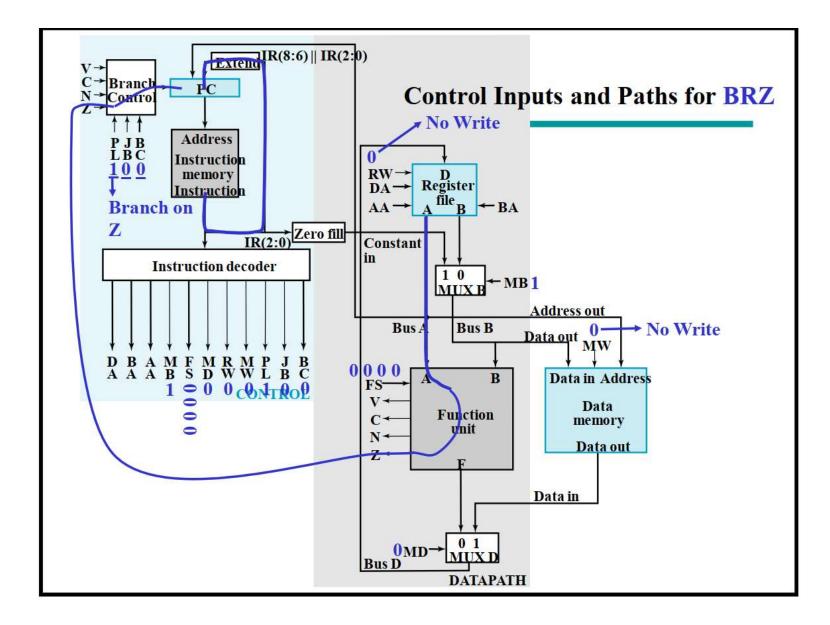

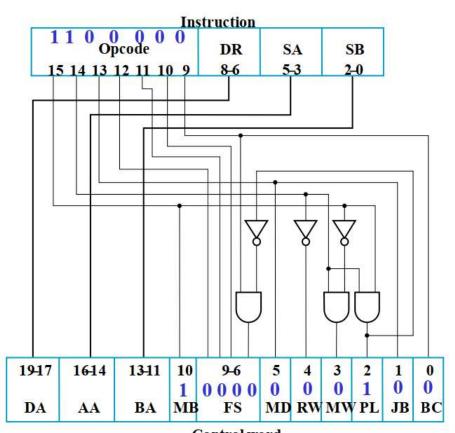

## **Decoding for BRZ**

**Control word**