University Of Diyala

College Of Engineering

Department of Computer Engineering

# Digital System Design II Asynchronous Sequential Logic Part II

Dr. Yasir Al-Zubaidi

Third stage

2021

#### Outline

- Asynchronous Sequential Circuits

- Analysis Procedure

- Circuits with Latches

- Design Procedure

- Reduction of State and Flow Tables

- Race-Free State Assignment

- Hazards

- Design Example

## Design Procedure

- 1. Obtain a primitive flow table from the given design specifications

- 2. Reduce the flow table by merging rows in the primitive flow table

- 3. Assign binary state variables to each row of the reduced flow to obtain the transition table.

- 4. Assign output values to the dashes associated with the unstable states to obtain the output map.

- 5. Simplify the Boolean functions of the excitation and output variables and draw the logic diagram

#### Primitive Flow Table

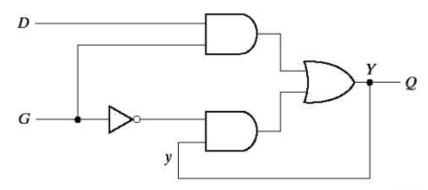

- Design example: gated latch

- Two Input (G = gate, D = Data).

- One output is Q, the gated latch is a memory element that;

- Accept the value of D when G=1

- Retain this value after G goes to 0 (D has no effects now)

- Obtain the flow table by listing all possible states.

- Dash marks are given when both inputs change simultaneously

- Outputs of unstable states are don't care

|             | In       | put | Output |                     |

|-------------|----------|-----|--------|---------------------|

| State D G Q | Comments |     |        |                     |

| a           | 0        | 1   | 0      | D=Q because G=1     |

| b           | 1        | 1   | 1      | D=Q because G=1     |

| С           | 0        | 0   | 0      | After states a or d |

| d           | 1        | 0   | 0      | After state c       |

| е           | 1        | 0   | 1      | After states b or f |

| f           | 0        | 0   | 1      | After state e       |

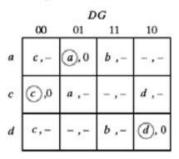

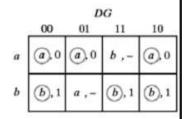

|   |                | D      | G                              |               |

|---|----------------|--------|--------------------------------|---------------|

|   | 00             | 01     | 11                             | 10            |

| а | c,-            | (a), 0 | b ,-                           | -,-           |

| b | -,-            | a ,-   | <b>(</b> <i>b</i> <b>)</b> , 1 | e,-           |

| с | ⓒ,0            | a ,-   | -,-                            | d ,-          |

| d | c,-            | -,-    | b ,-                           | <b>(d</b> ),0 |

| e | f,-            | -,-    | b ,-                           | (e), 1        |

| f | <b>(f)</b> , 1 | a ,-   | -,-                            | e ,-          |

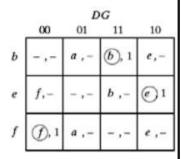

#### **Reduce the Flow Table**

- Two or more rows can be merged into one row if there are non-conflicting states and outputs in every columns

- After merged into one row:

- Don't care entries are overwritten

- Stable states and output values are included

- A common symbol is given to the merged row

- Formal reduction procedure is given in next section

(a) States that are candidates for merging

(b) Reduced table (two alternatives)

(a)

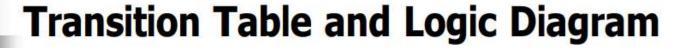

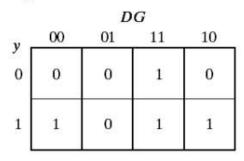

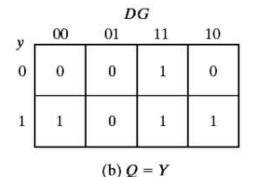

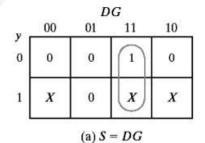

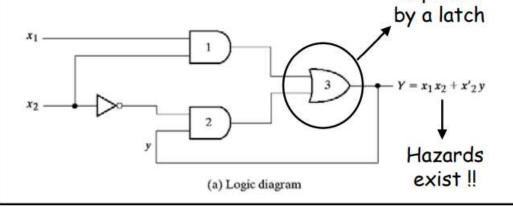

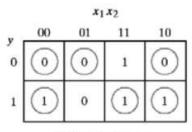

$$Y = DG + G'y$$

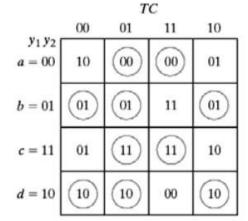

- Assign a binary value to each state to generate the transition table

- a=0, b=1 in this example

- Directly use the simplified Boolean function for the excitation variable Y

- An asynchronous circuit without latch is produced

01

DG

11

10

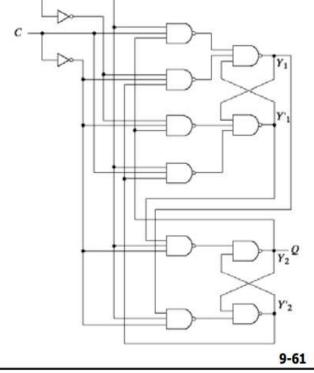

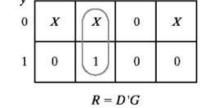

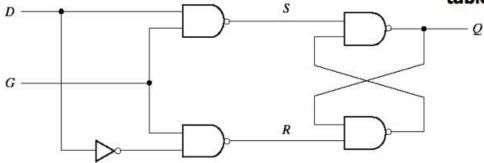

(a) Maps for S and R

Listed according to the transition table and the excitation table of SR latch

(b) Logic diagram

## **Outputs for Unstable States**

- Objective: no momentary false outputs occur when the circuit switches between stable states

- If the output value is not changed, the intermediate unstable state must have the same output value

- $0 \rightarrow 1$  (unstable)  $0 \rightarrow 0$  (X)

- $\bullet$  0  $\rightarrow$  0 (unstable)  $\rightarrow$  0 (0)

- If the output value changed, the intermediate outputs are don't care

- It makes no difference when the output change occurs

| (a) | F | ow | ta | ы | ( |

|-----|---|----|----|---|---|

| 0 | (0) |

|---|-----|

| X | 0   |

| 1 | (1) |

| X | 1   |

(b) Output assignment

#### Outline

- Asynchronous Sequential Circuits

- Analysis Procedure

- Circuits with Latches

- Design Procedure

- Reduction of State and Flow Tables

- Race-Free State Assignment

- Hazards

- Design Example

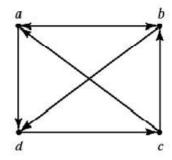

## **State Reduction**

Two states are equivalent if they have the same output and go to the same (equivalent) next states for each possible input

Ex: (a,b) are equivalent

(c,d) are equivalent

State reduction procedure is similar in both sync. & async. sequential circuits

| Present | Next | State | Out | put |

|---------|------|-------|-----|-----|

| State   | x=0  | x=1   | x=0 | x=1 |

| а       | С    | b     | 0   | 1   |

| b       | d    | а     | 0   | 1   |

| С       | a    | d     | 1   | 0   |

| d       | b    | d     | 1   | 0   |

- For completely specified state tables:

- → use implication table

- For incompletely specified state tables:

- → use compatible pairs

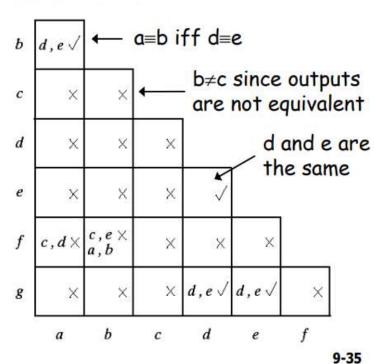

## **Implication Table Method (1/2)**

#### Step 1: build the implication chart

| <b>Present</b> | Next | State | Out | put |

|----------------|------|-------|-----|-----|

| State          | x=0  | x=1   | x=0 | x=1 |

| a              | d    | b     | 0   | 0   |

| b              | е    | а     | 0   | 0   |

| С              | g    | f     | 0   | 1   |

| d              | а    | d     | 1   | 0   |

| е              | a    | d     | 1   | 0   |

| f              | С    | b     | 0   | 0   |

| g              | а    | е     | 1   | 0   |

## **Implication Table Method (2/2)**

- Step 2: delete the node with unsatisfied conditions

- Step 3: repeat Step 2 until equivalent states found

| equivalent     | states :   |

|----------------|------------|

| (a,b) (d,e) (d | d,g) (e,g) |

| d ==           | e == g     |

| <b>Present</b> | <b>Next State</b> |     | Output |     |

|----------------|-------------------|-----|--------|-----|

| State          | x=0               | x=1 | x=0    | x=1 |

| a              | d                 | а   | 0      | 0   |

| C              | d                 | f   | 0      | 1   |

| d              | a                 | d   | 1      | 0   |

| f              | С                 | a   | 0      | 0   |

\*Reduced State Table\*

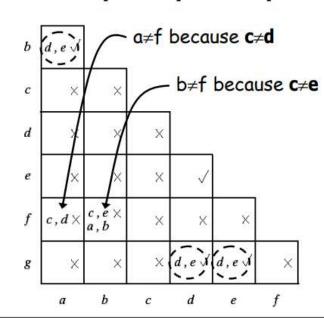

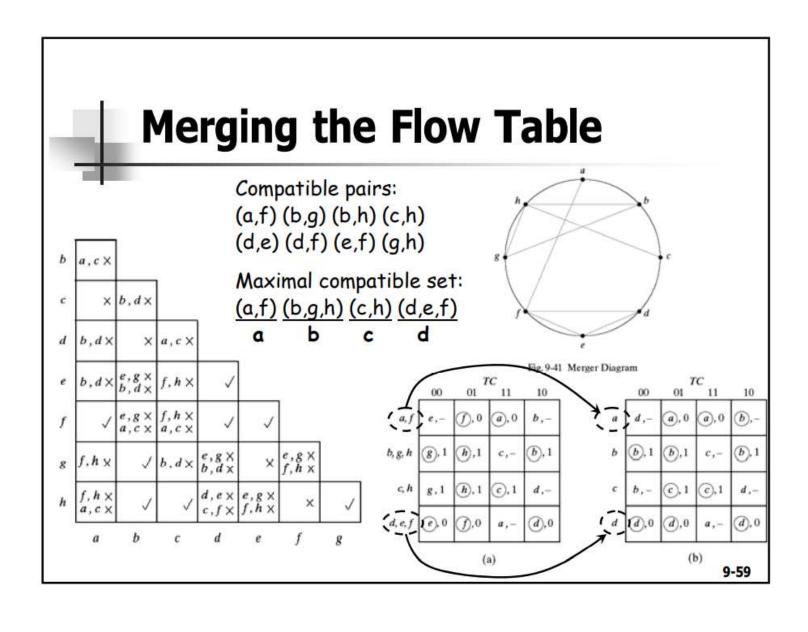

#### **Merge the Flow Table**

- The state table may be incompletely specified

- Some next states and outputs are don't care

- Primitive flow tables are always incompletely specified

- Several synchronous circuits also have this property

- Incompletely specified states are not "equivalent"

- Instead, we are going to find "compatible" states

- Two states are compatible if they have the same output and compatible next states whenever specified

- Three procedural steps:

- Determine all compatible pairs

- Find the maximal compatibles

- Find a minimal closed collection of compatibles

- Implication tables are used to find compatible states

- We can adjust the dashes to fit any desired condition

- Must have no conflict in the output values to be merged

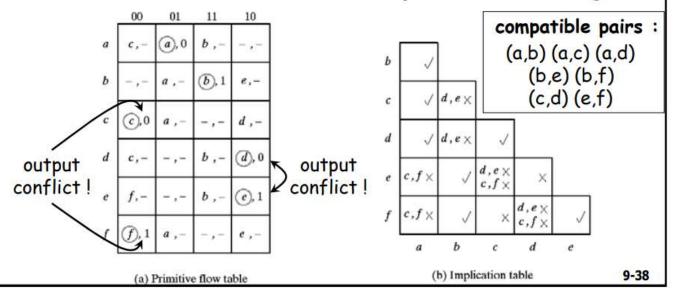

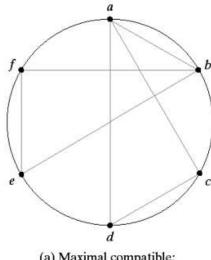

## **Maximal Compatibles**

- A group of compatibles that contains all the possible combinations of compatible states

- Obtained from a merger diagram

- A line in the diagram represents that two states are compatible

- n-state compatible → n-sided fully connected polygon

All its diagonals connected

Not all maximal compatibles are necessary

(a,b,)(a,c,d)(b,e,f)

(a, b, e, f) (b, c, h) (c, d) (g)

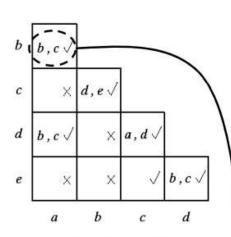

## **Closed Covering Condition**

- The set of chosen compatibles must cover all the states and must be closed

- Closed covering

- The closure condition is satisfied if

- There are no implied states

- The implied states are included within the set

- Ex: if remove (a,b) in the right

- (a,c,d) (b,e,f) are left in the set

- All six states are still included

- No implied states according to its implication table 9-23(b)

(a) Maximal compatible: (a, b,) (a, c, d) (b, e, f)

## **Closed Covering Example**

Compatibles (a, b) (a, d) (b, c) (c, d, e)Implied states (b, c) (b, c) (d, e) (a, d, b) (b, c, c)

(c) Closure table

(b) Merger diagram

\*(a,b) (c,d,e) → (X) implied (b,c) is not included in the set

\* better choice:

(a,d) (b,c) (c,d,e)

all implied states

are included 9-41

#### Outline

- Asynchronous Sequential Circuits

- Analysis Procedure

- Circuits with Latches

- Design Procedure

- Reduction of State and Flow Tables

- Race-Free State Assignment

- Hazards

- Design Example

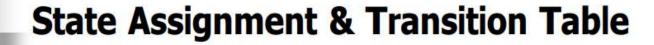

- Objective: choose a proper binary state assignment to prevent critical races

- Only one variable can change at any given time when a state transition occurs

- States between which transitions occur will be given adjacent assignments

- Two binary values are said to be adjacent if they differ in only one variable

- To ensure that a transition table has no critical races, every possible state transition should be checked

- A tedious work when the flow table is large

- Only 3-row and 4-row examples are demonstrated

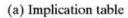

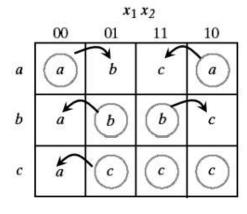

## 3-Row Flow Table Example (1/2)

- Three states require two binary variables

- Outputs are omitted for simplicity

- Adjacent info. are represented by a transition diagram

- a and c are still not adjacent in such an assignment !!

- Impossible to make all states adjacent if only 3 states are used

a = 00 b = 01---- b has a transition to c c = 11

(a) Flow table

(b) Transition diagram

- A race-free assignment can be obtained if we add an extra row to the flow table

- Only provide a race-free transition between the stable states

- The transition from a to c must now go through d

- $00 \rightarrow 10 \rightarrow 11$  (no race condition)

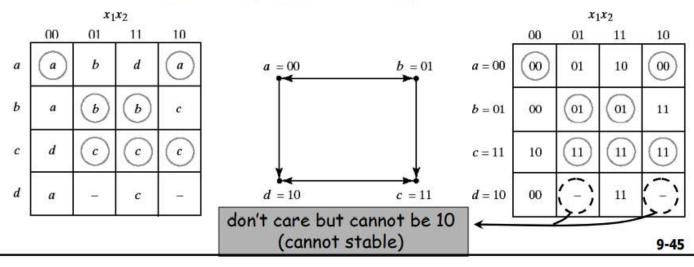

### 4-Row Flow Table Example (1/2)

- Sometimes, just one extra row may not be sufficient to prevent critical races

- More binary state variables may also required

- With one or two diagonal transitions, there is no way of using two binary variables that satisfy all adjacency

(b) Transition diagram

## 4-Row Flow Table Example (2/2)

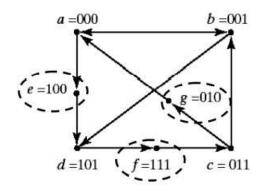

101 = d

100 = e

(a) Binary assignment

(b) Transition diagram

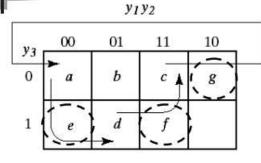

|         | 00       | 01  | 11                | 10  |

|---------|----------|-----|-------------------|-----|

| 000 = a | ь        | a   | e                 |     |

| 001 = b | <b>b</b> | d   | <b>b</b>          | а   |

| 011 = c | C        | g   | ь                 | C   |

| 010 = g | -        | а   | 1                 | J   |

| 110 –   |          | - T | 9 <del>87</del> 9 | Tak |

| 111 = f | с        | ==  | -                 | с   |

|         |          |     | _                 |     |

d

still has only 4 stable states

## **Multiple-Row Method**

- Multiple-row method is easier

- May not as efficient as in above shared-row method

- Each stable state is duplicated with exactly the same output

- Behaviors are still the same

- While choosing the next states, choose the adjacent one

|               |                   | <i>y</i> <sub>2</sub> | <i>y</i> <sub>3</sub> |                       |

|---------------|-------------------|-----------------------|-----------------------|-----------------------|

|               | y <sub>1</sub> 00 | 01                    | 11                    | 10                    |

|               | $0  a_1$          | $b_1$                 | $c_1$                 | $d_1$                 |

| can be used < |                   |                       |                       |                       |

| o any 4-row   | 1 c <sub>2</sub>  | $d_2$                 | <i>a</i> <sub>2</sub> | <i>b</i> <sub>2</sub> |

| flow table    |                   |                       |                       |                       |

(a) Binary assignment

| 0 | $00 = a_1$       | $b_1$             |                       | $d_1$                 |                       |

|---|------------------|-------------------|-----------------------|-----------------------|-----------------------|

| 1 | $11 = a_2$       | b <sub>2</sub>    | (a <sub>2</sub> )     | <i>d</i> <sub>2</sub> | (a <sub>2</sub> )     |

| 0 | $01 = b_1$       | (b <sub>1</sub> ) | <i>d</i> <sub>2</sub> | $b_1$                 | <i>a</i> <sub>1</sub> |

| 1 | $10 = b_2$       | (b <sub>2</sub> ) | $d_1$                 | (b <sub>2</sub> )     | <i>a</i> <sub>2</sub> |

| 0 | $c_{11} = c_{1}$ | $c_1$             | <i>a</i> <sub>2</sub> | <i>b</i> <sub>1</sub> |                       |

| 1 | $00 = c_2$       | (c <sub>2</sub> ) | <i>a</i> <sub>1</sub> | <i>b</i> <sub>2</sub> | (c <sub>2</sub> )     |

| 0 | $10 = d_1$       | $c_1$             | $d_1$                 | $d_1$                 | $c_1$                 |

| 1 | $01 = d_2$       | c <sub>2</sub>    | $d_2$                 | $d_2$                 | $c_2$                 |

|   |                  |                   |                       |                       |                       |

(b) Flow table

#### Outline

- Asynchronous Sequential Circuits

- Analysis Procedure

- Circuits with Latches

- Design Procedure

- Reduction of State and Flow Tables

- Race-Free State Assignment

- Hazards

- Design Example

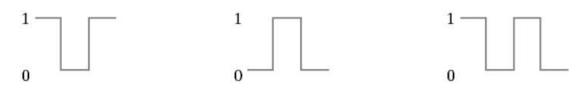

- Unwanted switching appears at the output of a circuit

- Due to different propagation delay in different paths

- May cause the circuit to mal-function

- Cause temporary false-output values in combinational circuits

- Cause a transition to a wrong state in asynchronous circuits

- Not a concern to synchronous sequential circuits

- Three types of hazards:

- (a) Static 1-hazard

- (b) Static 0-hazard

- (c) Dynamic hazard

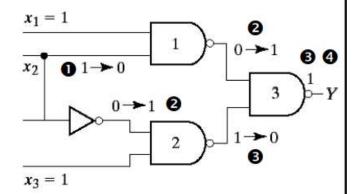

#### **Circuits with Hazards**

- Static hazard: a momentary output change when no output change should occur

- If implemented in sum of products:

- no static 1-hazard → no static 0-hazard or dynamic hazard

- Two examples for static 1-hazard:

(a) AND-OR circuit

(b) NAND circuit

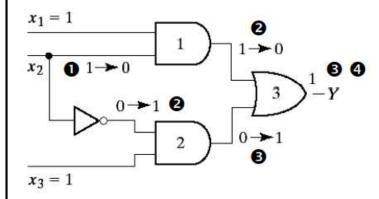

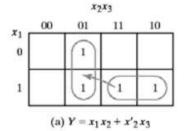

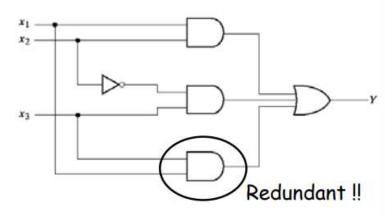

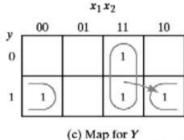

#### **Hazard-Free Circuit**

- Hazard can be detected by inspecting the map

- The change of input results in a change of covered product term

- → Hazard exists

- Ex: 111 → 101 in (a)

- To eliminate the hazard, enclose the two minterms in another product term

- Results in redundant gates

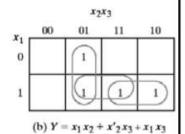

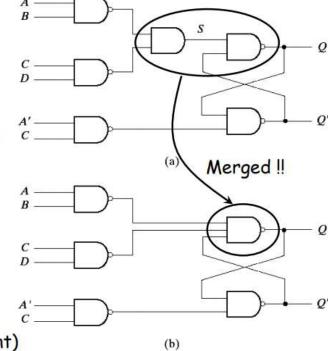

#### **Remove Hazard with Latches**

- Implement the asynchronous circuit with SR latches can also remove static hazards

- A momentary 0 has no effects to the S and R inputs of a NOR latch

- A momentary 1 has no effects to the S and R inputs of a NAND latch

Replaced

(b) Transition table

....

#### **Implementation with SR Latches**

$$S = AB + CD$$

$$R = A'C$$

For NAND latch, use complemented inputs

$$= [Q'(AB)'(CD)']'$$

→ Two-level circuits

(this is the output we want)

#### **Essential Hazards**

- Besides static and dynamic hazards, another type of hazard in asynchronous circuits is called essential hazard

- Caused by unequal delays along two or more paths that originate from the same input

- Cannot be corrected by adding redundant gates

- Can only be corrected by adjusting the amount of delay in the affected path

- Each feedback path should be examined carefully !!

#### Outline

- Asynchronous Sequential Circuits

- Analysis Procedure

- Circuits with Latches

- Design Procedure

- Reduction of State and Flow Tables

- Race-Free State Assignment

- Hazards

- Design Example

- 1. State the design specifications

- 2. Derive a primitive flow table

- 3. Reduce the flow table by merging the rows

- 4. Make a race-free binary state assignment

- 5. Obtain the transition table and output map

- 6. Obtain the logic diagram using SR latches

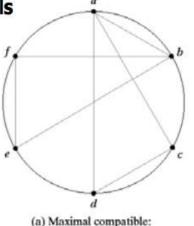

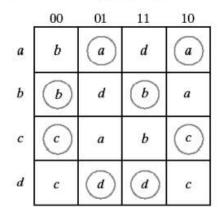

#### **Primitive Flow Table**

- Design a negative-edge-triggered

T flip-flop

- Two inputs: T(toggle) and C(clock)

- T=1: toggle, T=0: no change

- One output: Q

|       | In | put | Output |                     |

|-------|----|-----|--------|---------------------|

| State | T  | С   | Q      | Comments            |

| а     | 1  | 1   | 0      | Initial output is 0 |

| b     | 1  | 0   | 1      | After state a       |

| C     | 1  | 1   | 1      | Initial output is 1 |

| d     | 1  | 0   | 0      | After state c       |

| е     | 0  | 0   | 0      | After states d or f |

| f     | 0  | 1   | 0      | After states e or a |

| g     | 0  | 0   | 1      | After states b or h |

| h     | 0  | 1   | 1      | After states g or c |

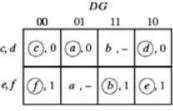

|   | TC             |                |              |                |  |

|---|----------------|----------------|--------------|----------------|--|

|   | 00             | 01             | 11           | 10             |  |

| a | -,-            | f ,-           | <b>a</b> , 0 | b ,-           |  |

| b | g ,-           | -,-            | c ,-         | <b>(b)</b> , 1 |  |

| с | -,-            | h ,-           | ©, 1         | d ,-           |  |

| d | e,-            | -,-            | a ,-         | <b>(d</b> ), 0 |  |

| e | @,0            | f ,-           | -,-          | d ,-           |  |

| ſ | e ,-           | <b>(</b> f), 0 | a ,-         | - ,-           |  |

| g | <b>(g</b> ), 1 | h ,-           | -,-          | b ,-           |  |

| h | g ,-           | (h), 1         | c ,-         | -,-            |  |

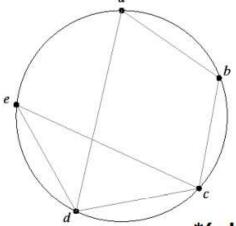

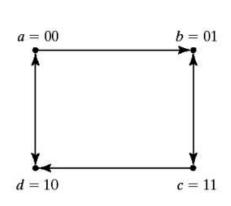

- No diagonal lines in the transition diagram

- → No need to add extra states

Fig. 9-43 Transition Diagram

(a) Transition table

| 10 |    |                            |                                     |

|----|----|----------------------------|-------------------------------------|

| 00 | 01 | 11                         | 10                                  |

| 0  | 0  | 0                          | х                                   |

| 1  | 1  | 1                          | 1                                   |

| 1  | 1  | 1                          | X                                   |

| 0  | 0  | 0                          | 0                                   |

|    | 1  | 00 01<br>0 0<br>1 1<br>1 1 | 00 01 11<br>0 0 0<br>1 1 1<br>1 1 1 |

TC

(b) Output map  $Q = y_2$

(a)

$$S_1 = y_2 TC + y'_2 T'C'$$

|        | TC |    |    |    |

|--------|----|----|----|----|

| y1y2 [ | 00 | 01 | 11 | 10 |

| 00     | 0  | X  | x  | X  |

| 01     | X  | Х  | 0  | Х  |

| 11     | 1  | 0  | 0  | 0  |

| 10     | 0  | 0  | 1  | 0  |

|        |    |    | _  |    |

(b)

$$R_1 = y_2 T'C' + y'_2 TC$$

|                   | TC |    |    |    |

|-------------------|----|----|----|----|

| y1y2 <sub>1</sub> | 00 | 01 | 11 | 10 |

| 00                | X  | X  | X  | 0  |

| 01                | 0  | 0  | 0  | 0  |

| 11                | 0  | 0  | 0  | 1  |

| 10                | X  | X  | х  | X  |