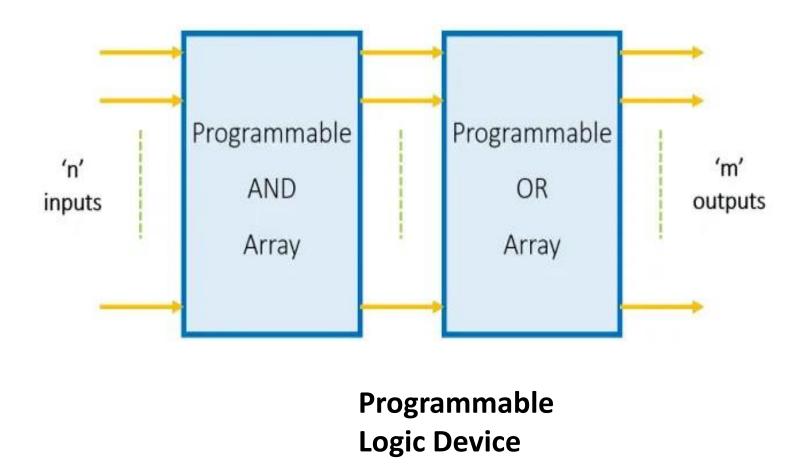

Programmable Logic Device PLD

#### PLD

An IC that contains large numbers of gates, flip-flops, etc. that can be configured by the user to perform different functions is called a Programmable Logic Device (PLD). It permits elaborate digital logic designs to be implemented by the user on a single device. The internal logic gates and/or connections of PLDs can be changed/configured by a programming process. On the other hand, Programmable Logic Devices (PLDs) are the components which do not have a specific function associated with them.

#### Definitions

Programmable Logic Device (PLD):

- Also known as "Field Programmable Logic Device (FPLD)"

- An integrated circuit chip that can be configured by the user to implement different digital hardware.

#### Advantages of PLDs

- Programmability

- Re-programmability

- PLDs can be reprogrammed without being removed from the circuit board.

- Low cost of design

- Immediate hardware implementation

#### PLD

- The purpose of a PLD device is to permit elaborate digital logic designs to be implemented by the user in a single device.

- Can be erased electrically and reprogrammed with a new design, making them very well suited for academic and prototyping

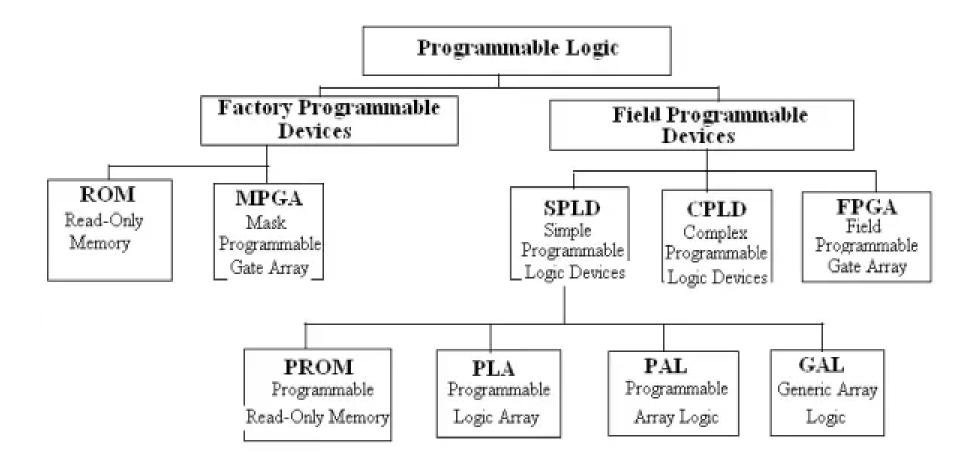

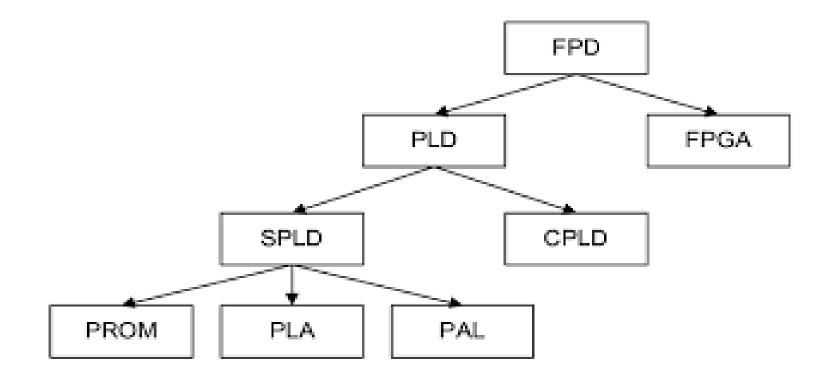

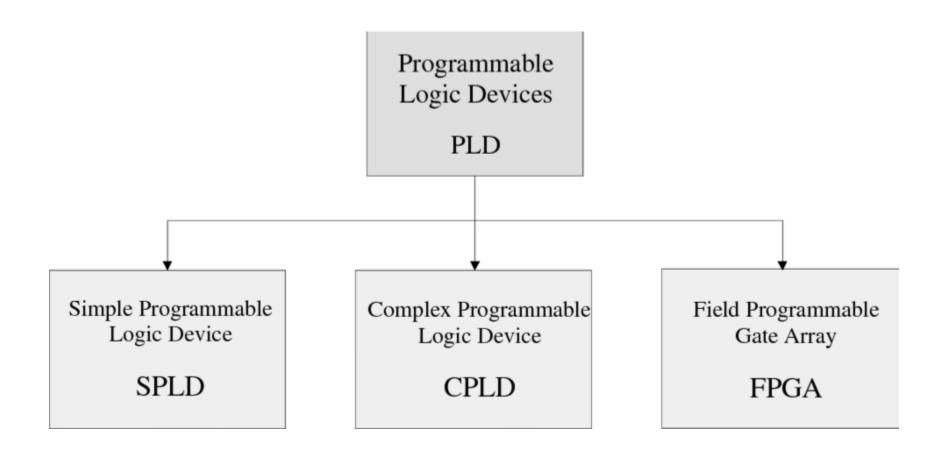

- Types of Programmable Logic Devices

- SPLDs (Simple Programmable Logic Devices)

- ROM (Read-Only Memory)

- PLA (Programmable Logic Array)

- PAL (Programmable Array Logic)

- GAL (Generic Array Logic)

- CPLD (Complex Programmable Logic Device)

- FPGA (Field-Programmable Gate Array)

$\checkmark$

#### Type of PLDs

- The three major types of programmable logic are :-

- 1) SPLD (Simple Programmable Logic devices)

- CPLD (Complex Programmable Logic Devices) and

- 3) FPGA (Field Programmable Gate Array).

#### PLDs

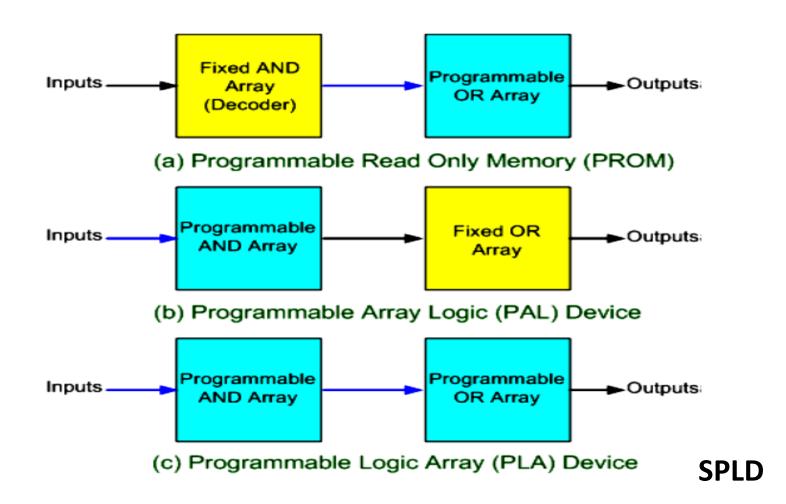

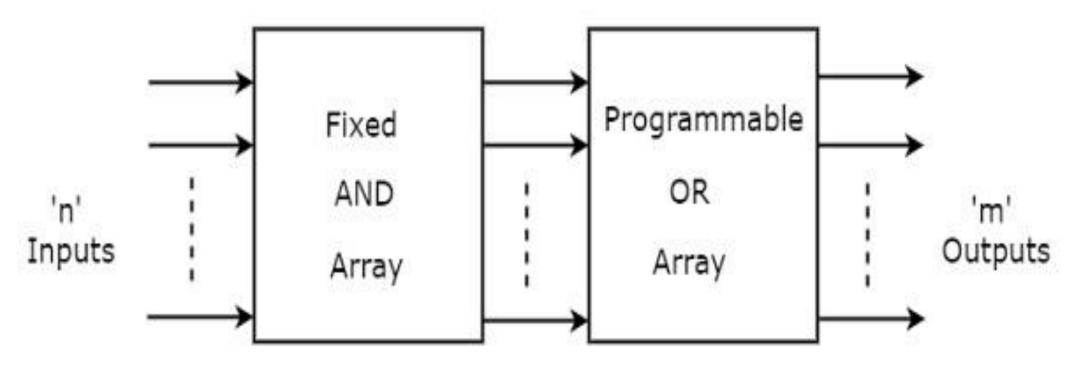

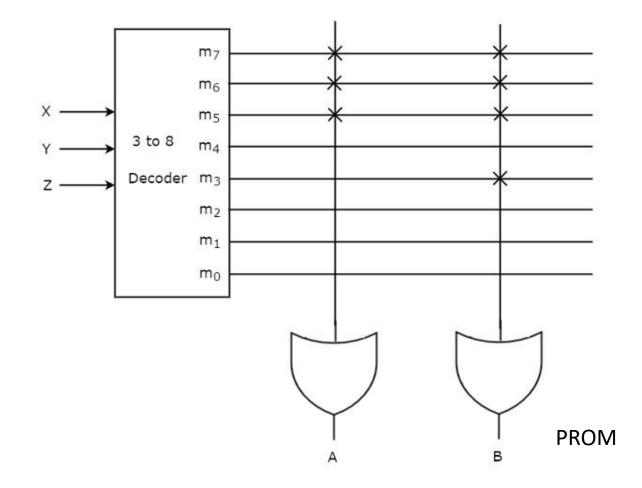

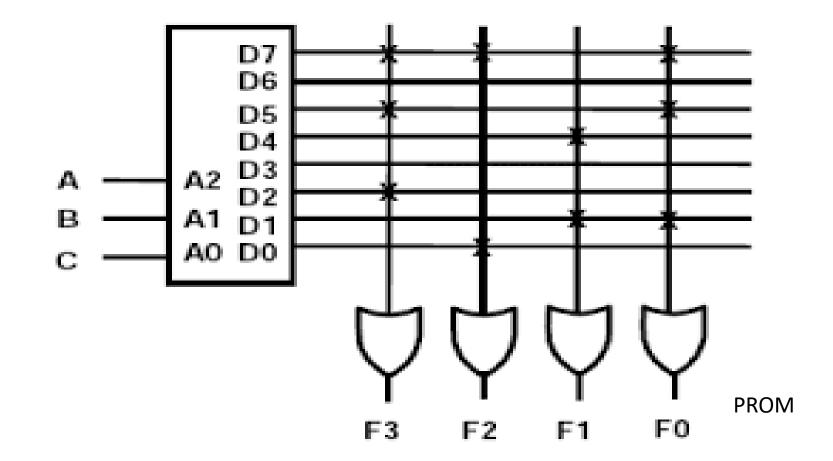

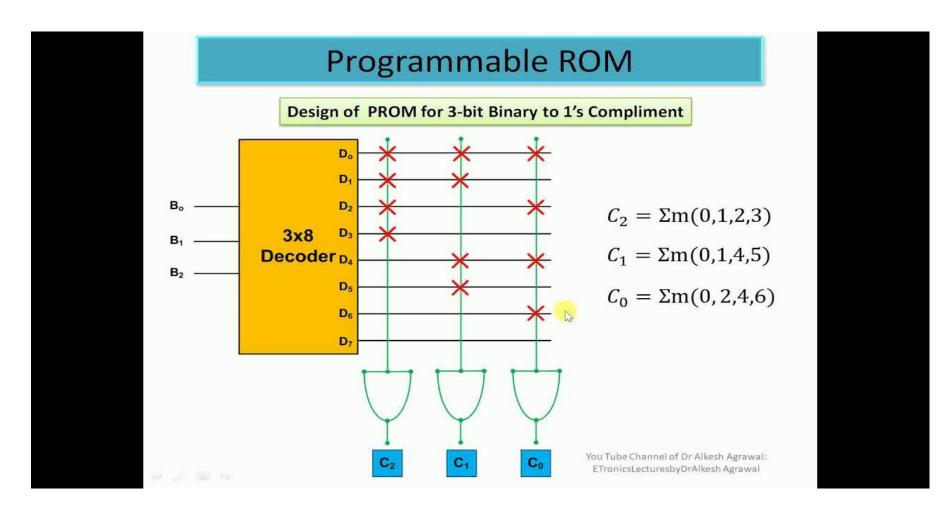

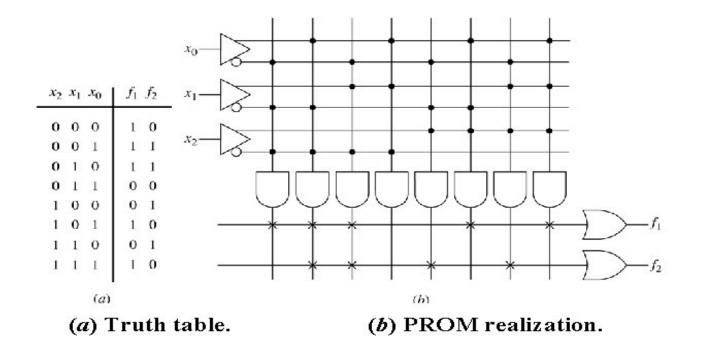

- ROM : Programmable OR array

- PLA : Programmable Logic Array . Programmable OR – AND arrays.

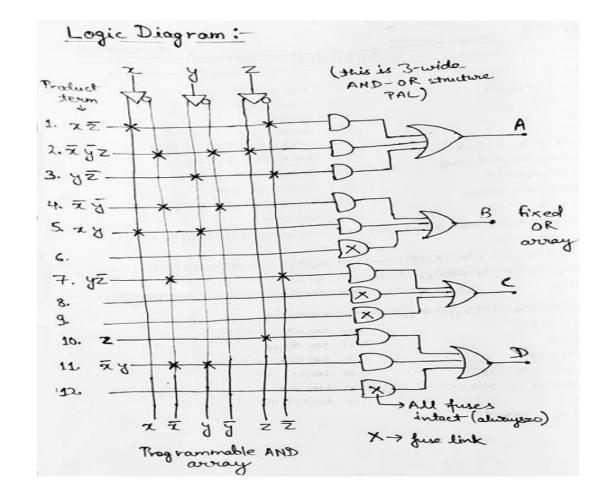

- PAL : Programmable Array Logic . Programmable AND array, fixed OR

- GAL : Generic Array Logic Can be configured to emulate many earlier PLDs including those with internal Flip-Flops

- CPLD : Complex PLD

- FPGA : Field Programmable Gate Arrays

#### Three FPLD Types

- Simple Programmable Logic Device (SPLD)

- LSI device

- Less than 1000 logic gates

- Complex Programmable Logic Device (CPLD)

- VLSI device

- Higher logic capacity than SPLDs

- Field Programmable Gate Array (FPGA)

- VLSI device

- Higher logic capacity than CPLDs

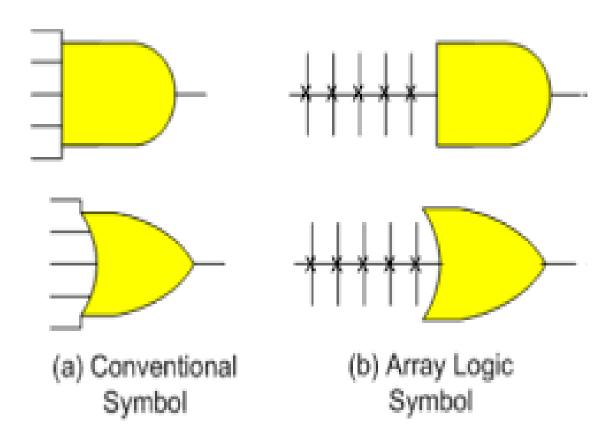

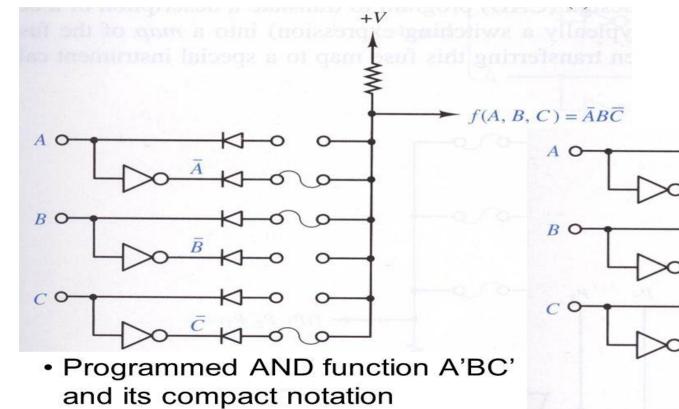

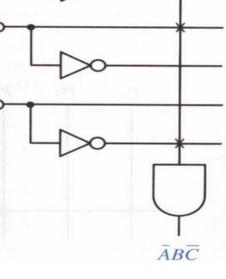

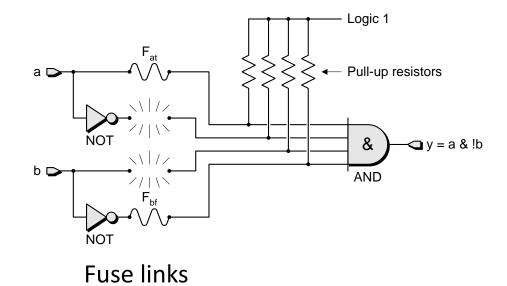

– X means fuse intact (not blown)

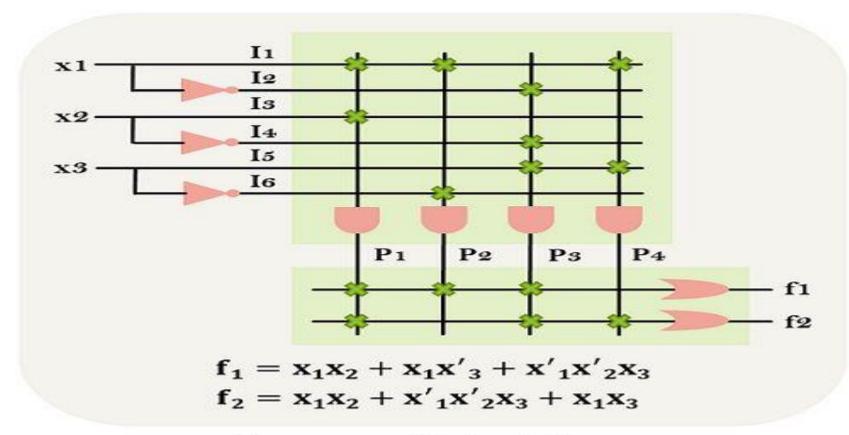

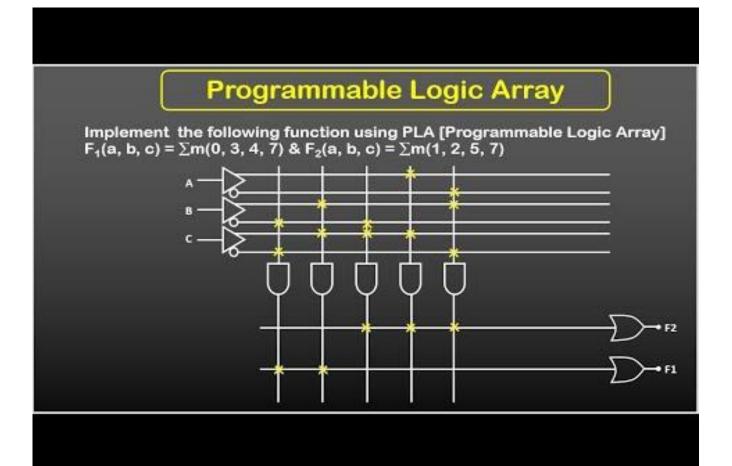

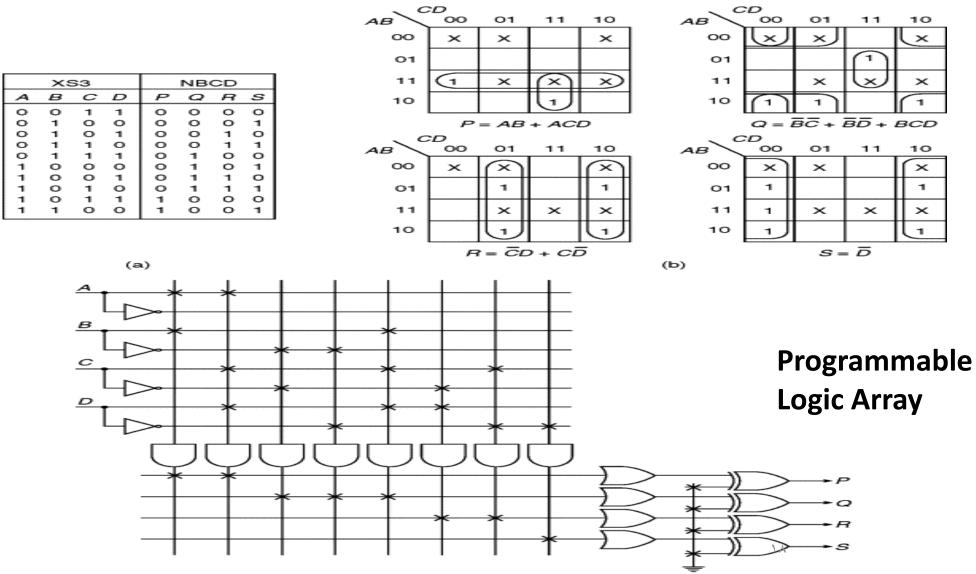

#### PLA (Programmable Logic Array)

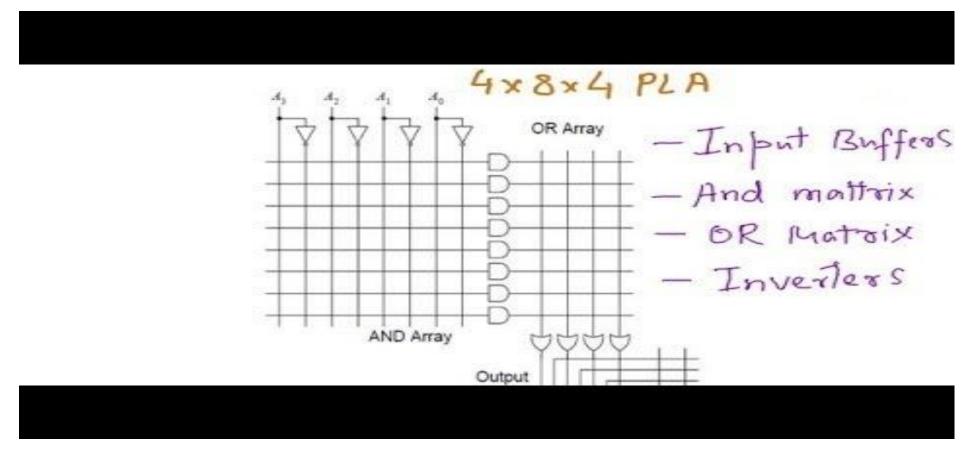

- First device specially for implementing logic circuits, introduced in the early 1970s by Philips.

- Consists of 2 level of logic gates : a programmable "wired" AND-plane followed by a programmable "wired" OR-plane.

- Designed to implement random logic expression in SOP form.

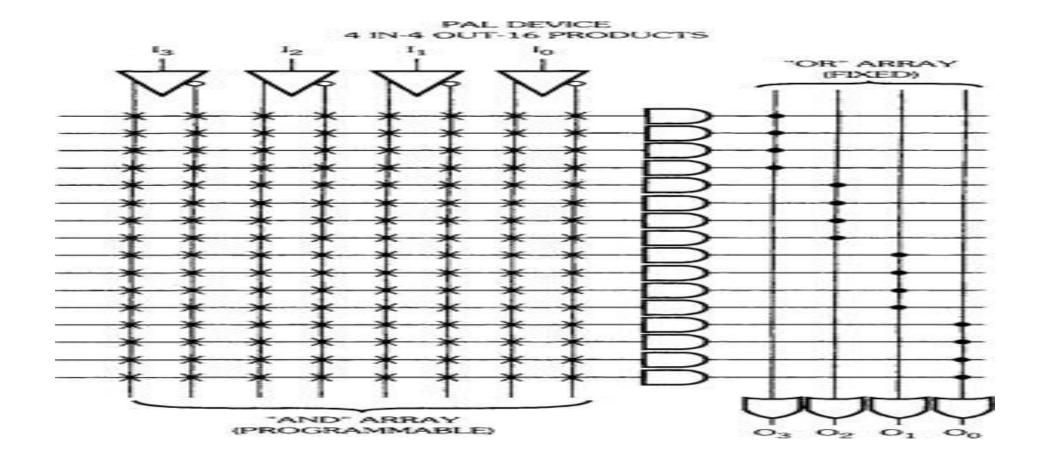

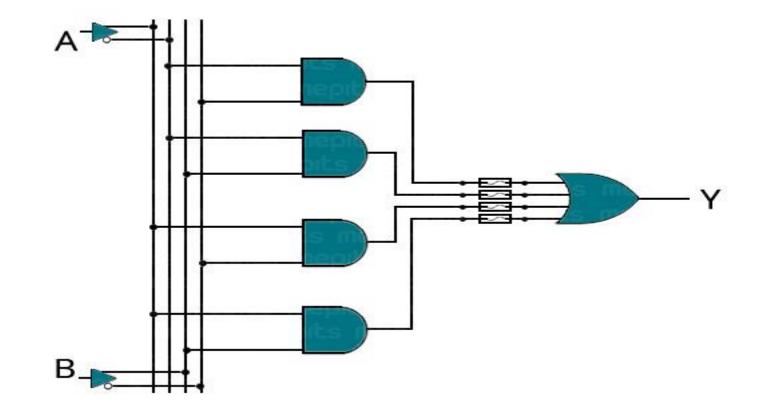

## Programmable Array Logic

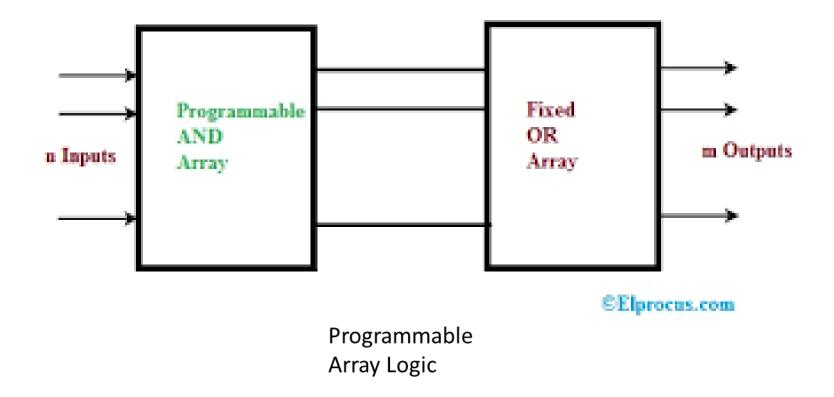

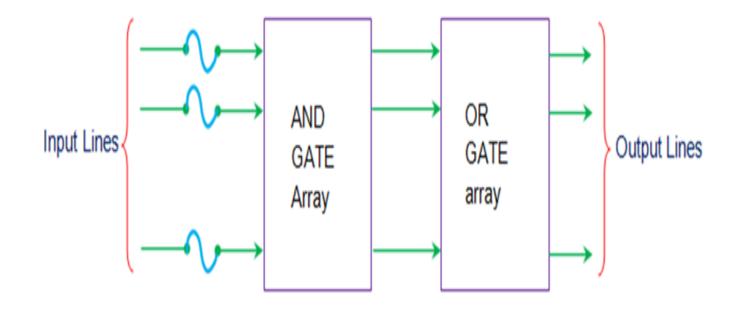

**PALs** use an **OR gate array with fixed logic** while an **AND gate array which can be programmed** as per the requirement of the user. As a result, these devices express the output as a combination of inputs in sum-of-products form.

## Programmable Array Logic

## Programmable Array Logic

Figure 1 Programmable Array Logic (PAL)

#### A Difference :

| S. No. | PAL                                                                                                                                                       | PLA                                                          |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| 1.     | It is moderately expensive and moderately complicated.                                                                                                    | It is expensive than PAL and PROM<br>and complicated to use. |  |

| 2.     |                                                                                                                                                           | ND array<br>OR array are programmable.                       |  |

| 3.     | It is easier to program<br>because only the AND gates<br>are programmable.<br>It is complicated to program b<br>both the AND and OR gate<br>programmable. |                                                              |  |

| 4.     | It is less flexible due to fixed<br>OR gates.                                                                                                             | It is more flexible than PAL.                                |  |

# Generic Logic Array

Generic Logic Array (GLA)

• These devices had their properties similar to those of PALs in addition to which they were electrically erasable and re-programmable. This important feature proved to be meritorious as it considerably eased the prototype design which in turn reduced the time to market.

#### Using a PROM for logic design

Hong Kong Institute of Vocational Education (Tsing Yi) Electrical and Telecommunications Course Board

E&T1350 Electronics

#### **Programmable Logic Devices**

|                 | PROM       | PAL        | PLA   |

|-----------------|------------|------------|-------|

| Input lines     | hard-wired | prog.      | prog. |

| Output lines    | prog.      | hard-wired | prog. |

| Versatility     | low        | moderate   | high  |

| Difficulty in   | low        | moderate   | high  |

| manufacturing,  |            |            |       |

| programming and |            |            |       |

| testing         |            |            |       |

PAL & GAL 1 / page 10

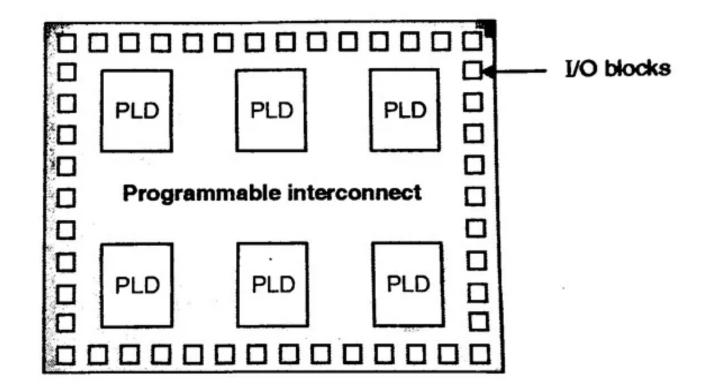

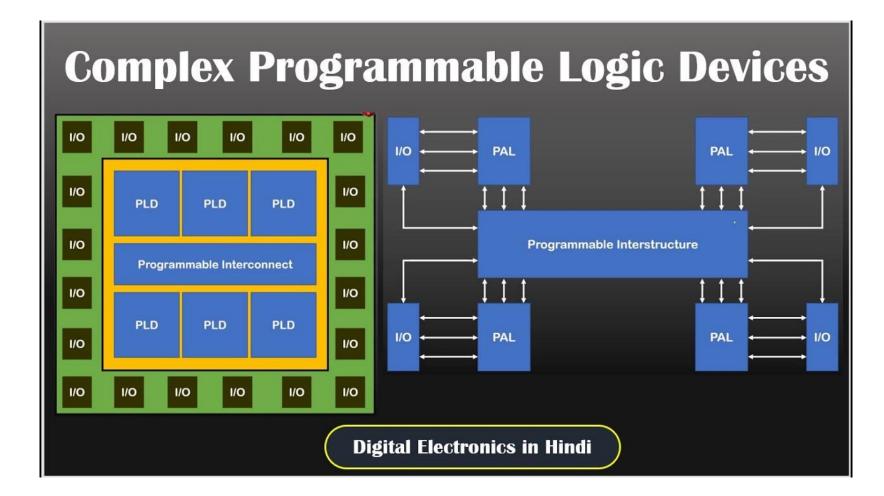

## Complex Programmable Logic Device

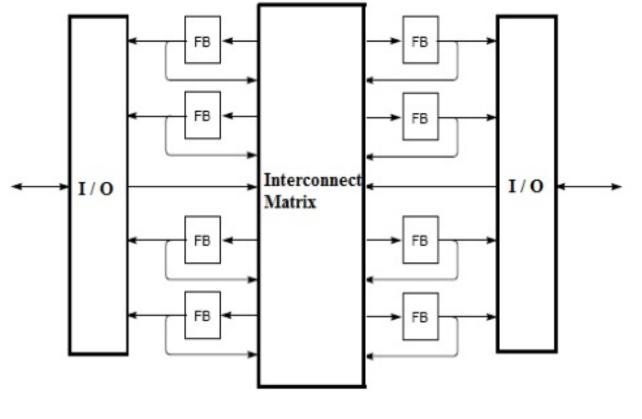

#### CPLD

Traditionally, CPLDs have been chosen over FPGAs whenever high-performance logic is required, Because of its less flexible internal architecture, the delay is more predictable and usually shorter.

# Complex Programmable Logic Device

- Complex Programmable Logic Device (CPLD)

- CPLDs are denser than PALs and comprise of a large number of programmable logical elements. The interconnection between these macro cells is to be established by the user through the interconnecting network.

- Here sum-of-product establishing logical elements are combined together to form structures in order to reduce the number of input-output (IO) pins.

- This facilitates the implementation of more complex logic design with slightly worse propagation time when compared to that of PALs.

- These offer predictable timing characteristics making them most suitable for critical control applications with high performance.

- CPLDs are preferred to implement combinational logic based designs.

#### **Complex Programmable Logic Device**

# Complex Programmable Logic Device

# Complex Programmable Logic Device

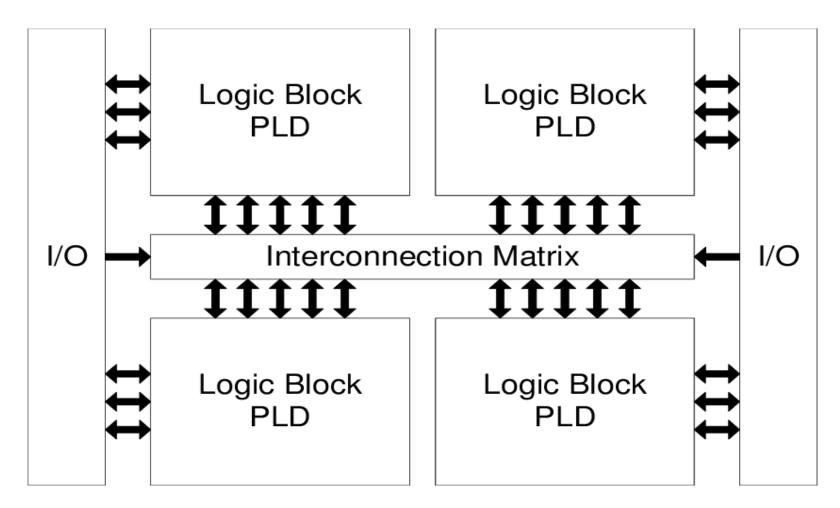

## CPLD (Complex PLD)

- CPLDs were an evolutionary step from even smaller devices that preceded them

- CPLDs can be thought of as multiple PLDs (plus some programmable interconnect) in a single chip.

- The larger size of a CPLD allows you to implement either more logic equations or a more complicated design.

- Because CPLDs can hold larger designs than PLDs, their potential uses are more varied.

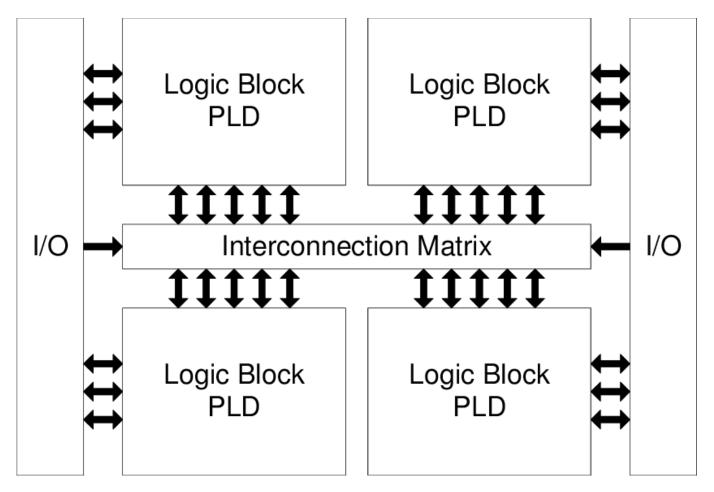

It contain programmable logic components called "logic blocks".

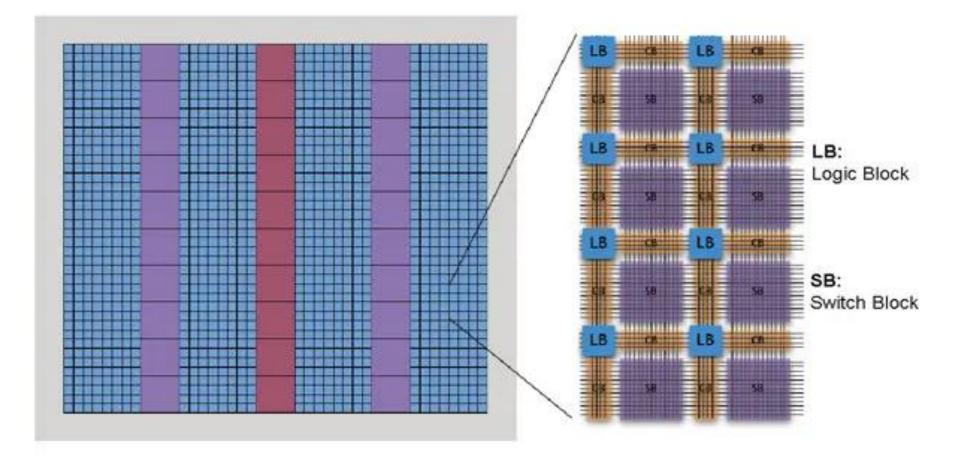

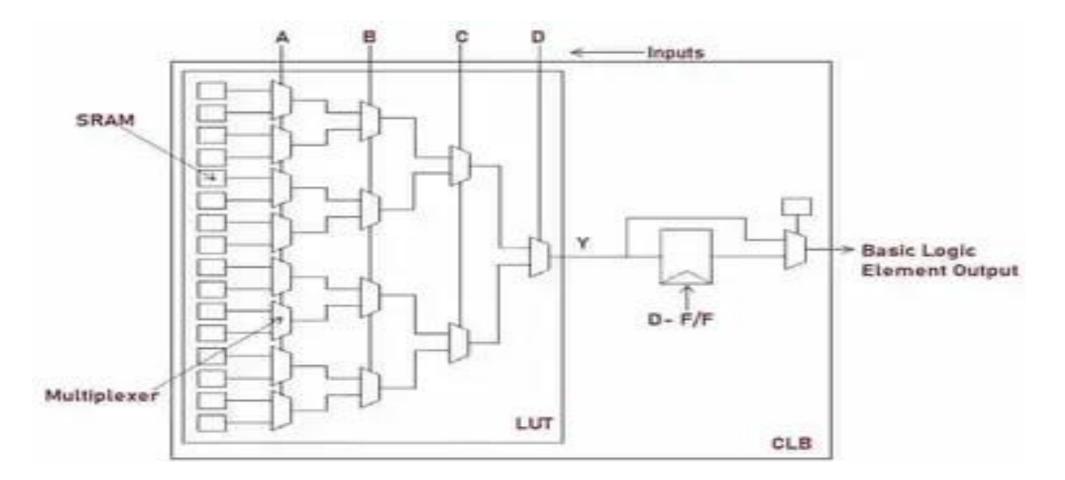

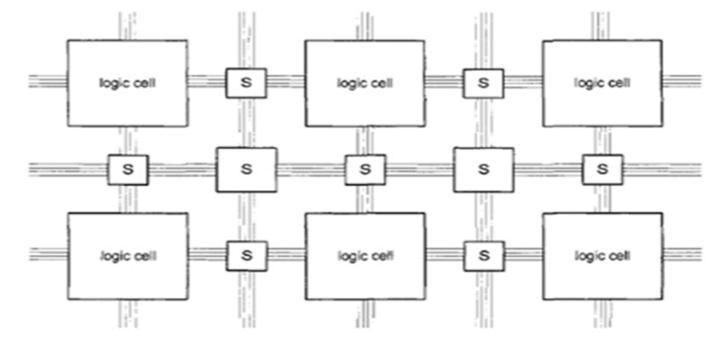

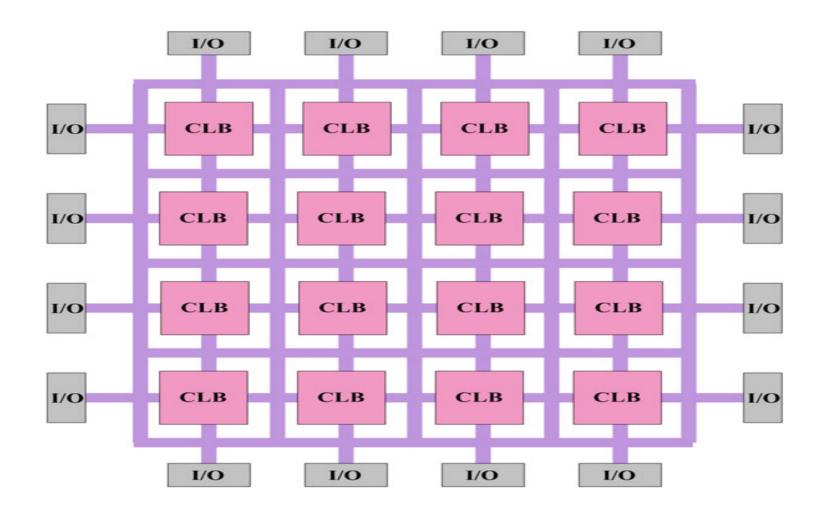

Conceptual structure of an FPGA device.

## What is an FPGA?

## FPGA

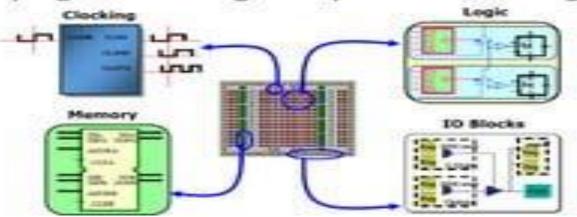

- Programmable (= reconfigurable) Digital System

- Component

- □ Basic components

- Combinational logics

- Flip Flops

- Macro components

- Multiplier (large combinational logic)

- Random Access Memory (Large Density)

- Read Only memory (Large Density)

- CPU

- Programmable Interconnection

- □ Programmable Input/Output circuit

- Programmable Clock Generator

4

## FPGA = "Programmable hardware"

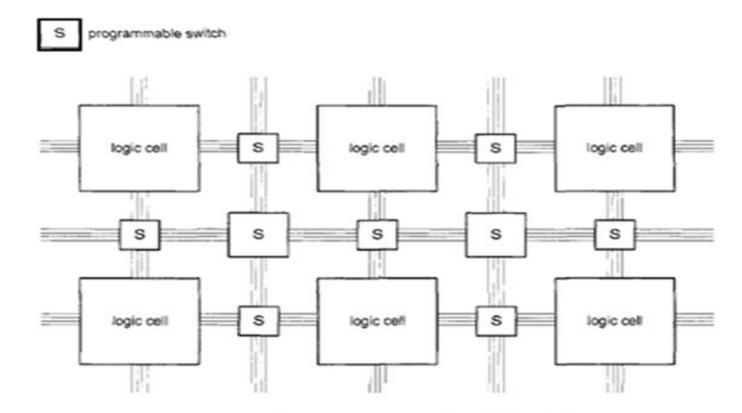

- > Integrated circuit containing many identical logic cells.

- Each logic cell can independently take on one of a limited set of functions.

- The individual cells are interconnected by a matrix of wires and programmable switches.

- Larger FPGAs provide additional functional blocks:

- Phase-locked loop clock conditioning

- >Serializer/deserializer

- Large amounts of on-chip memory

- Dedicated multiplier/accumulator ("DSP") components

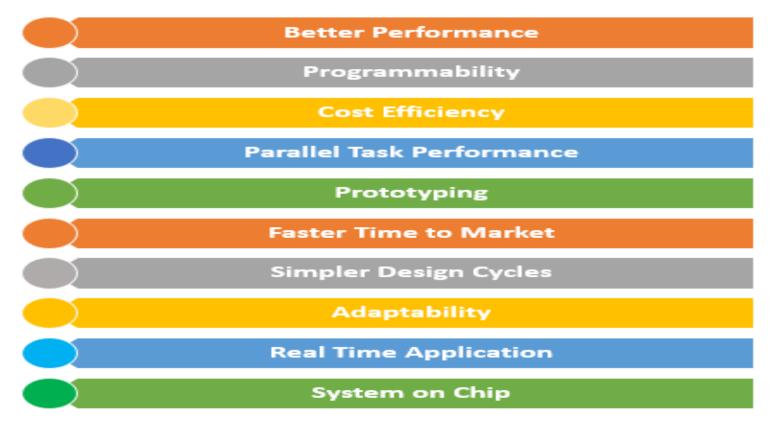

### **Top 10 FPGA Advantages**

|             | CPLD        | FPGA    |

|-------------|-------------|---------|

| Flexibility | Low         | High    |

| Price       | Low         | High    |

| Security    | High        | Low     |

| Speed       | High        | High    |

| Capacity    | Flexibility | High    |

| Application | Simple      | Complex |

FPGA

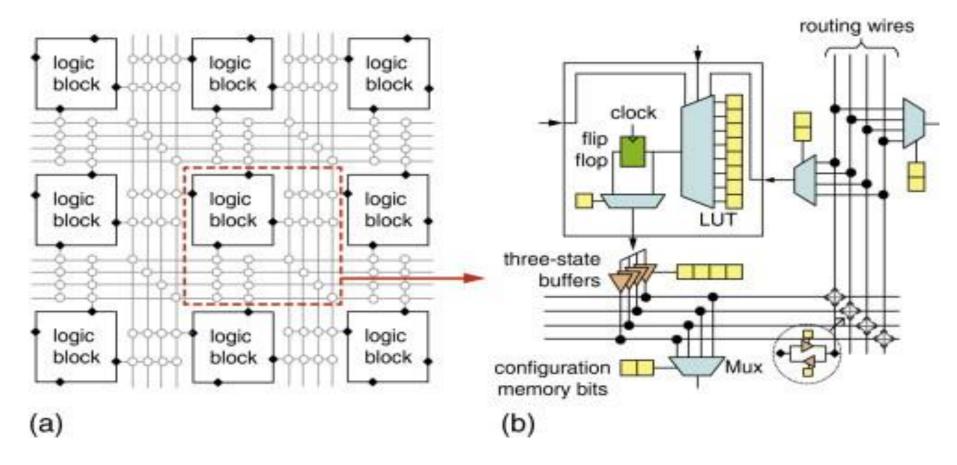

An afield-programmable gate array (FPGA) is a logic device that contains a two-dimensional array of generic logic cells and programmable switches. The conceptual structure of an FPGA device is shown in Figure .1. A logic cell can be configured (i.e., programmed) to perform a simple function, and a programmable switch can be customized to provide interconnections among the logic cells.

A custom design can be implemented by specifying the function of each logic cell and selectively setting the connection of each programmable switch. Once the design and synthesis are completed, we can use a simple adaptor cable to download the desired logic cell and switch configuration to the FPGA device and obtain the custom circuit. Since this process can be done "in the field" rather than "in a fabrication facility (fab)," the device is known as field programmable.

S programmable switch

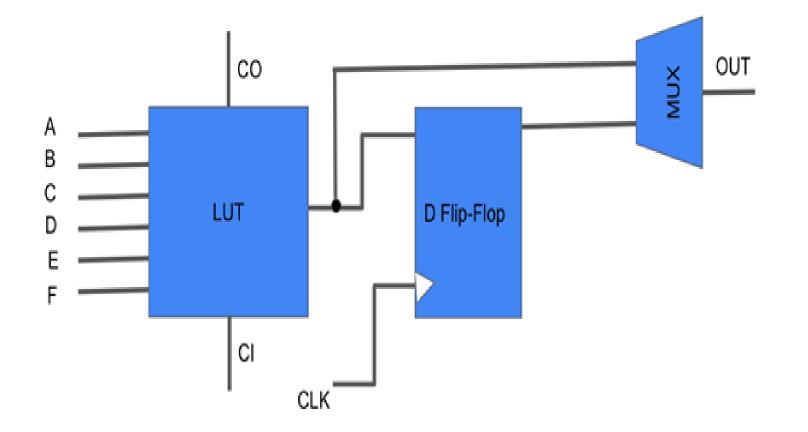

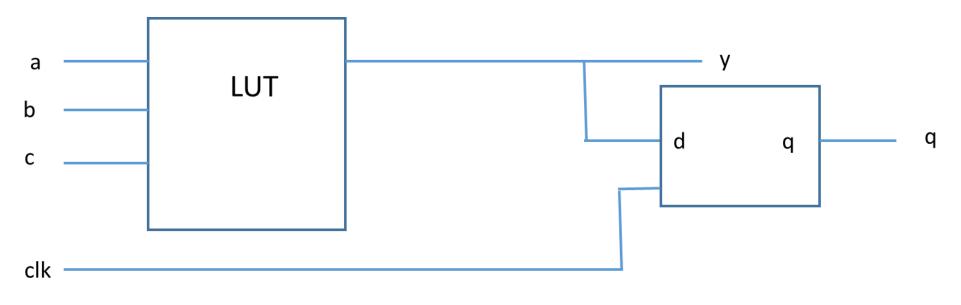

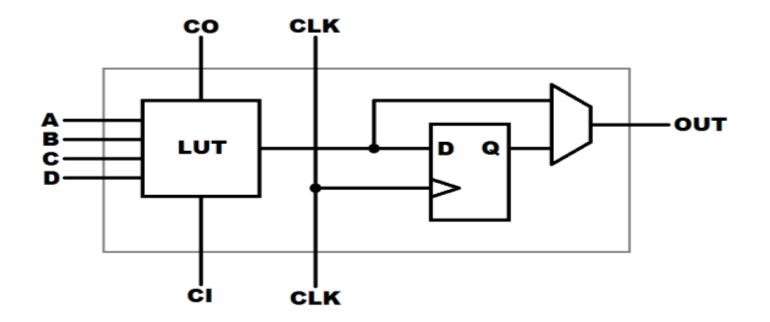

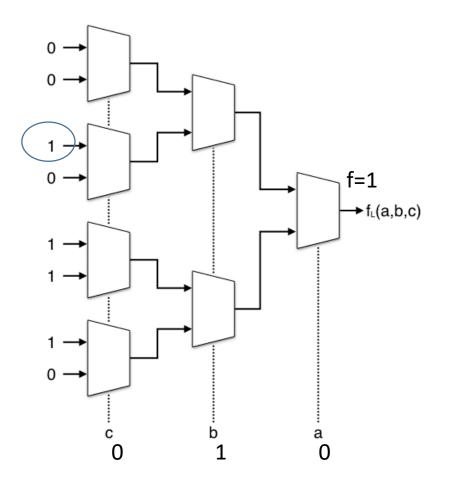

## LUT based logic cell

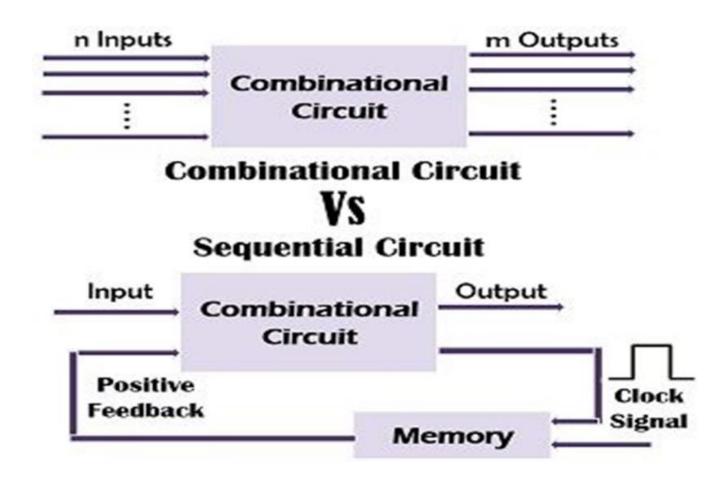

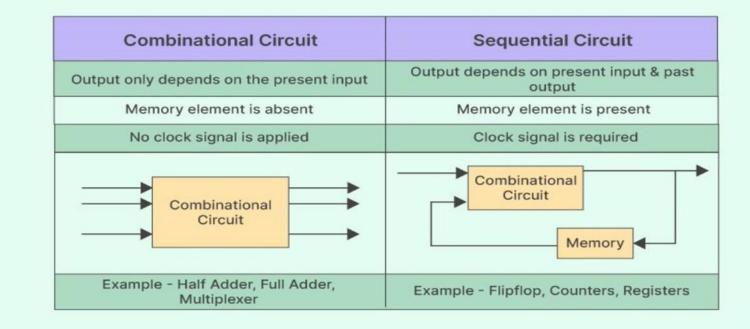

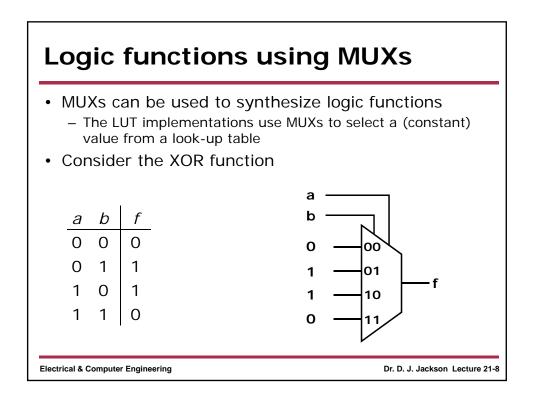

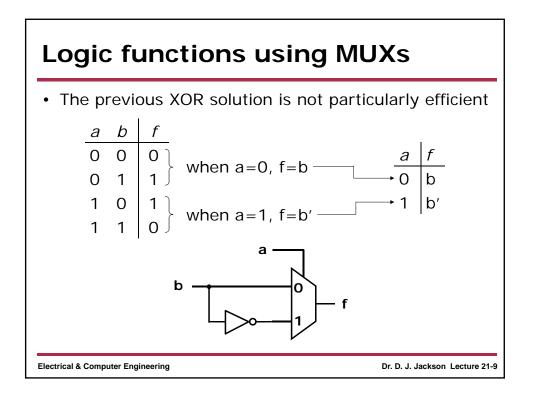

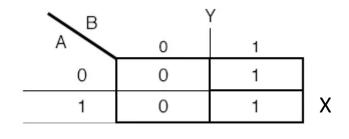

logic cell usually contains a small configurable Α combinational circuit with a D-type flip-flop (D FF). The most common method to implement a configurable combinational circuit is a look-up table (LUT). An n-input LUT can be considered as a small 2<sup>n</sup> memory. By properly writing the memory content, we can use an LUT to implement any n-input combinational function. The conceptual diagram of a three input LUT-based logic cell is shown in Figure

2.(a). An example of a three-input LUT implementation of *a xor* b xor c is shown in Figure 2.(b). Note that the output of the LUT can be used directly or stored to the D FF. The latter can be used to implement sequential circuits.

| Α | b | C | Y |  |

|---|---|---|---|--|

| 0 | 0 | 0 | 0 |  |

| 0 | 0 | 1 | 1 |  |

| 0 | 1 | 0 | 1 |  |

| 0 | 1 | 1 | 0 |  |

| 1 | 0 | 0 | 1 |  |

| 1 | 0 | 1 | 0 |  |

| 1 | 1 | 0 | 0 |  |

| 1 | 1 | 1 | 1 |  |

Figure 2-b Example Table Figure 2- Three input LUT based logic circuit

### **Combinational vs Sequential Circuits**

unstop

| Perfect induction example                                         |   |    |                |    |            |              |  |  |  |  |  |

|-------------------------------------------------------------------|---|----|----------------|----|------------|--------------|--|--|--|--|--|

| <ul> <li>Use perfect induction to prove (xy) '= x'+ y'</li> </ul> |   |    |                |    |            |              |  |  |  |  |  |

| X                                                                 | у | ху | ( <i>xy</i> )′ | Χ' | <i>Y</i> ′ | <i>x'+y'</i> |  |  |  |  |  |

| 0                                                                 | 0 | 0  | 1              | 1  | 1          | 1            |  |  |  |  |  |

| 0                                                                 | 1 | 0  | 1              | 1  | 0          | 1            |  |  |  |  |  |

| 1                                                                 | 0 | 0  | 1              | 0  | 1          | 1            |  |  |  |  |  |

| 1                                                                 | 1 | 1  | 0              | 0  | 0          | 0            |  |  |  |  |  |

|                                                                   |   |    |                |    |            |              |  |  |  |  |  |

| equivalent                                                        |   |    |                |    |            |              |  |  |  |  |  |

| Electrical & Computer Engineering Dr. D. J. Jackson Lecture 3-8   |   |    |                |    |            |              |  |  |  |  |  |

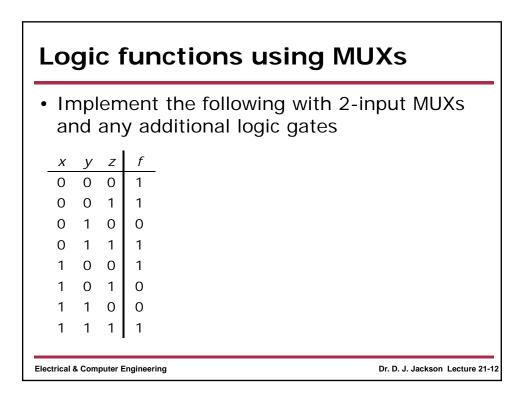

| Shannon's expansion example                                   |   |   |                                                                                                                                                                           |                                    |  |  |  |

|---------------------------------------------------------------|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| x                                                             | y | Ζ | f           1           0           1           0           1           0           0           0           0           0           0           0           0           0 | f=x'y'z'+x'y'z+x'yz+xy'z'+xy'z     |  |  |  |

| 0                                                             | 0 | 0 | 1                                                                                                                                                                         |                                    |  |  |  |

| 0                                                             | 0 | 1 | 1                                                                                                                                                                         | choose z as the expansion variable |  |  |  |

| 0                                                             | 1 | 0 | 0                                                                                                                                                                         |                                    |  |  |  |

| 0                                                             | 1 | 1 | 1                                                                                                                                                                         |                                    |  |  |  |

| 1                                                             | 0 | 0 | 1                                                                                                                                                                         |                                    |  |  |  |

| 1                                                             | 0 | 1 | 1                                                                                                                                                                         |                                    |  |  |  |

| 1                                                             | 1 | 0 | 0                                                                                                                                                                         |                                    |  |  |  |

| 1                                                             | 1 | 1 | 0                                                                                                                                                                         |                                    |  |  |  |

|                                                               |   |   |                                                                                                                                                                           |                                    |  |  |  |

| Electrical & Computer Engineering Dr. D. J. Jackson Lecture 2 |   |   |                                                                                                                                                                           |                                    |  |  |  |

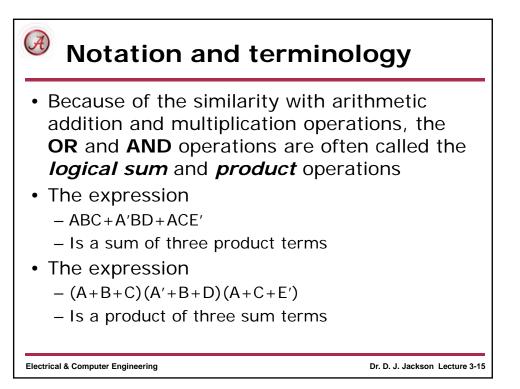

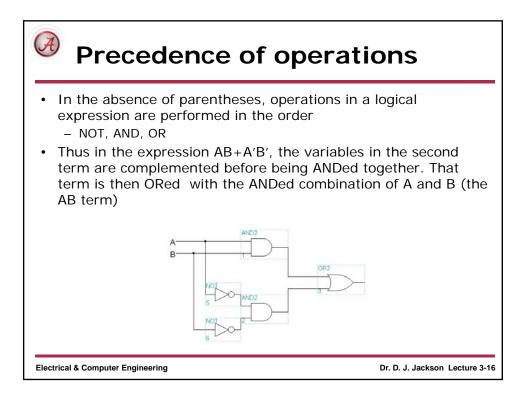

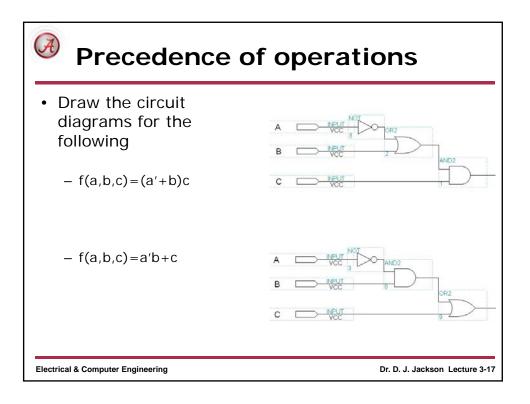

Lecture Three

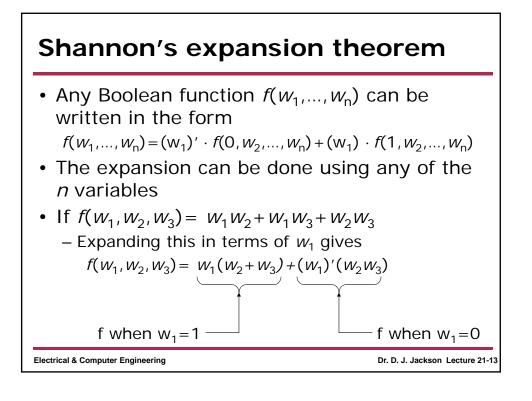

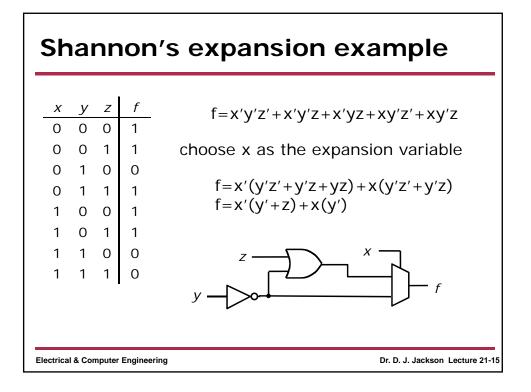

## Shannon's Expansion Theorem

T11a:

$F(X1,...,Xn) = F(0, X2,...,Xn) \bullet X1 + F(1, X2,...,Xn) \bullet X1$ T11b:

$F(X1,...,Xn) = [F(1, X2,...,Xn) + X1] \bullet [F(0, X2,...,Xn) + X1]$

## Shannon's Expansion Theorem

### Let X1=0 in T11a

$$F(X1,...,Xn) = F(0, X2,...,Xn) \bullet \overline{0} + F(1, X2,...,Xn) \bullet 0$$

$$F(X1,...,Xn) = F(0, X2,...,Xn) \bullet 1 + F(1, X2,...,Xn) \bullet 0$$

$$F(X1,...,Xn) = F(0, X2,...,Xn)$$

Let X1=1 in T11a

$F(X1,...,Xn) = F(0, X2,...,Xn) \bullet 1 + F(1, X2,...,Xn) \bullet 1$   $F(X1,...,Xn) = F(0, X2,...,Xn) \bullet 0 + F(1, X2,...,Xn) \bullet 1$ F(X1,...,Xn) = F(1, X2,...,Xn)

## Shannon's Expansion Theorem $F(X1,...,Xn) = F(0,0,X3,...,Xn) \bullet \overline{X1} \bullet \overline{X2} + F(0,1,X3,...,Xn) \bullet \overline{X1} \bullet X2$ $+ F(1,0,X3,...,Xn) \bullet X1 \bullet \overline{X2} + F(1,1,X3,...,Xn) \bullet X1 \bullet X2$

$$= I0 \bullet \overline{X1} \bullet \overline{X2} + I1 \bullet \overline{X1} \bullet X2 + I2 \bullet X1 \bullet \overline{X2} + I3 \bullet X1 \bullet X2$$

$$= I0 \bullet m0 + I1 \bullet m1 + I2 \bullet m2 + I3 \bullet m3$$

$$= \sum_{k=0}^{2^{n}-1} Ki \bullet m_{i} \quad \text{Where} \quad m_{i} = m_{i}(X1, X2)$$

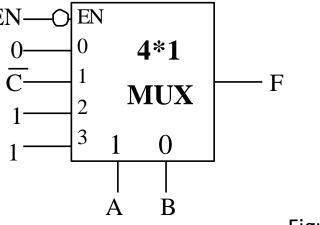

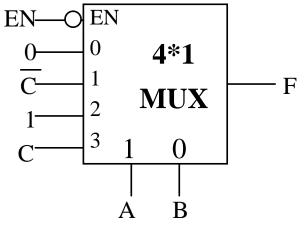

## Example

Design a circuit using MUX to implement the following function by applying Shannon's Expansion Theorem T11a with respect to A and B

$F(A, B, C) = A + B.\overline{C}$

Solution

```

F(A, B, C) = F(0,0, C).\overline{A}.\overline{B} + F(0,1, C).\overline{A}.B + F(1,0, C).A.\overline{B} + F(1,1, C).A.B

F(0,0,C) = 0 + 0.\overline{C} = 0

F(0,1,C) = 0 + 1.\overline{C} = \overline{C}

F(1,0,C) = 1 + 0.\overline{C} = 1

F(1,1,C) = 1 + 1.\overline{C} = 1

```

## Analyzing a Multiplexer Design

$F(A, B, C) = \sum_{i=1}^{2^n - 1} Ki \bullet m_i$ Where  $m_i = m_i(A, B)$  $= I0 \bullet m0 + I1 \bullet m1 + I2 \bullet m2 + I3 \bullet m3$  $= 0 \bullet m0 + C \bullet m1 + 1 \bullet m2 + C \bullet m3$ = 0.A.B + C.A.B + 1.A.B + C.A.B $=\overline{A}.B.\overline{C} + A.\overline{B}.(C + \overline{C}) + A.B.C$  $= m_2 + m_4 + m_5 + m_7$  $=\sum m(2,4,5,7)$

Figure (2)

Field Programmable Gate Array (FPGA)

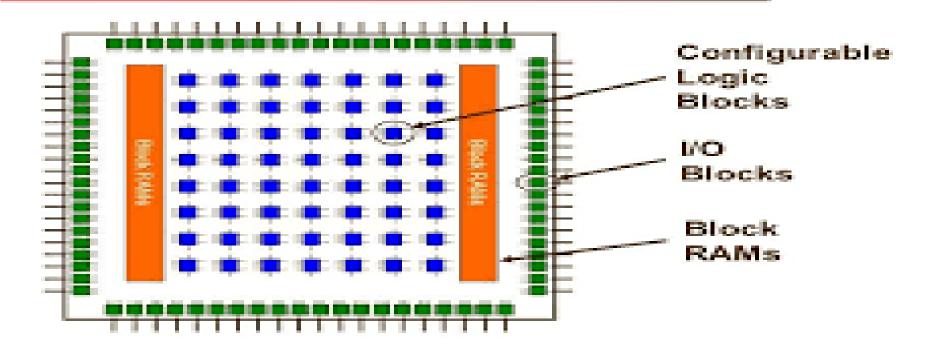

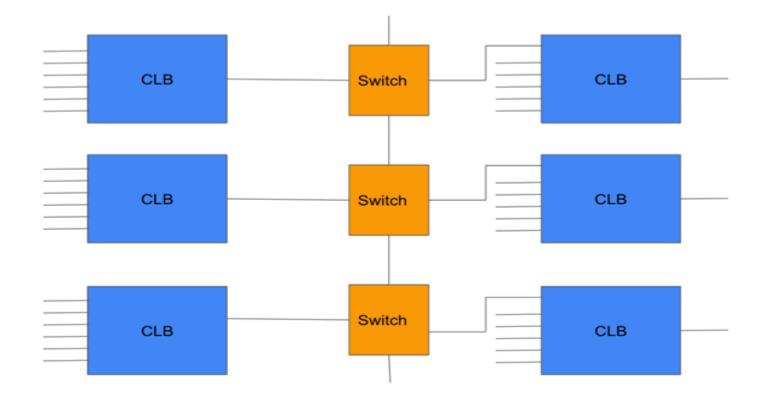

- FPGAs are based on gate array technology, unlike the PROM technology of early PLDs. These devices comprise configurable logic blocks (CLBs) along with an interconnection matrix running in between.

- FPGAs work based on the look-up tables (LUTs) and the flip-flops that form a part of CLB. The user has to program the CLBs to perform a certain logical function and then use the interconnection matrix to connect one or more logic blocks together. Further, they comprise input-output (I/O) ports facilitating the design both from the point of programming as well as debugging.

# • These devices are capable of implementing state-machine-based sequential designs along with designs based on combinational logic.

- FPGAs are used to realize more complex designs when compared to CPLDs due to their high density. Moreover, FPGAs offer the customer the flexibility to design/re-design the logic even after being deployed in the work field which gives them the name field-programmable. However, FPGAs have larger propagation delays when compared to CPLDs.

- All of these PLDs are programmable using device programs that transfer the Boolean logic pattern onto the programmable device

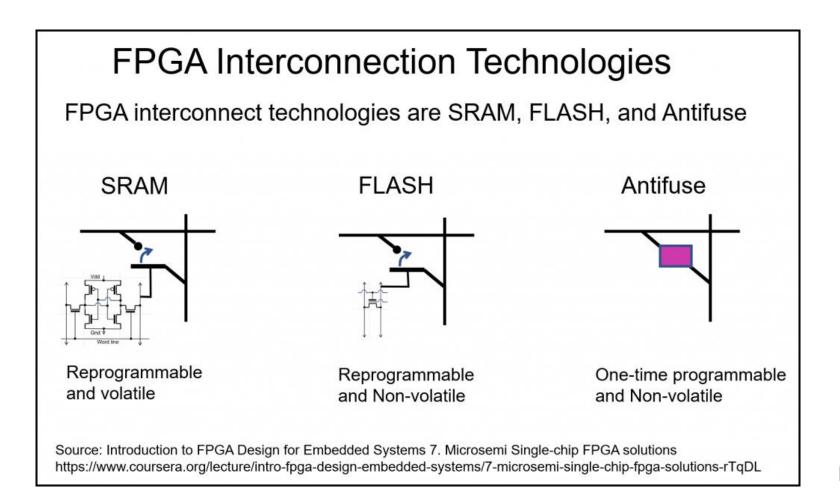

### **Programming Technologies**

• There are a number of programming technologies that have been used for **reconfigurable architectures**. Each of these technologies has different characteristics which in turn have a significant effect on the programmable architecture. Some of the well-known technologies **include static memory, flash, and anti-fuse**.

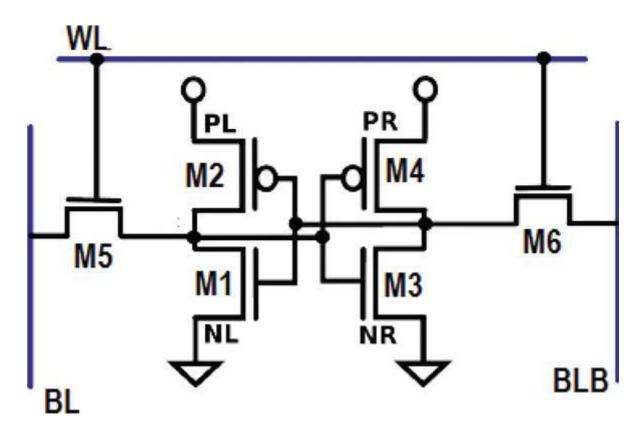

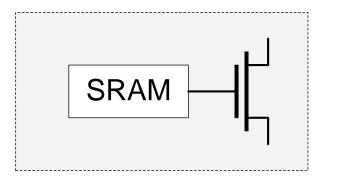

### SRAM-Based Programming Technology

Static memory cells are the basic cells used for SRAM-based FPGAs. Most commercial vendors **use static memory (SRAM)** based programming technology in their devices. These devices use static memory cells which are divided throughout the FPGA to provide configurability. An example of such a memory cell is shown in Fig.3 . In an SRAM-based FPGA, SRAM cells are mainly used for the following purposes:

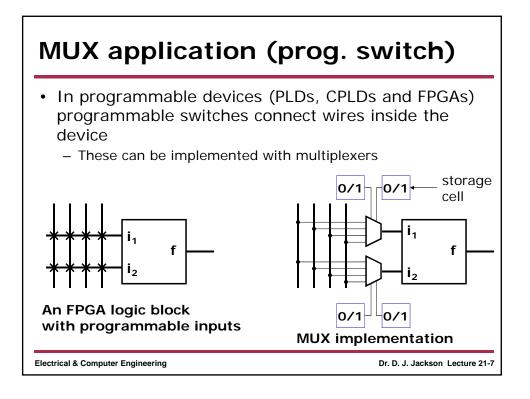

1. To program **the routing interconnect** of FPGAs which are generally steered by small multiplexors.

2. To program **Configurable Logic Blocks** (CLBs) that are used to implement logic functions.

• SRAM-based programming technology has become the dominant approach for FPGAs because of its re-programmability and the use of standard CMOS process technology therefore leading to increased integration, higher speed and lower dynamic power consumption of new process with smaller geometry. There are however a number of drawbacks associated with SRAM-based programming technology. For example an SRAM cell requires 6 transistors which makes the use of this technology costly in terms of area compared to other programming technologies. Further SRAM cells are volatile in nature and external devices are required to permanently store the configuration data. These external devices add to the cost and area overhead of SRAM-based FPGAs.

Figure -3-

## Flash Programming Technology

One alternative to the SRAM-based programming technology is the use of flash or EEPROM-based programming technology. Flash-based programming technology

offers several advantages. For example, this programming technology is *nonvolatile* in nature. Flash-based programming technology is *also more area-efficient* than SRAM-based programming technology. Flash-based programming technology has its own disadvantages, flash-based technology uses **non-standard CMOS processes**.

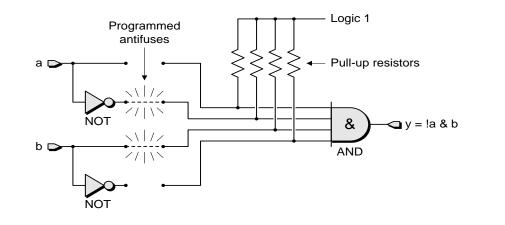

### Anti-fuse Programming Technology

An alternative to SRAM and flash-based technologies is anti-fuse programming technology. The primary advantage of anti-fuse programming technology is its **low area**. Also, this technology has lower **resistance and parasitic capacitance than the other two**.

Programming Technologies

- programming technologies. Further, this technology is non-volatile in nature. There are however significant disadvantages associated with this programming technology.

- For example, this technology does not make use of the standard CMOS process. Also, anti-fuse programming technology-based devices can **not be reprogrammed**.

Figure -4-

Anti-fuse links

Volatile memory – SRAM programmable

Figure -5-

| Technology                    | Symbol | Predominantly<br>associated with |

|-------------------------------|--------|----------------------------------|

| Fusible-link                  | -~~-   | SPLDs                            |

| Antifuse                      |        | FPGAs                            |

| EPROM                         | -IL    | SPLDs and CPLDs                  |

| E <sup>2</sup> PROM/<br>FLASH | ЧĽ     | SPLDs and CPLDs<br>(some FPGAs)  |

| SRAM                          |        | FPGAs (some CPLDs)               |

# **Classifying Devices**

## Device can be classed based on their level of programmability

One-Time Programmable: devices can be programmed only once; it's contents can not be changed. While typically these devices are fuse or anti-fuse-based, they can also be low-cost EPROM devices.

Re-programmable: These devices can have their configuration loaded more than once. SRAM-based and Flash-based devices may be reloaded without restriction.

Lecture Four

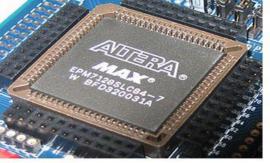

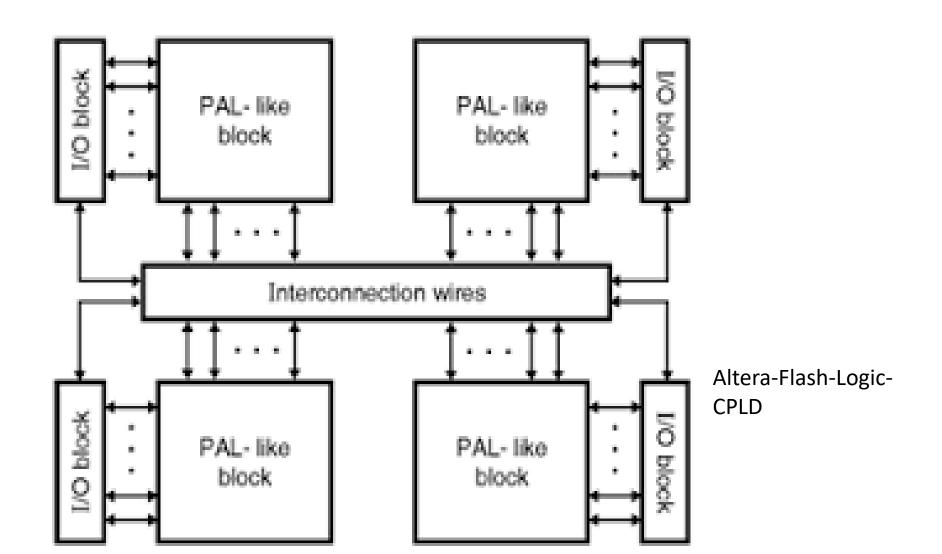

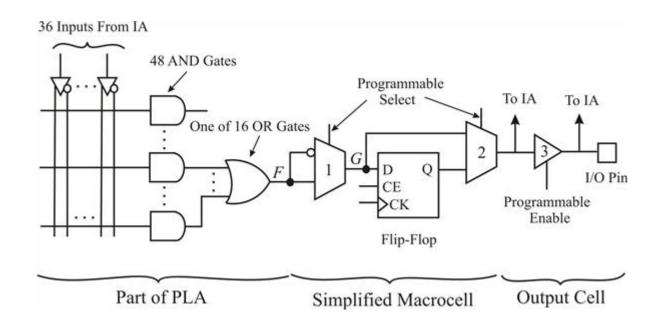

### **Complex Programmable Logic Devices (CPLDs)**

*Complex Programmable Logic Devices (CPLDs)* integrate multiple SPLDs into a single chip. A typical CPLD provides a logic capacity equivalent to about 50 single SPLDs. Altera, the world's second and largest manufacturer – presently, the largest manufacturer is Xilinx – of programmable semiconductors, introduced the MAX 5000, MAX 7000, and MAX 9000 series of CPLDs. MAX Wired – AND gates OR gate Flip Flop

**5000 is based on older technology**, the MAX **7000** family is a high-performance PLD and it is fabricated with **advanced CMOS** technology designed with state-of-the-art logic capacity and speed performance, and **MAX 9000** is very similar to the **MAX 7000** except that it has higher **logic capacity**.

### CPLD

(Complex programmable logic devices)

- Commercially Available CPLDs

- Altera CPLDs

- Advanced Micro Devices (AMD) CPLDs

- Lattice CPLDs

- Cypress CPLDs

- Xilinx CPLDs

- Altera FLASHlogic CPLDs

### Altera CPLD

- Altera has developed three families of chips that fit within the CPLD category:

- MAX 5000

- MAX 7000, and

- MAX 9000

- MAX 5000 represents an older technology that offers a cost effective solution,

- MAX 7000 series is widely used and offers stateof-the-art logic capacity and speed-performance.

CPLD

**Detail of CPLD**

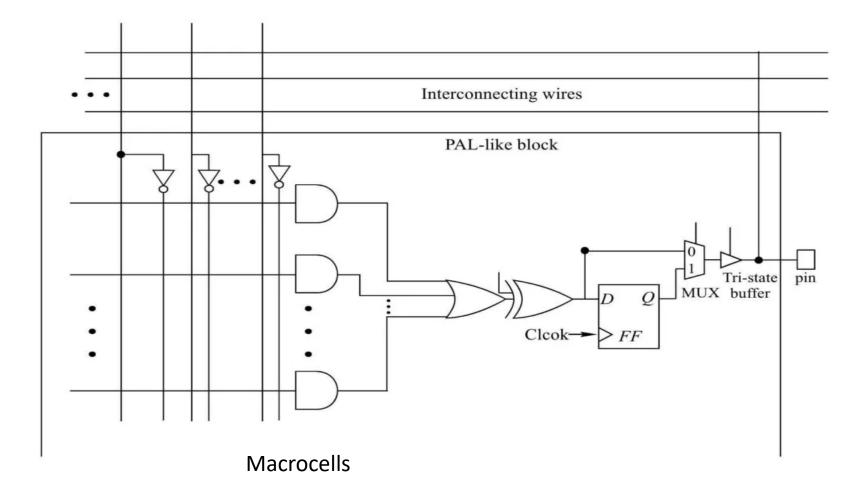

A Complex Programmable Logic Device (CPLD) is a programmable logic device and can **be programmed** by using **VHDL**. CPLDs are based on **EPROM** or EEPROM technology. CPLDs have extended density than the SPLDs. The concept of CPLDs is to have a few macrocells on a single chip with simple **logic paths**. CPLDs are classified depending on the architecture which gives rise to high speed, detailed timing, and simple software flow. The basic CPLD consists of the configurable logic block (CLB) which consists of AND gate arrays and interconnects. The logic blocks are programmable AND, fixed OR devices. PALs and GALs are available only in small sizes, equivalent to a few hundred logic gates. CPLD is an arrangement of multiple SPLD-like blocks on a single chip. CPLD consists of multiple circuit blocks in the chip. The circuit block in CPLD are the same as that of **PLA or PAL blocks**.

The figure below shows an example of a CPLD. This CPLD has four PAL blocks which are connected interconnection wires. The PAL block is also connected to a sub-circuit known as an **I/O block**. The I/O block is connected to a number of input and output pins. The PAL block consists of macrocells. The macrocell consists of flip-flop, a multiplexer, and a tri-state buffer. The flip-flop is used to store the output value produced by the OR gate. The tri-state buffer acts as a switch. In the function block, the AND array gets inputs from the I/O blocks and other function blocks. The product terms are given to fixed OR gates. The outputs of the multiplex or are then sent through a clocked flip-flop. The function blocks are designed similarly to PAL architectures.

The I/O block is used to drive signals to the pins of the CPLD device. The CPLD interconnect is a programmable switch matrix.

Macrocells

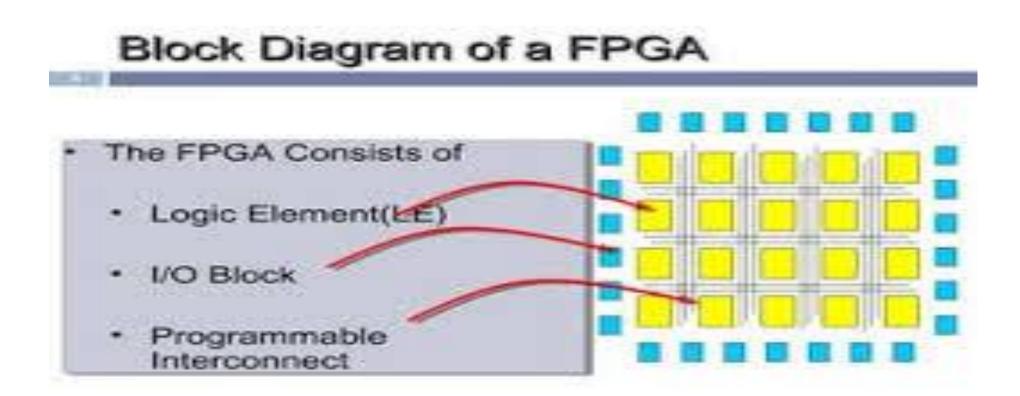

Normally FPGAs comprise of:

- Programmable logic blocks which implement logic functions.

- Programmable routing that connects these logic functions.

- I/O blocks that are connected to logic blocks through routing interconnect and that make off-chip connections.

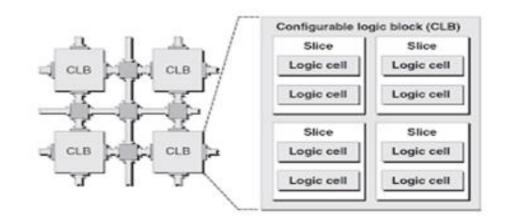

A generalized example of an FPGA is shown in the Figure below where configurable logic blocks (**CLBs**) are arranged in **a two dimensional grid** and are **interconnected** by **programmable routing** resources. I/O blocks are arranged at the **periphery** of the grid and they are also connected to the programmable routing interconnect. The "**programmable/reconfigurable**" term in FPGAs indicates their ability to implement **a new function** on the chip after its fabrication is complete. The configurability programmability of an FPGA is based on an **underlying programming** technology, which can cause a change in the behavior of a pre-fabricated chip after its fabrication.

### **Overview of FPGA Architecture**

**Macro cell** Most FPGA devices also embed certain *macro cells* or *macro blocks*. These are designed and fabricated at the transistor level, and their functionalities complement the general logic cells. Commonly used macro cells include **memory blocks**, **combinational**

**multipliers, clock management circuits**, and I/O interface circuits. Advanced FPGA devices may even contain one or more prefabricated processor cores.

## **Overview of the Xilinx Spartan3 devices**

**Xilinx Spartan-3** family FPGA devices. Based on the ratio between the number of logic cells and the I/O counts, the family is further divided into several subfamilies. Our discussion applies to all the subfamilies.

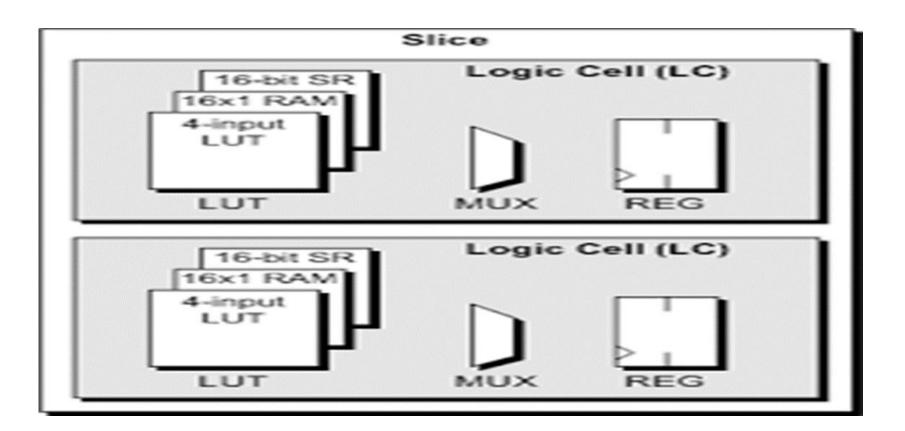

Logic cell, slice, and CLB The most basic element of the Spartan-3 device is a *logic cell* (LC), which contains a four-input LUT and a D FF, similar to that in Figure below. In addition, a logic cell contains a carry circuit, which is used to implement arithmetic functions, and a multiplexing circuit, which is used to implement wide multiplexers. The LUT can also be configured as a 16-by- 1 static random access memory (SRAM) or a 16-bit shift register.

**Conceptual Diagram**

To increase flexibility and improve performance, eight logic cells are combined with a special internal **routing structure**. In Xilinx terms, two logic cells are grouped to form a *slice*, and **four slices** are grouped to form a *configurable logic block* (CLB).

Logic cell

A Slice containing two logic cells

A CLB containing four slices (the number of slices depend on the FPGA family)

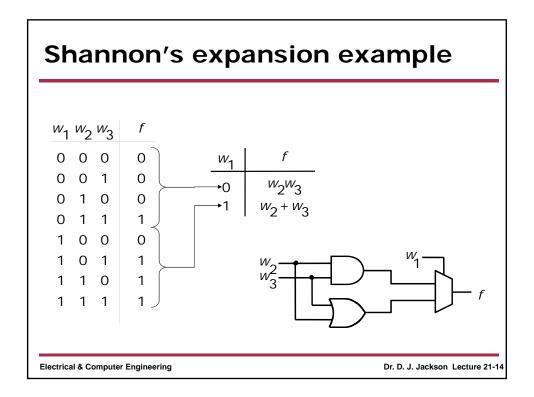

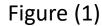

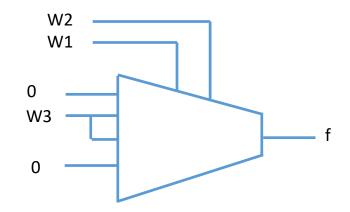

## Example (1):-

Implement the following using 4X1 multiplexer and any any additional logic gates, using w1w2 as a selector?

| W1 | W2 | W3 | f | W1    | W2 | f  |

|----|----|----|---|-------|----|----|

| 0  | 0  | 0  | 0 | <br>0 | 0  | 0  |

| 0  | 0  | 1  | 0 | <br>0 | 1  | W3 |

| 0  | 1  | 0  | 0 | 1     | 0  | W3 |

| 0  | 1  | 1  | 1 | 1     | 1  | 0  |

| 1  | 0  | 0  | 0 |       |    |    |

| 1  | 0  | 1  | 1 |       |    |    |

| 1  | 1  | 0  | 0 |       |    |    |

| 1  | 1  | 1  | 0 |       |    |    |

Implementation of solution of example -1-

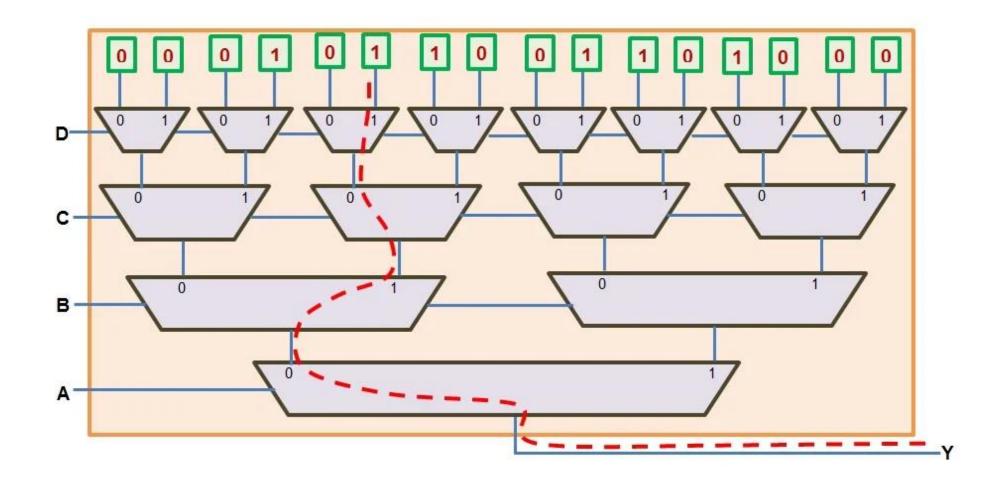

Example (2):-Implement the following using 2X1 multiplexer?

| Α | В | С | D | Υ |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

# LooK UP-table

## Example (3):-Implement the following using 2X1 multiplexer?

| а | b | С | Υ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   |   |   |   |

|   |   |   |   |

|             | CPLD   | FPGA            |

|-------------|--------|-----------------|

| Flexibility | Low    | High            |

| Price       | Low    | High            |

| Security    | High   | Low             |

| Speed       | High   | High            |

| Capacity    | Low    | High            |

| Application | Simple | Complex         |

|             |        | hardwarebee.com |

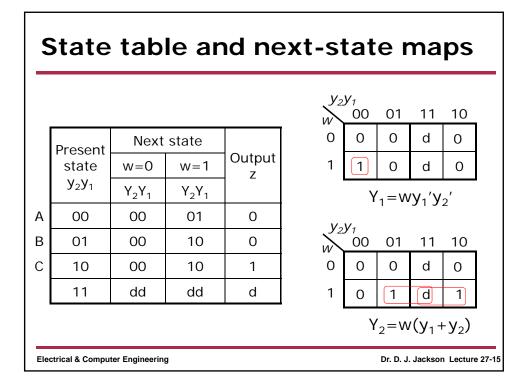

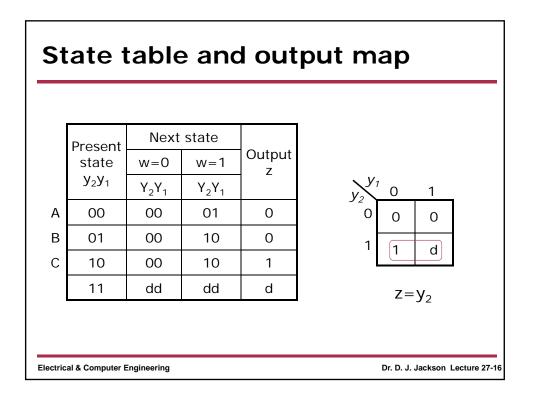

|   | Present                                     | Next                          | state    |             |  |

|---|---------------------------------------------|-------------------------------|----------|-------------|--|

|   | state                                       | w=0                           | w=1      | Output<br>z |  |

|   | <b>y</b> <sub>2</sub> <b>y</b> <sub>1</sub> | Y <sub>2</sub> Y <sub>1</sub> | $Y_2Y_1$ |             |  |

| А | 00                                          | 00                            | 01       | 0           |  |

| В | 01                                          | 00                            | 10       | 0           |  |

| С | 10                                          | 00                            | 10       | 1           |  |

|   | 11                                          | dd                            | dd       | d           |  |

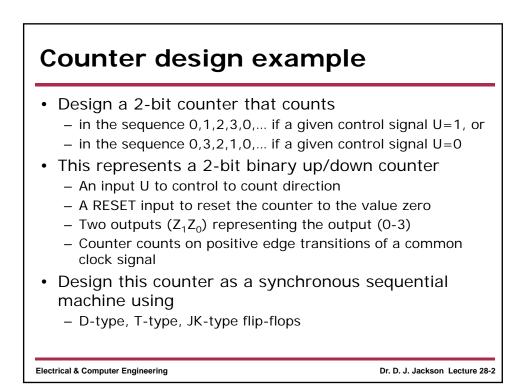

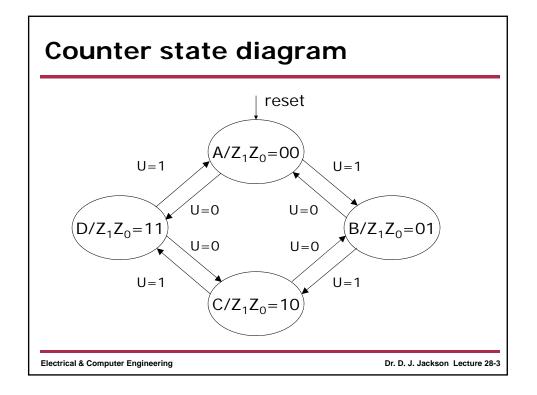

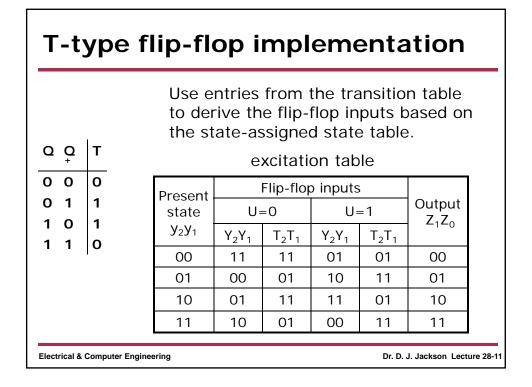

| Count | er sta  | te ta | ble     |           |  |

|-------|---------|-------|---------|-----------|--|

|       | Present | Nex   | t state | Output    |  |

|       | state   | U=0   | U=1     | $Z_1 Z_0$ |  |

|       | А       | D     | В       | 00        |  |

|       | В       | А     | С       | 01        |  |

|       | С       | В     | D       | 10        |  |

|       | D       | С     | А       | 11        |  |

|       |         |       |         |           |  |

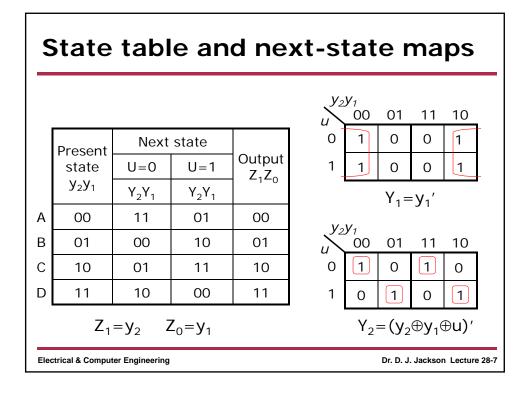

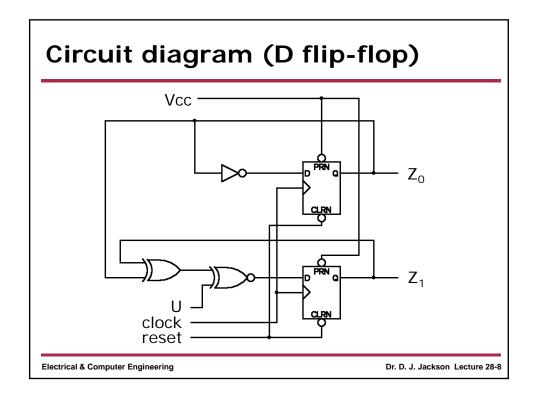

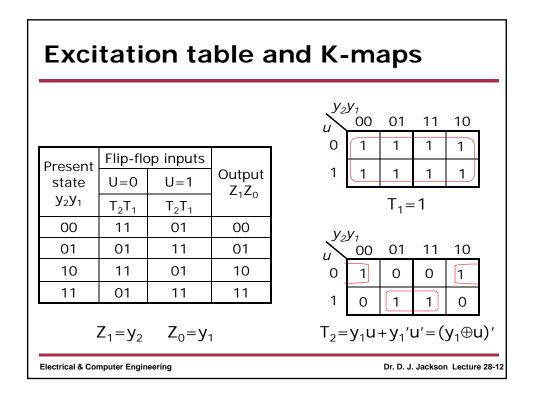

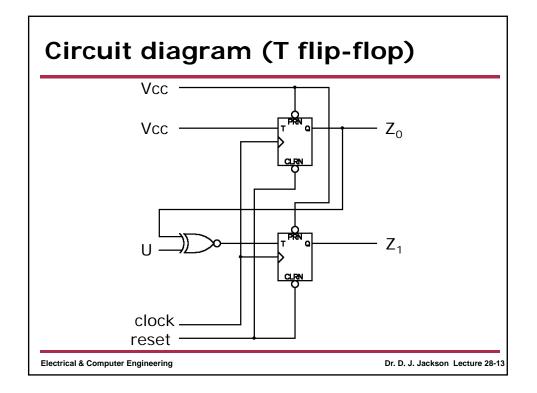

## State-assigned state table

Choosing a state assignment of A=00, B=01, C=10 and D=11 makes sense here because the outputs Z<sub>1</sub>Z<sub>0</sub> become the outputs from the flip-flops directly

|                       | Present     | Next     | state    |                                         |

|-----------------------|-------------|----------|----------|-----------------------------------------|

|                       | state       | U=0      | U=1      | Output<br>Z <sub>1</sub> Z <sub>0</sub> |

|                       | $y_2y_1$    | $Y_2Y_1$ | $Y_2Y_1$ | -1-0                                    |

| А                     | 00          | 11       | 01       | 00                                      |

| В                     | 01          | 00       | 10       | 01                                      |

| С                     | 10          | 01       | 11       | 10                                      |

| D                     | 11          | 10       | 00       | 11                                      |

|                       |             |          |          |                                         |

| Electrical & Computer | Engineering |          |          | Dr. D. J. J                             |

| Tran              | Transition tables |         |        |   |   |    |              |          |               |  |

|-------------------|-------------------|---------|--------|---|---|----|--------------|----------|---------------|--|

| JKQ               | Q+                | Q Q+    | JK     | Т | Q | Q+ | Q            | Q+       | Т             |  |

| 000               | 0                 | 0 0     | 0 D    | 0 | 0 | 0  | 0            | 0        | 0             |  |

| 001               | 1                 | 0 1     | 1 D    | 0 | 1 | 1  | 0            | 1        | 1             |  |

| 010               | 0                 | 1 0     | D 1    | 1 | 0 | 1  | 1            | 0        | 1             |  |

| 011               | 0                 | 1 1     | D 0    | 1 | 1 | 0  | 1            | 1        | 0             |  |

| 100               | 1                 | JK tran | sition |   |   |    | T tra        | ansi     | tion          |  |

| 101               | 1                 | tab     |        |   |   |    |              | able     |               |  |

| 1 1 0             | 1                 |         |        |   |   |    |              |          |               |  |

| 111               |                   |         |        |   |   |    |              |          |               |  |

| Electrical & Comp | uter Engi         | neering |        |   |   |    | Dr. D. J. Ja | ickson l | _ecture 28-10 |  |

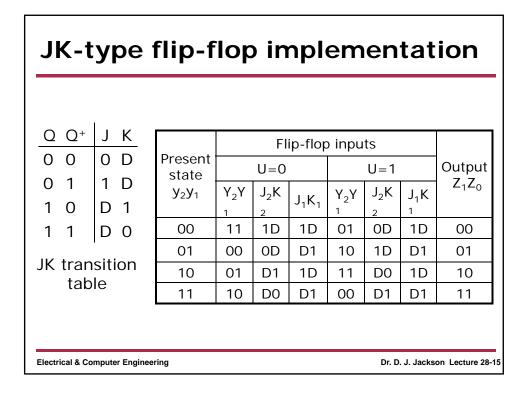

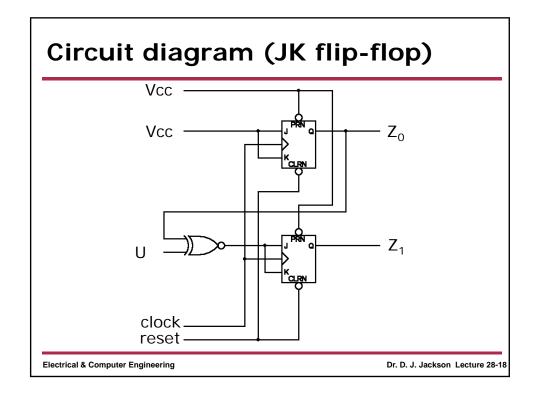

### JK-type flip-flop implementation • Use entries from the transition table to derive the flip-flop inputs based on the state-assigned state table - This must be done for each input (J and K) on each flip-flop Q Q<sup>+</sup> JΚ Next state Present 0 D 0 0 Output state U = 0U=1 $Z_1Z_0$ 0 1 1 D $y_2y_1$ $Y_2Y_1$ $Y_2Y_1$ D 1 1 0 00 11 01 00 D 0 1 1 01 00 10 01 10 01 11 10 JK transition 10 00 11 11 table **Electrical & Computer Engineering** Dr. D. J. Jackson Lecture 28-14

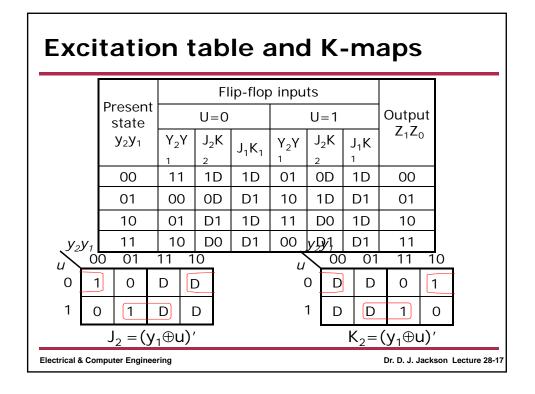

| Exci             | tatio             | on t                  | ab                    | le a                          | anc                   | I K                   | -m               | aps                           |                 |

|------------------|-------------------|-----------------------|-----------------------|-------------------------------|-----------------------|-----------------------|------------------|-------------------------------|-----------------|

|                  |                   |                       | FI                    | ip-flop                       | o inpu                | ts                    |                  |                               |                 |

|                  | Present<br>state  |                       | U=0                   |                               |                       | U = 1                 |                  | Output                        |                 |

|                  | $y_2y_1$          | Υ <sub>2</sub> Υ<br>1 | J <sub>2</sub> K<br>2 | J <sub>1</sub> K <sub>1</sub> | Υ <sub>2</sub> Υ<br>1 | J <sub>2</sub> K<br>2 | J <sub>1</sub> K | Z <sub>1</sub> Z <sub>0</sub> |                 |

|                  | 00                | 11                    | 1D                    | 1D                            | 01                    | 0D                    | 1D               | 00                            |                 |

|                  | 01                | 00                    | 0D                    | D1                            | 10                    | 1D                    | D1               | 01                            |                 |

|                  | 10                | 01                    | D1                    | 1D                            | 11                    | D0                    | 1D               | 10                            |                 |

| $y_{2}y_{1}$     | 11                | 10                    | D0                    | D1                            | 00                    | yÐ⁄1                  | D1               | 11                            |                 |

| $u \sqrt{0}$     | 0 01              | 11 1                  | 0                     |                               | u                     | $\sqrt{00}$           | ) 01             | 11 1                          | 0               |

| 0 1<br>1 1       | D                 | _                     | 1                     |                               |                       | 0 D<br>1 D            | 1                | 1 [<br>1 [                    |                 |

|                  | J <sub>1</sub> =1 |                       |                       |                               |                       |                       | К <sub>1</sub>   | =1                            |                 |

| Electrical & Cor | nputer Enginee    | ring                  |                       |                               |                       |                       |                  | Dr. D. J. Jacks               | son Lecture 28- |

Lecture Six

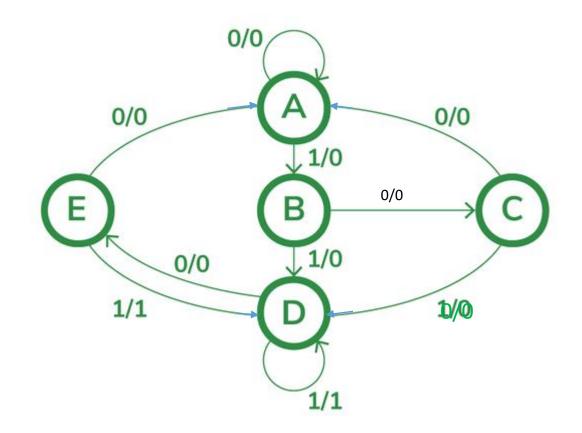

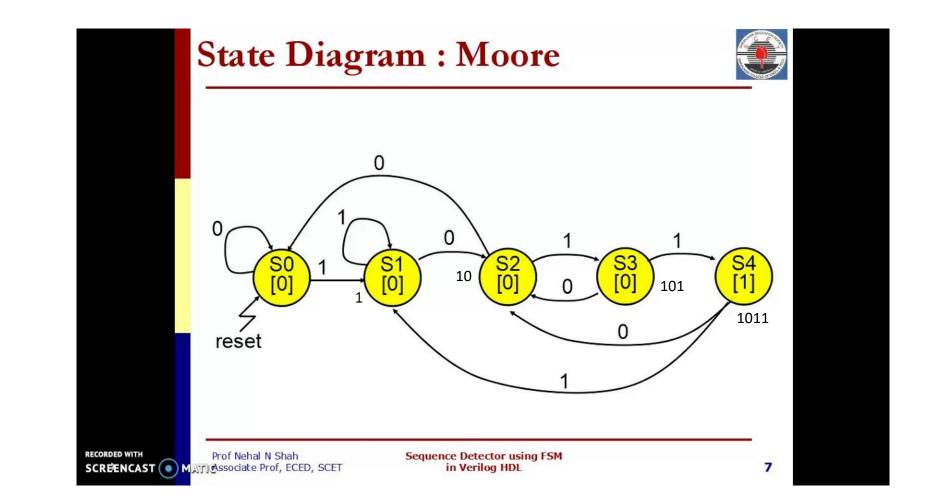

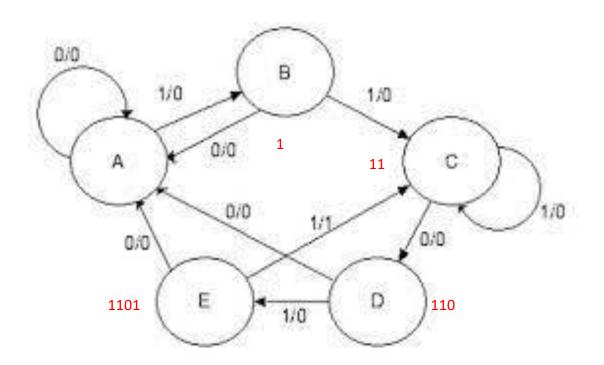

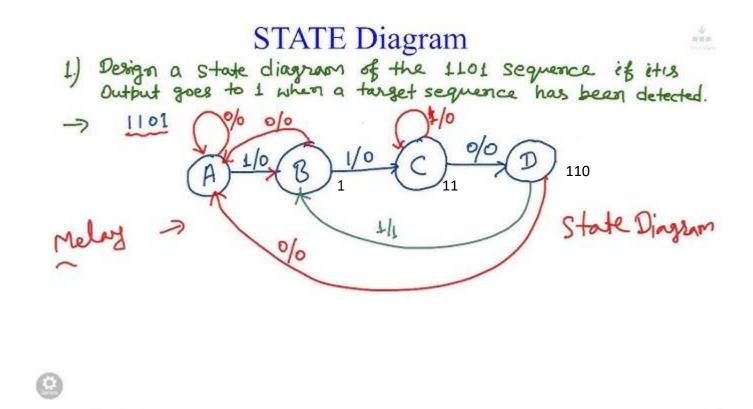

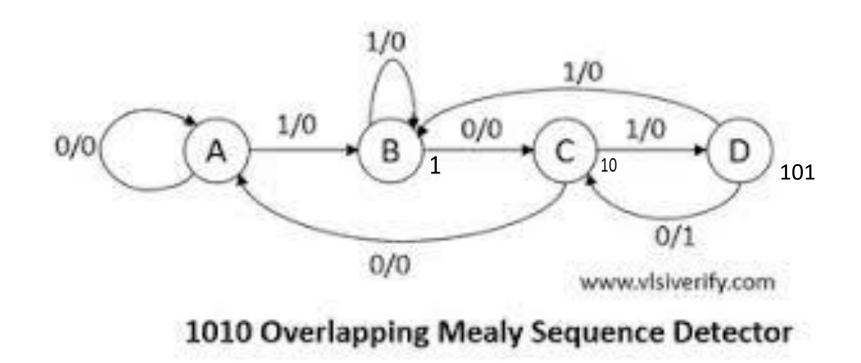

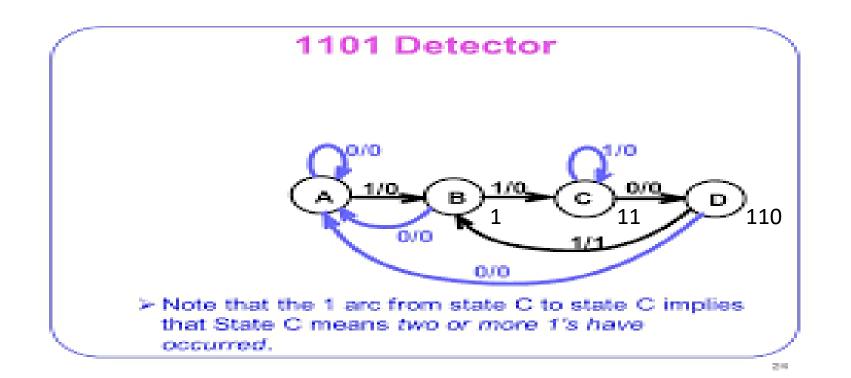

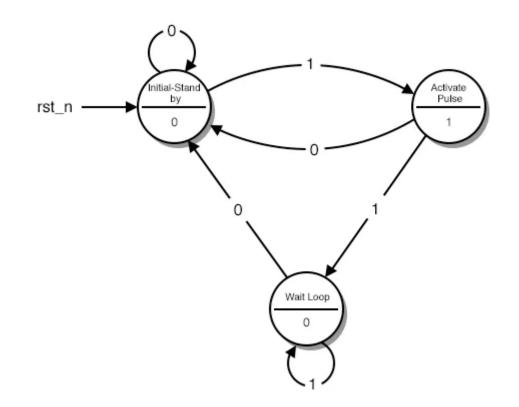

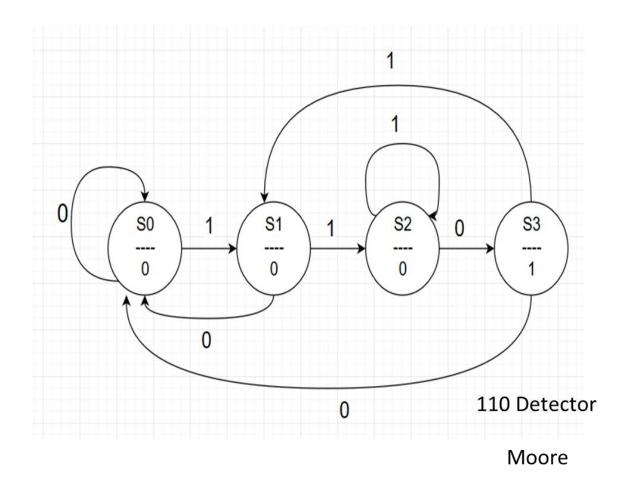

1011 Moore

11011 Mealy

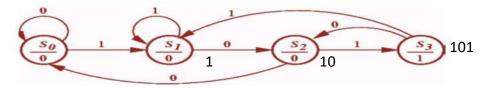

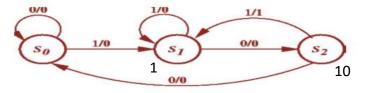

#### Construct a sequence detector for the sequence 101 using both mealy state machine and moore state machine

Moore state require to four states st0,st1,st2,st3 to detect the 101 sequence.

Mealy state machine require only three states st0,st1,st2 to detect the 101 sequence.

| Present State | Next State |      | Output |      |

|---------------|------------|------|--------|------|

|               | IN=0       | IN=1 | IN=0   | IN=1 |

| q             | Q          | Q    | Q      | Q    |

| а             | а          | b    | 0      | 1    |

| b             | В          | b    | 1      | 0    |

| Present State | Next State |      | Output |      |

|---------------|------------|------|--------|------|

|               | IN=0       | IN=1 | IN=0   | IN=1 |

| q             | Q          | Q    | Q      | Q    |

| 0             | 0          | 1    | 0      | 1    |

| 1             | 1          | 1    | 1      | 0    |

а

b

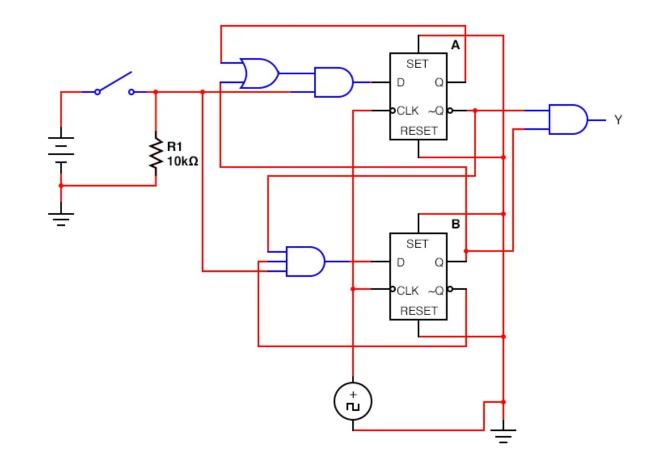

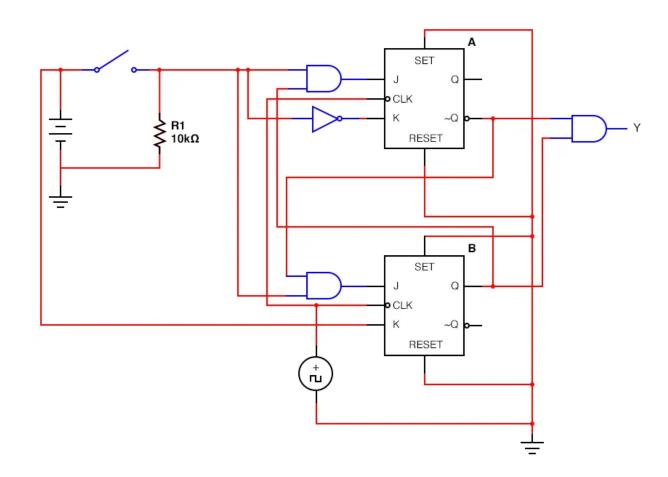

| Curren | t State | Input | Next  | Outputs |   |

|--------|---------|-------|-------|---------|---|

| Α      | В       | I     | Anext | Bnext   | Y |

| 0      | 0       | 0     | 0     | 0       | 0 |

| 0      | 0       | 1     | 0     | 1       | 0 |

| 0      | 1       | 0     | 0     | 0       | 1 |

| 0      | 1       | 1     | 1     | 0       | 1 |

| 1      | 0       | 0     | 0     | 0       | 0 |

| 1      | 0       | 1     | 1     | 0       | 0 |

| 1      | 1       | 0     | Х     | Х       | Х |

| 1      | 1       | 1     | Х     | Х       | Х |

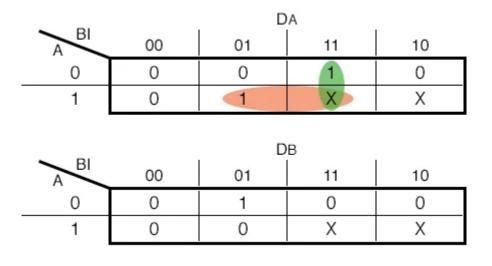

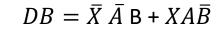

| Currer | nt State | Input | Next  | State | Outputs | Flip Flo | Flip Flop Inputs |  |

|--------|----------|-------|-------|-------|---------|----------|------------------|--|

| Α      | В        | I     | Anext | Bnext | Y       | DA       | DB               |  |

| 0      | 0        | 0     | 0     | 0     | 0       | 0        | 0                |  |

| 0      | 0        | 1     | 0     | 1     | 0       | 0        | 1                |  |

| 0      | 1        | 0     | 0     | 0     | 1       | 0        | 0                |  |

| 0      | 1        | 1     | 1     | 0     | 1       | 1        | 0                |  |

| 1      | 0        | 0     | 0     | 0     | 0       | 0        | 0                |  |

| 1      | 0        | 1     | 1     | 0     | 0       | 1        | 0                |  |

| 1      | 1        | 0     | Х     | Х     | Х       | Х        | Х                |  |

| 1      | 1        | 1     | Х     | Х     | Х       | Х        | Х                |  |

| Q | Q <sub>next</sub> | J | Κ |

|---|-------------------|---|---|

| 0 | 0                 | 0 | Х |

| 0 | ,                 | 1 | X |

|   | 0                 | X | 1 |

|   |                   | X | 0 |

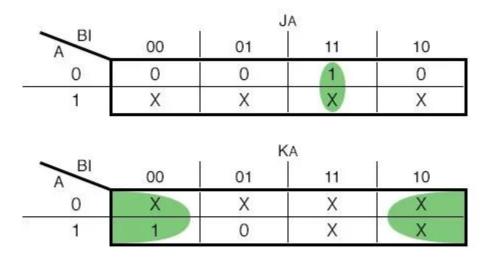

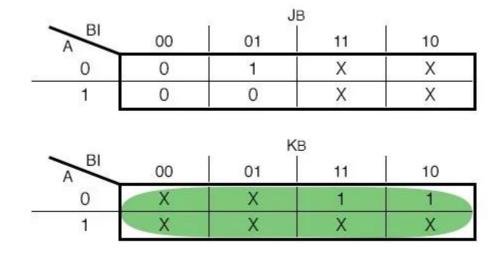

| Current State Input |   |   | Next  | State | Output | Flip Flop Inputs |    |    |    |  |

|---------------------|---|---|-------|-------|--------|------------------|----|----|----|--|

| Α                   | В | 1 | Anext | Bnext | Ŷ      | JA               | KA | JB | KB |  |

| 0                   | 0 | 0 | 0     | 0     | 0      | 0                | Х  | 0  | Х  |  |

| 0                   | 0 | 1 | 0     | 1     | 0      | 0                | Х  | 1  | Х  |  |

| 0                   | 1 | 0 | 0     | 0     | 1      | 0                | Х  | Х  | 1  |  |

| 0                   | 1 | 1 | 1     | 0     | 1      | 1                | Х  | Х  | 1  |  |

| 1                   | 0 | 0 | 0     | 0     | 0      | Х                | 1  | 0  | Х  |  |

| 1                   | 0 | 1 | 1     | 0     | 0      | Х                | 0  | 0  | Х  |  |

| 1                   | 1 | 0 | Х     | Х     | Х      | Х                | Х  | Х  | Х  |  |

| 1                   | 1 | 1 | Х     | Х     | Х      | Х                | Х  | Х  | Х  |  |

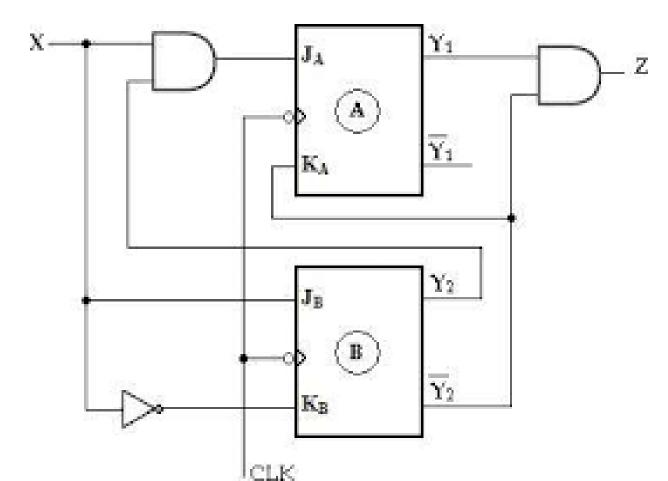

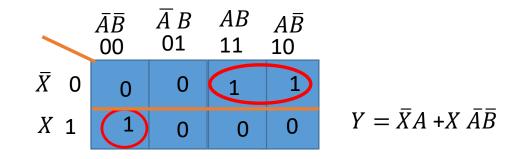

$$\begin{split} D_A &= A \cdot I + B \cdot I = (A + B) \cdot I \\ D_B &= \overline{A} \cdot \overline{B} \cdot I \end{split}$$

$$J_A = B \cdot I$$

$$K_A = \overline{I}$$

$$J_B = \overline{A} \cdot I$$

$$K_B = 1$$

$Y = \overline{A} \cdot B$

# Home Work

Solve previous question in other form

| Presen | it State | Next State<br>I=0 I=1 |   |   |   | Output |

|--------|----------|-----------------------|---|---|---|--------|

| Α      | В        | A                     | В | Α | B | Υ      |

| 0      | 0        |                       |   |   |   |        |

|        |          |                       |   |   |   |        |

|        |          |                       |   |   |   |        |

|        |          |                       |   |   |   |        |

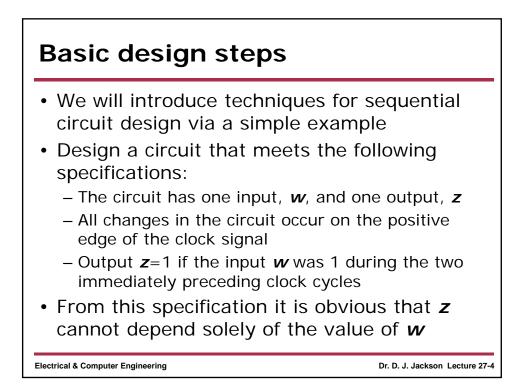

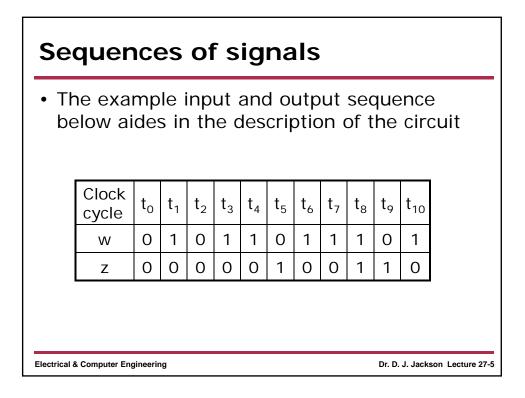

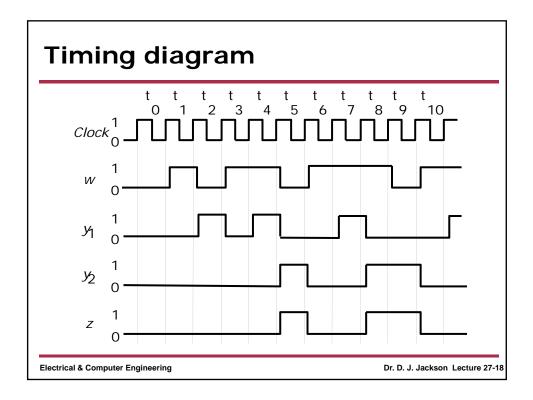

| Clock<br>Cycle | t0 | t1 | t2 | t3 | t4 | t5 | t6 | t7 | t8 | t9 | t10 |

|----------------|----|----|----|----|----|----|----|----|----|----|-----|

| W              | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1   |

| Z              | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0   |

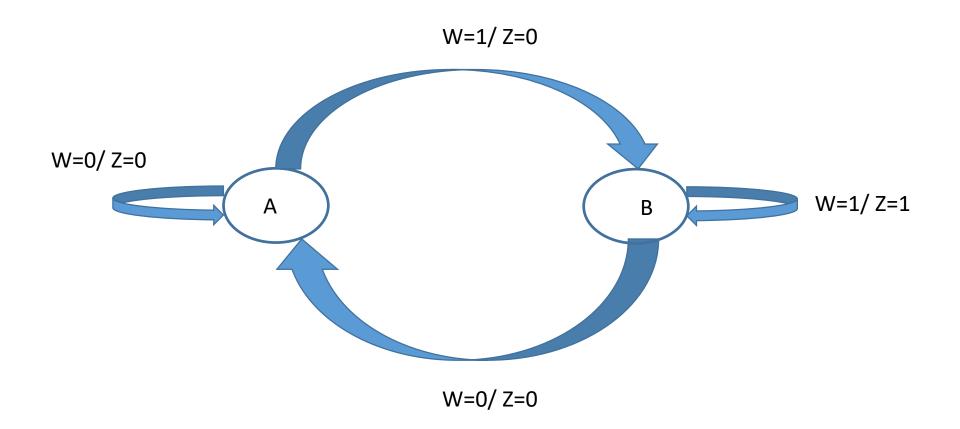

| Present State | Next State |     | Output |     |  |

|---------------|------------|-----|--------|-----|--|

|               | W=0        | W=1 | W=0    | W=1 |  |

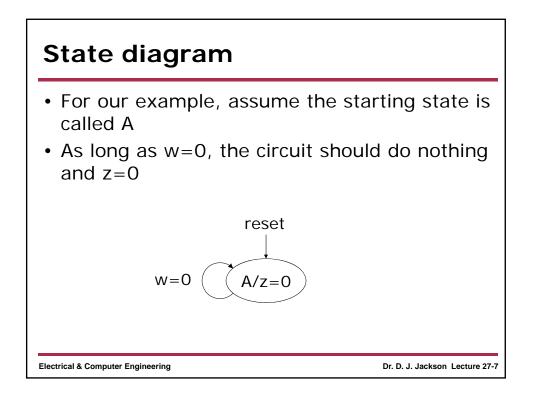

| A             | А          | В   | 0      | 0   |  |

| В             | А          | В   | 0      | 1   |  |

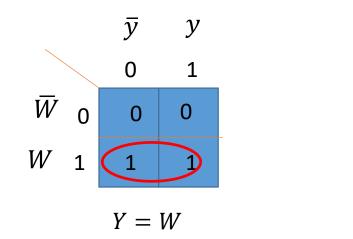

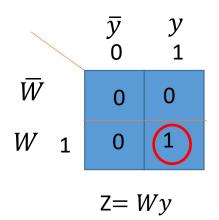

|   | Present State | Next | State | Output |     |  |

|---|---------------|------|-------|--------|-----|--|

|   |               | W=0  | W=1   | W=0    | W=1 |  |

|   | У             | Y    | Y     | Z      | Z   |  |

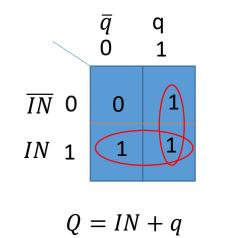

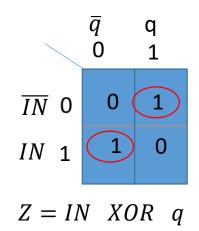

| А | 0             | 0    | 1     | 0      | 0   |  |

| В | 1             | 0    | 1     | 0      | 1   |  |

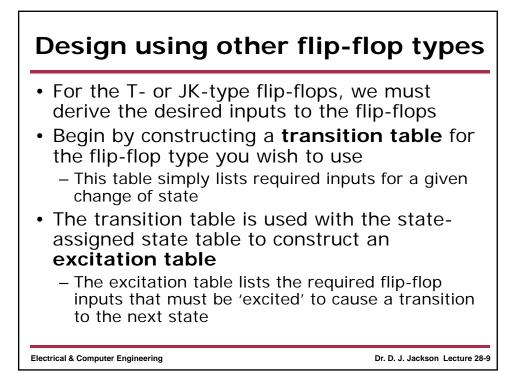

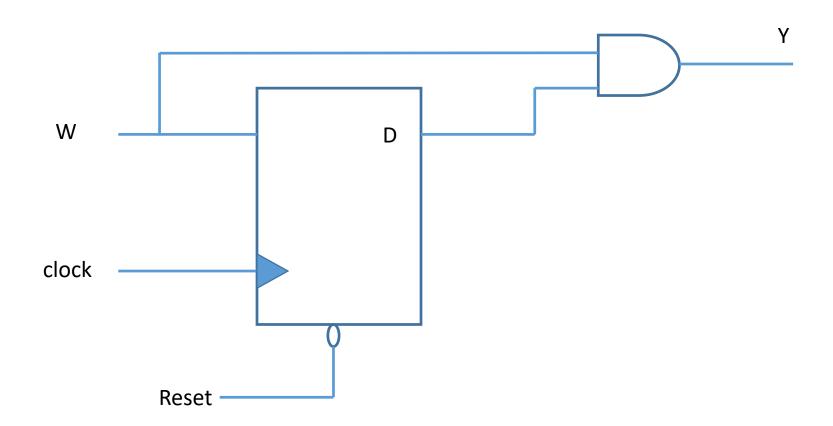

## **State Machine Design Procedure**

- 1. Build state/output table (or state diagram) from word description using state names.

- 2. Minimize number of states (optional).

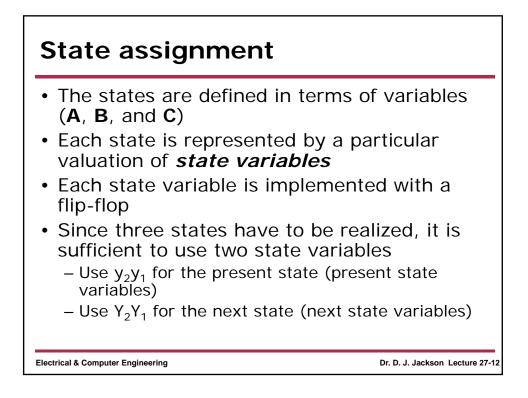

- 3. State Assignment: Choose state variables and assign bit combinations to named states.

- 4. Build transition/output table from state/output table (or state diagram) by substituting state variable combinations instead of state names.

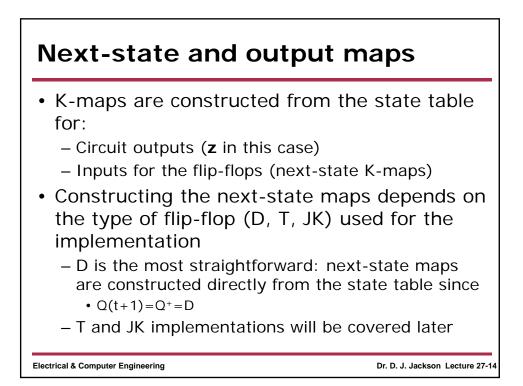

- 5. Choose flip-flop type (D, J-K, etc.)

- 6. Build excitation table for flip-flop inputs from transition table.

- 7. Derive excitation equations from excitation table.

- 8. Derive output equations from transition/output table.

- 9. Draw logic diagram with excitation logic, output logic, and state memory elements.

EECC341 - Shaaban

Lecture Seven

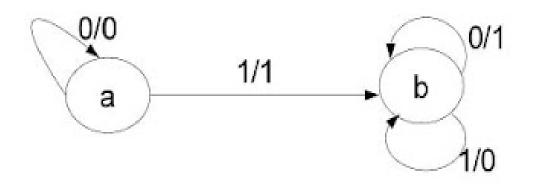

### Finite State Machines

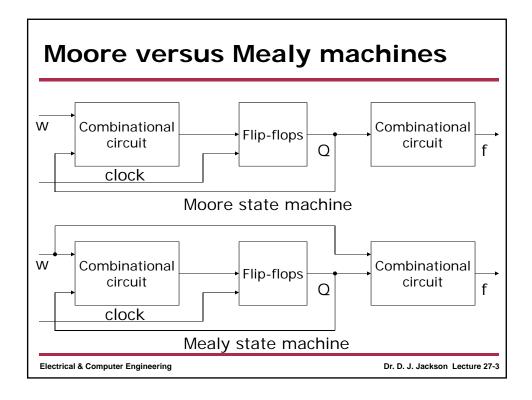

Two types of sequential circuits (or finite state machines)

#### Mealy machine

Output is function of present state and present input

#### Moore machine

Output is function of present state only

| Moore Circuit                                           | Mealy Circuit                                                                                  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------|

| a) Its output is a function of present state only.      | <ul> <li>a) Its output is a function of present state<br/>as well as present input.</li> </ul> |

| <ul> <li>b) Input changes does not affect the</li></ul> | <ul> <li>b) Input changes may affect the output of</li></ul>                                   |

| output.                                                 | the circuit.                                                                                   |

| <li>c) Moore circuit requires more number of</li>       | <li>c) It requires less number of states for</li>                                              |

| states for implementing same function.                  | implementing same function.                                                                    |

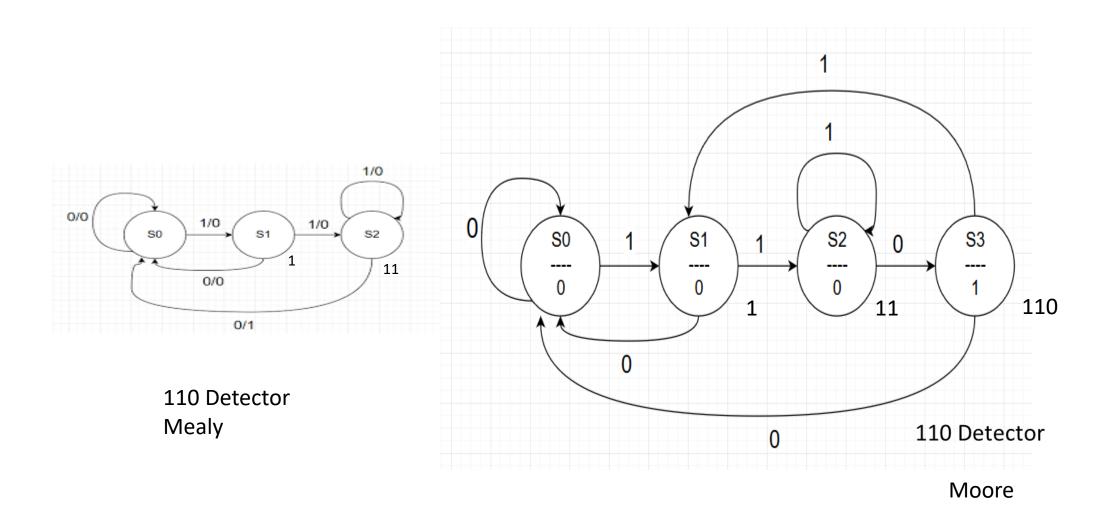

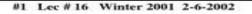

Example:-

State machine design 110 Mealy?

110 Detector Mealy

| Present State | Next | State | Output |     |  |

|---------------|------|-------|--------|-----|--|

|               | E=0  | E=1   | E=0    | E=1 |  |

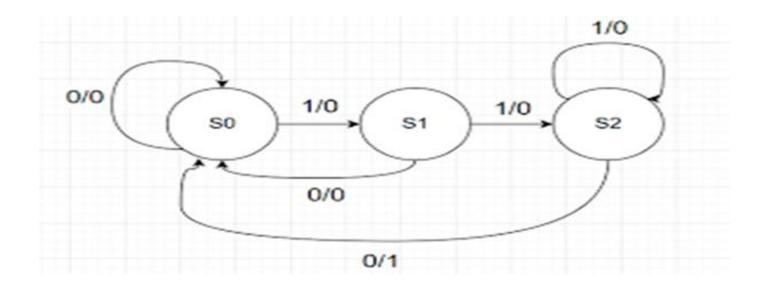

| S0            | S0   | S1    | 0      | 0   |  |

| S1            | S0   | S2    | 0      | 0   |  |

| S2            | SO   | S2    | 1      | 0   |  |

| Present State |    |     | Ne | ext St | ate | Output |     |  |

|---------------|----|-----|----|--------|-----|--------|-----|--|

| Y2            | Y1 | E=0 | )  | E=1    | L   | E=0    | E=1 |  |

|               |    | Y2  | Y1 | Y2     | Y1  | Z      | Z   |  |

| 0             | 0  | 0   | 0  | 0      | 1   | 0      | 0   |  |

| 0             | 1  | 0   | 0  | 1      | 0   | 0      | 0   |  |

| 1             | 0  | 0   | 0  | 1      | 0   | 1      | 0   |  |

| 1             | 1  | d   | d  | d      | d   | d      | d   |  |

Y1 = EY1 + EY2

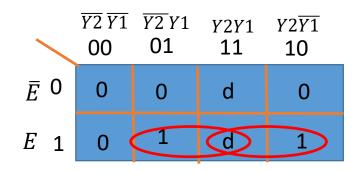

$Y2 = E\overline{Y2}\,\overline{Y1}$

Home Work Draw circuit Diagram

| Present State |     | Next State | Output |

|---------------|-----|------------|--------|

|               | E=0 | E=1        | Z      |

| S0            | S0  | S1         | 0      |

| S1            | S0  | S2         | 0      |

| S2            | S3  | S2         | 0      |

| S3            | S0  | S1         | 1      |

| Present | State | Nex | t State |    |    | Output |

|---------|-------|-----|---------|----|----|--------|

| Y2      | Y1    | E=0 |         | E  | =1 |        |

|         |       | Y2  | Y1      | Y2 | Y1 | Z      |

| 0       | 0     | 0   | 0       | 0  | 1  | 0      |

| 0       | 1     | 0   | 0       | 1  | 0  | 0      |

| 1       | 0     | 1   | 1       | 1  | 0  | 0      |

| 1       | 1     | 0   | 0       | 0  | 1  | 1      |

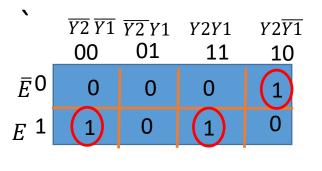

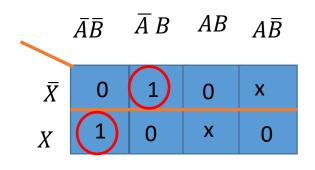

$Y1 = EY2Y1 + E\overline{Y2} \ \overline{Y1} + \ \overline{E} \ Y2\overline{Y1}$

| $\overline{Y2} \overline{Y1}$ | <u>72</u> Y1 | Y2Y1 | $Y2\overline{Y1}$ |

|-------------------------------|--------------|------|-------------------|

| 00                            | 01           | 11   | 10                |

| Ē00                           | 0            | 0    |                   |

| <i>E</i> 1 0                  |              | 0    | 1                 |

$Y2 = E\overline{Y2}Y1 + Y2\overline{Y1}$

Home Work Draw circuit Diagram Z = Y2Y1

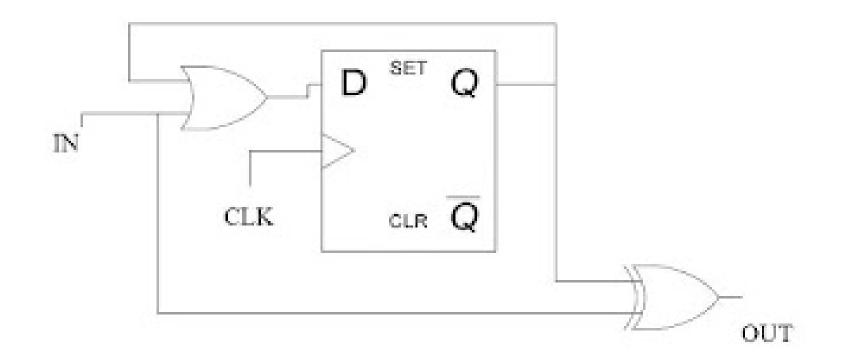

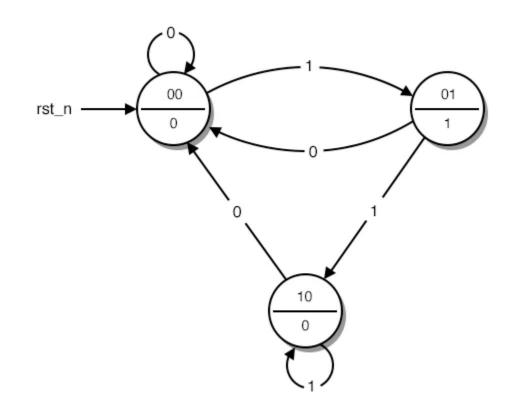

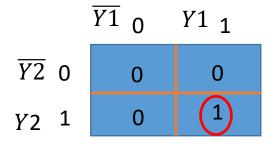

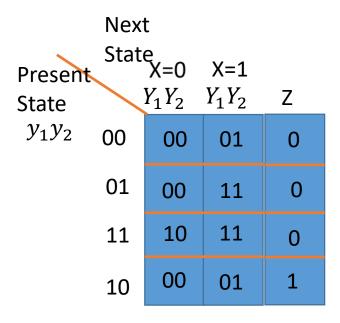

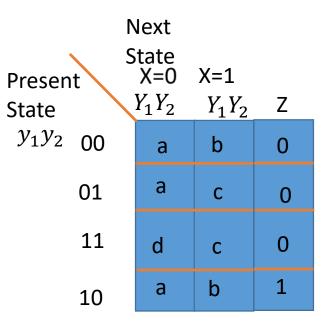

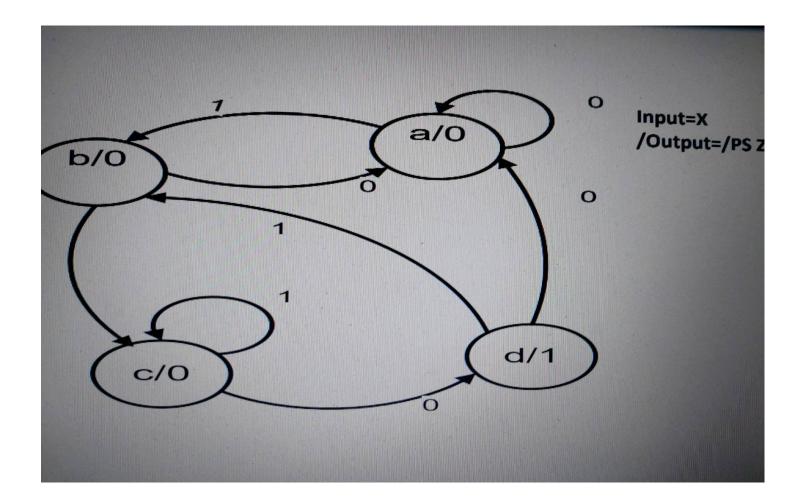

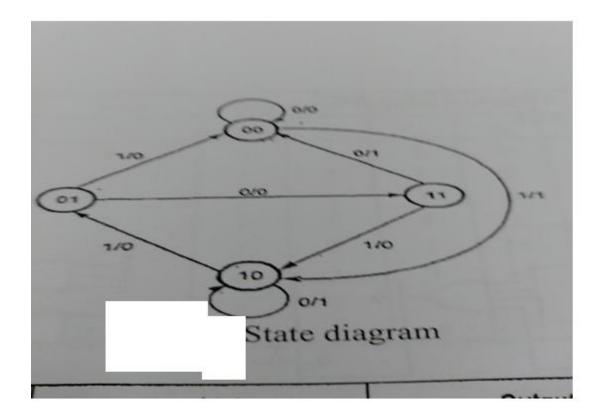

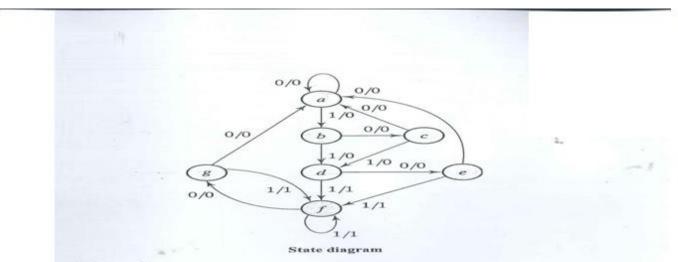

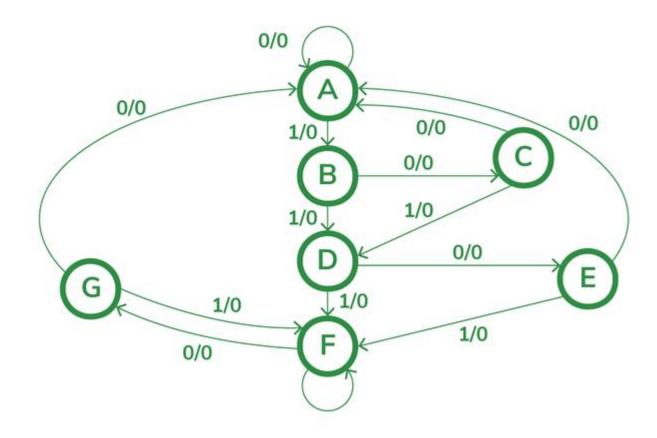

Analyze the circuit below to obtain its state diagram?

Fig3. Characteristic equation of JK flip flop

Solution:- $Y = Q = q.\,\overline{k} + \overline{q}.\,\mathsf{J}$  $J_{A} = y_{2} X$  $K_A = \overline{y_2}$  $Y_1 = \overline{y_1} \cdot J_A + y_1 \overline{k_A}$  $Y_1 = \overline{y_1} \cdot y_2 \cdot X + y_1 y_2$  $J_B = X$  $K_R = \overline{X}$  $Y_2 = \overline{y_2} \cdot J_B + y_2 \overline{k_B}$  $Y_2 = \overline{y_2} \cdot X + y_2 X$  $Z = y_1 \cdot \overline{y_2}$

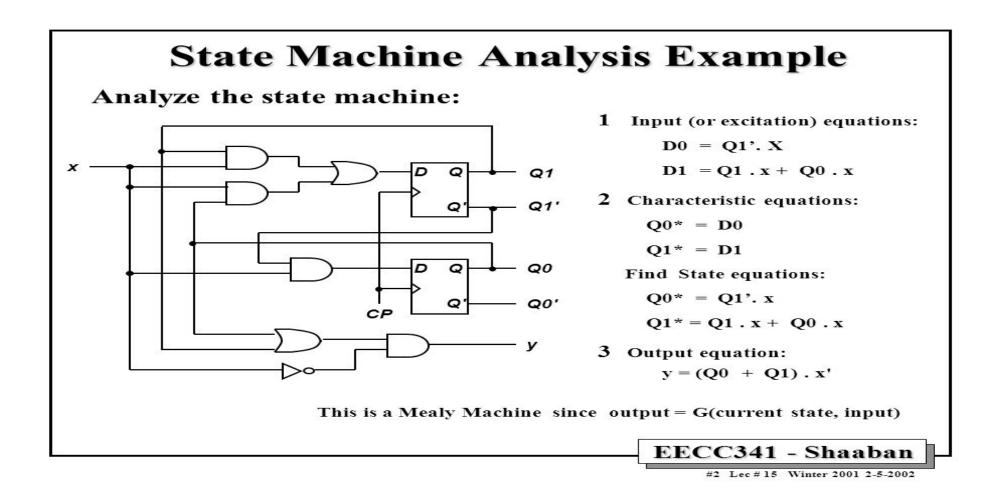

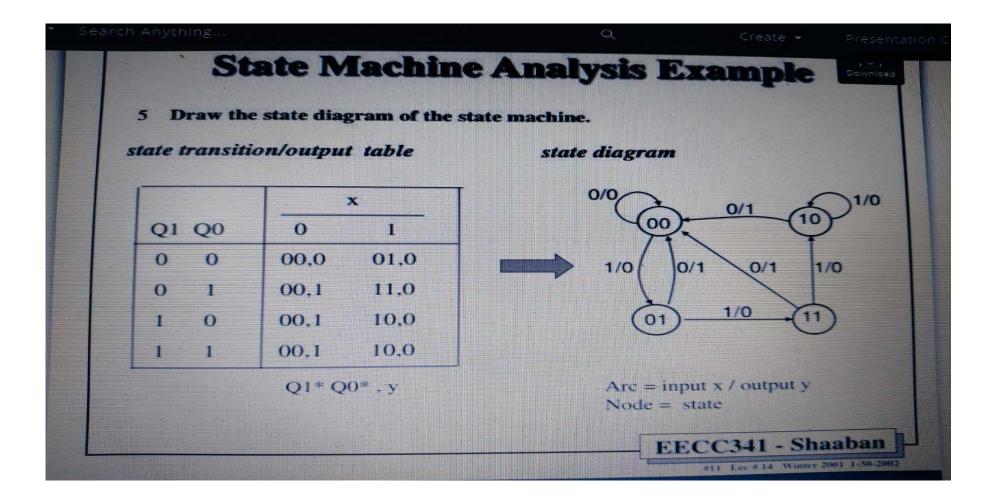

#### **State Machine Analysis**

From the state equation and output equation, construct the state transition – output table.

State Equation

$$Q_0^* = Q_1 \quad .x$$

$Q_1^* = Q_1 . x + Q_0 . x$ Output Equation  $y = (Q_0 + Q_1) . \bar{x}$

| $Q_1$ | $Q_0$ | x=0             | <b>x=1</b>                                      |  |

|-------|-------|-----------------|-------------------------------------------------|--|

|       |       | $Q_1^* Q_0^* y$ | $Q_1^* \hspace{0.1 cm} Q_0^* \hspace{0.1 cm} y$ |  |

| 0     | 0     | 0 0 0           | 0 1 0                                           |  |

| 0     | 1     | 0 0 1           | 1 1 0                                           |  |

| 1     | 0     | 0 0 1           | 1 0 0                                           |  |

| 1     | 1     | 0 0 1           | 1 0 0                                           |  |

Lecture eight

# D Flip-Flop

| Present State |   | Next | State | Output |     |  |

|---------------|---|------|-------|--------|-----|--|

|               |   |      | X=1   | X=0    | X=1 |  |

| А             | В | AB   | AB    | Y      | Y   |  |

| 0             | 0 | 00   | 10    | 0      | 1   |  |

| 0             | 1 | 11   | 00    | 0      | 0   |  |

| 1             | 0 | 10   | 01    | 1      | 0   |  |

| 1             | 1 | 00   | 10    | 1      | 0   |  |

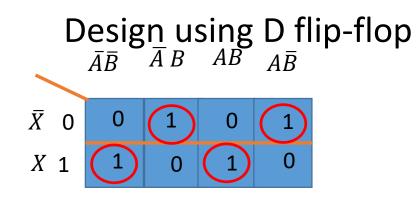

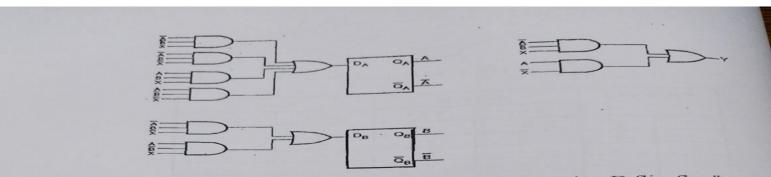

### D Flip-Flop

|            | $ar{A}ar{B}$ 00 | $\overline{A} B \\ 01$ | <i>AB</i><br>11 | $A\overline{B}$ 10 |

|------------|-----------------|------------------------|-----------------|--------------------|

| <i>X</i> 0 | 0               |                        | 0               | 0                  |

| X 1        | 0               | 0                      | 0               |                    |

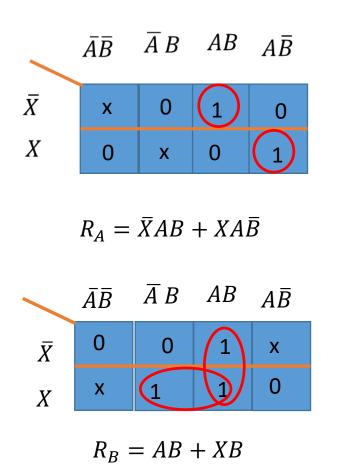

$DA = \overline{X} \overline{A} B + \overline{X} A \overline{B} + X \overline{A} \overline{B} + XAB$

"Logic diagram of given sequential circuit using D flip-flop"

#### ii) Design using T flip- flops :

| Qn | Qn+1 | т   |

|----|------|-----|

| 0  | . 0  | 0 . |

| 0  | 1 3  | 1   |

| 1  | 0    | 1   |

| 1  | 1    | O   |

"Excitation table for T flip-flop"

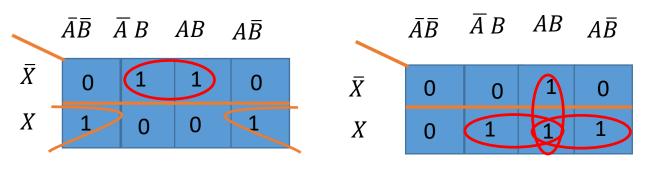

# T Flip-Flop

| Present st | ate | Input | Next State |   | Flip-flop Inputs |    | Output |

|------------|-----|-------|------------|---|------------------|----|--------|

| А          | В   | Х     | А          | В | ТА               | ТВ | Y      |

| 0          | 0   | 0     | 0          | 0 | 0                | 0  | 0      |

| 0          | 0   | 1     | 1          | 0 | 1                | 0  | 1      |

| 0          | 1   | 0     | 1          | 1 | 1                | 0  | 0      |

| 0          | 1   | 1     | 0          | 0 | 0                | 1  | 0      |

| 1          | 0   | 0     | 1          | 0 | 0                | 0  | 1      |

| 1          | 0   | 1     | 0          | 1 | 1                | 1  | 0      |

| 1          | 1   | 0     | 0          | 0 | 1                | 1  | 1      |

| 1          | 1   | 1     | 1          | 0 | 0                | 1  | 0      |

### T Flip-Flop

$TA = \overline{X} B + X\overline{B}$

Y as previous case in D flip-flop

## RS Flip-Flop

# RS Flip-Flop

| Present | State | Input | Next State |   | Flip flop Inputs |                |       |       | Output1 |

|---------|-------|-------|------------|---|------------------|----------------|-------|-------|---------|

| А       | В     | Х     | А          | В | $R_A$            | S <sub>A</sub> | $R_B$ | $S_B$ | Y       |

| 0       | 0     | 0     | 0          | 0 | х                | 0              | х     | 0     | 0       |

| 0       | 0     | 1     | 1          | 0 | 0                | 1              | х     | 0     | 1       |

| 0       | 1     | 0     | 1          | 1 | 0                | 1              | 0     | х     | 0       |

| 0       | 1     | 1     | 0          | 0 | х                | 0              | 1     | 0     | 0       |

| 1       | 0     | 0     | 1          | 0 | 0                | х              | х     | 0     | 1       |

| 1       | 0     | 1     | 0          | 1 | 1                | 0              | 0     | 1     | 0       |

| 1       | 1     | 0     | 0          | 0 | 1                | 0              | 1     | 0     | 1       |

| 1       | 1     | 1     | 1          | 0 | 0                | х              | 1     | 0     | 0       |

Circuit Excitation Table

### RS Flip-Flop

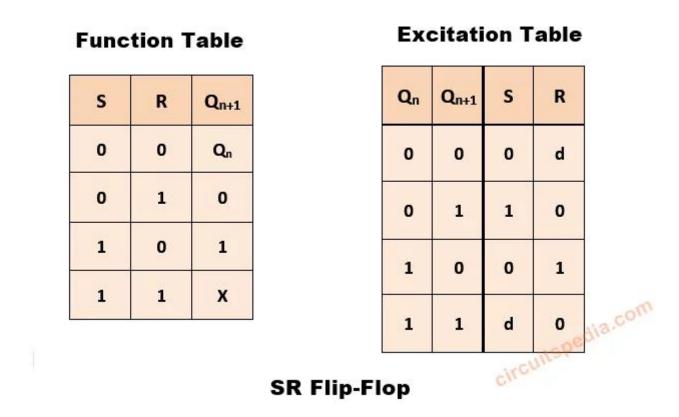

$S_A = \bar{X} \,\bar{A}B + X \bar{A}\bar{B}$

Home Work

Design using JK flip-flop?

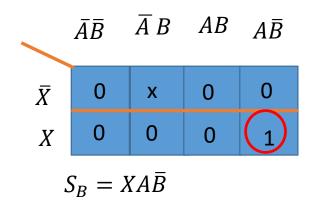

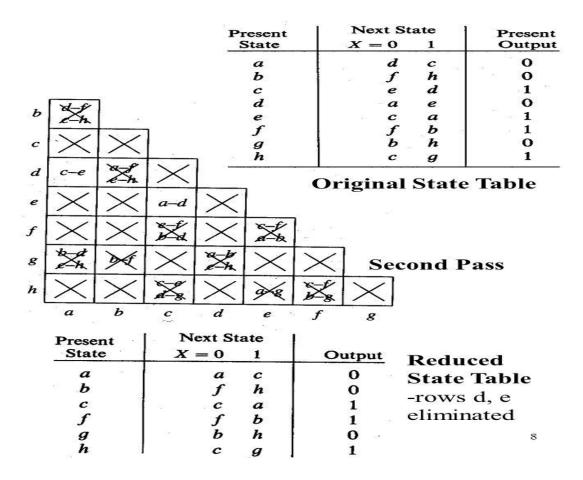

2- State table

|               | Next State |       | Output |              |  |

|---------------|------------|-------|--------|--------------|--|

| Present State | x = 0      | x = 1 | x = 0  | <i>x</i> = 1 |  |

| a             | a          | Ь     | 0      | 0            |  |

| b             | 0          | d     | 0      | 0            |  |

| C             | a          | d     | 0      | 0            |  |

| d             | e          | 5     | 0      | 1            |  |

| e             | 0          | 5     | 0      | 1            |  |

| 5             | 8          | 5     | 0      | 1            |  |

| . 8           | a          | - 5   | 0      | 1            |  |

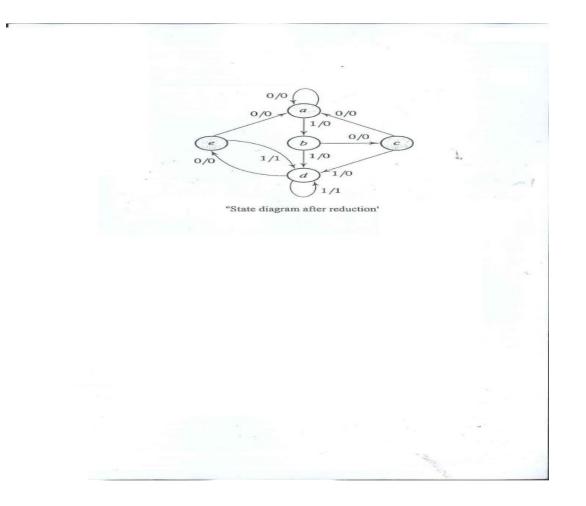

#### 3- Reducing the state table:

- e = g (remove g and keep e)

- d = f (remove f and keep d)

Reducing the State Table

|               | Next State |              | Output |       |

|---------------|------------|--------------|--------|-------|

| Present State | x = 0      | <i>x</i> = 1 | x = 0  | x = 1 |

| a             | a          | ь            | 0      | 0     |

| b             | c          | d            | 0      | 0     |

| C             | a          | d            | 0      | 0     |

| d             | e          | 5            | 0      | 1     |

| e             | a          | ſ            | 0      | 1     |

| 5             | e          | 5            | 0      | 1     |

#### Reduced State Table

|               | Next State |       | Output |       |

|---------------|------------|-------|--------|-------|

| Present State | x = 0      | x = 1 | x = 0  | x = 1 |

| a             | a          | Ь     | 0      | 0     |

| b             | c          | d     | 0      | 0     |

| c             | a          | d     | 0      | 0     |

| d             | e          | d     | 0      | I     |

| e             | a .        | d     | 0      | 1     |

|               |            |       |        |       |

|               |            |       |        |       |

|               |            |       |        |       |

|               |            |       |        |       |

|               | -          |       |        |       |

|               |            |       |        |       |

|               |            |       |        |       |

Lecture Nine

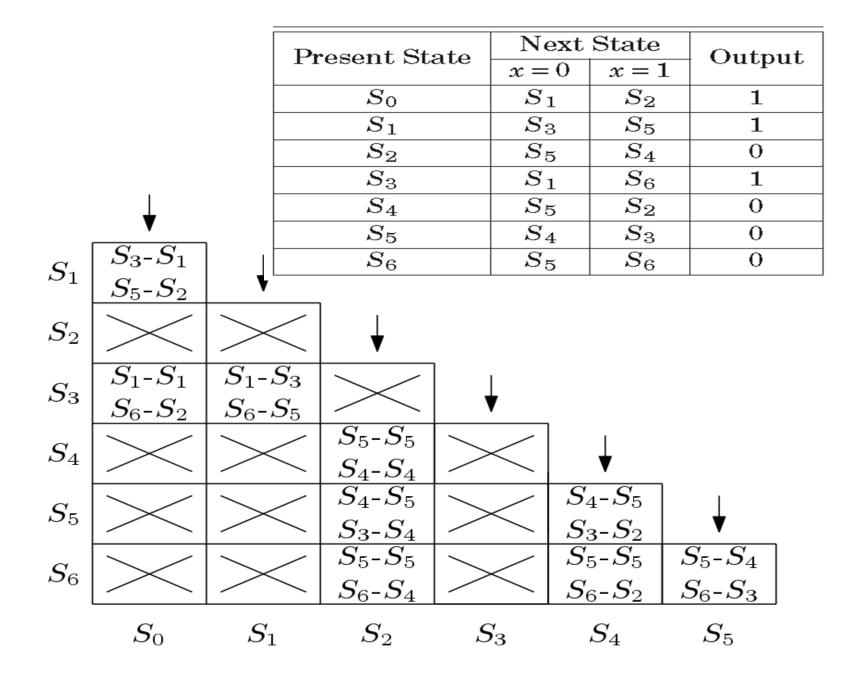

State Reduction

- Inspection

- Implication Table

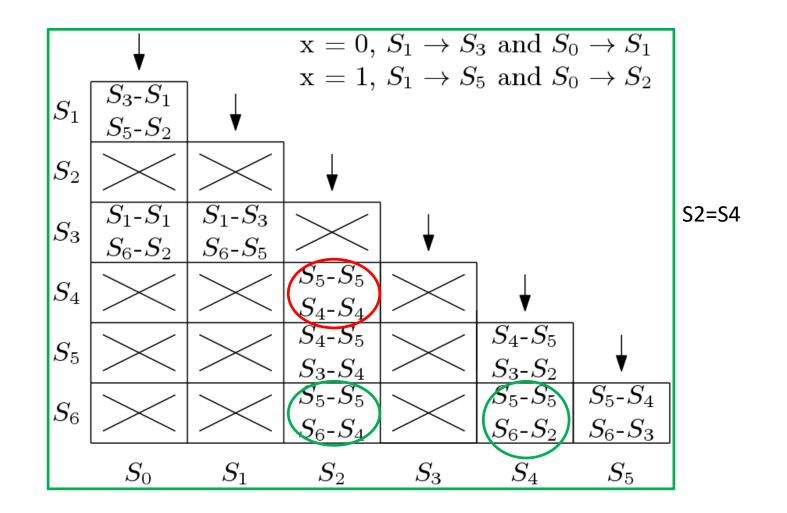

Example (1)

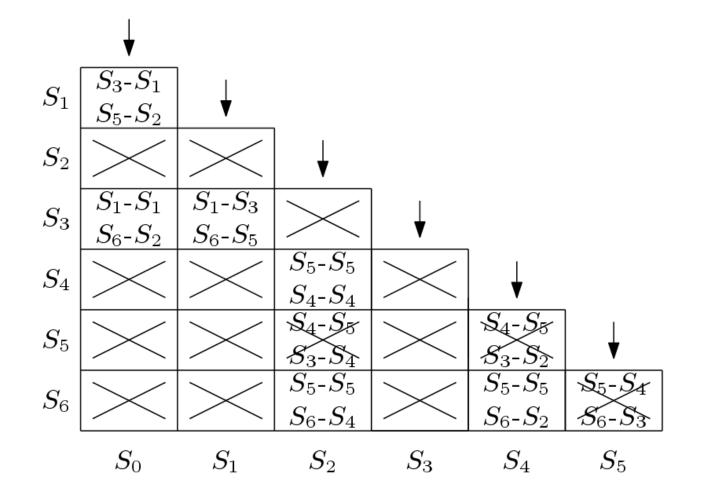

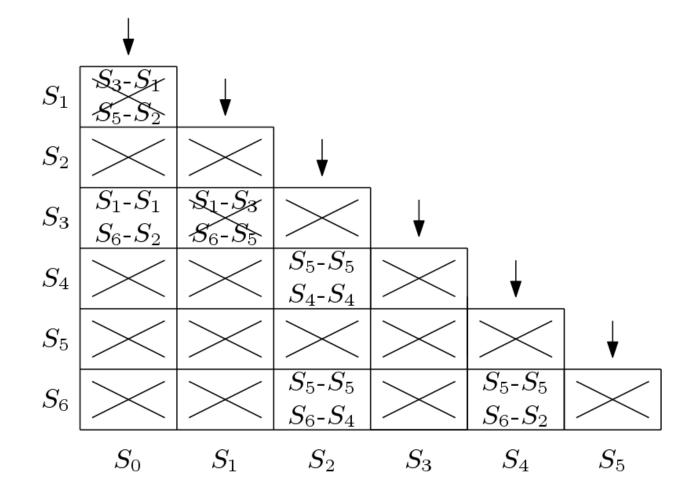

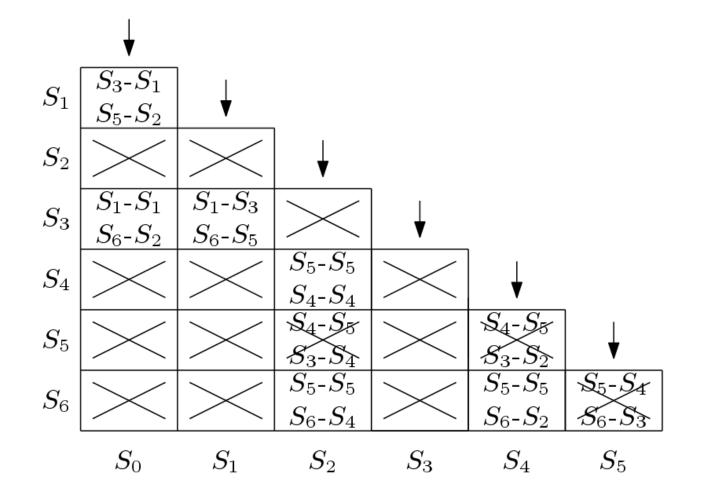

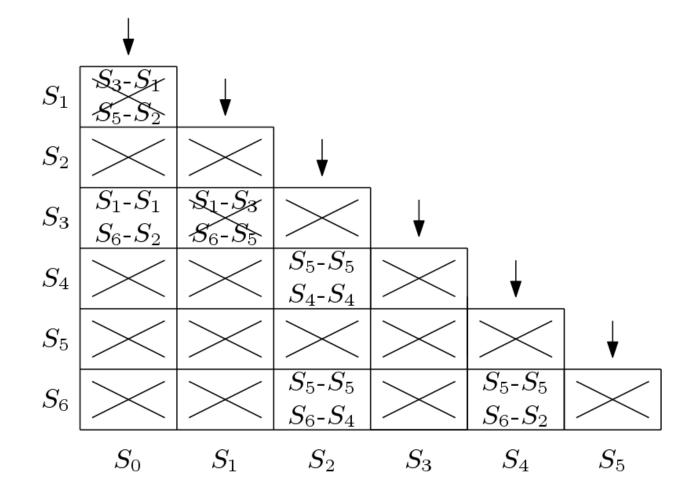

Reduce the number of states for table shown below using Implication table method?

| Ducaset State | Next  | State | Outrast |

|---------------|-------|-------|---------|

| Present State | x = 0 | x = 1 | Output  |

| $S_0$         | $S_1$ | $S_2$ | 1       |

| $S_1$         | $S_3$ | $S_5$ | 1       |

| $S_2$         | $S_5$ | $S_4$ | 0       |

| $S_3$         | $S_1$ | $S_6$ | 1       |

| $S_4$         | $S_5$ | $S_2$ | 0       |

| $S_5$         | $S_4$ | $S_3$ | 0       |

| $S_6$         | $S_5$ | $S_6$ | 0       |

| Present State | Next    | State   | Output |  |

|---------------|---------|---------|--------|--|

| riesent State | x = 0   | x = 1   | Output |  |

| $S_0^*$       | $S_1$   | $S_2$   | 1      |  |

| $S_1$         | $S_0^*$ | $S_5$   | 1      |  |

| $S_2^*$       | $S_5$   | $S_2^*$ | 0      |  |

| $S_5$         | $S_2^*$ | $S_0^*$ | 0      |  |

## Example (2)

## Inspection Method

| Present State | Next    | Present Output |   |

|---------------|---------|----------------|---|

|               | X=0 X=1 |                |   |

| а             | d       | С              | 0 |

| b             | d       | с              | 0 |

| с             | d       | а              | 0 |

| d             | d       | с              | 1 |

| Present state | Next Sstate |   | Output |

|---------------|-------------|---|--------|

|               | X=0 X=1     |   |        |

| а             | d           | С | 0      |

| С             | d           | а | 0      |

| d             | d           | С | 1      |

| Present State | Next State<br>X=0 X=1 |   | Output |

|---------------|-----------------------|---|--------|

| а             | d                     | а | 0      |

| d             | d                     | а | 1      |

## Example (3)

## Inspection Method

| Present State | Next State |     | Output |     |

|---------------|------------|-----|--------|-----|

|               | X=0        | X=1 | X=0    | X=1 |

|               |            |     |        |     |

| A             | В          | С   | 0      | 1   |

| В             | В          | А   | 0      | 1   |

| C             | D          | В   | 1      | 0   |

| D             | D          | А   | 0      | 1   |

| Present State | Next State |     | Output | Output |  |  |

|---------------|------------|-----|--------|--------|--|--|

|               | X=0        | X=1 | X=0    | X=1    |  |  |

| Α             | В          | С   | 0      | 1      |  |  |

| В             | В          | A   | 0      | 1      |  |  |

| C             | В          | В   | 1      | 0      |  |  |

| Present State | Next  | State        | Output |

|---------------|-------|--------------|--------|

| Fresent State | x = 0 | <i>x</i> = 1 | Output |

| $S_0$         | $S_1$ | $S_2$        | 1      |

| $S_1$         | $S_3$ | $S_5$        | 1      |

| $S_2$         | $S_5$ | $S_4$        | 0      |

| $S_3$         | $S_1$ | $S_6$        | 1      |

| $S_4$         | $S_5$ | $S_2$        | 0      |

| $S_5$         | $S_4$ | $S_3$        | 0      |

| $S_6$         | $S_5$ | $S_6$        | 0      |

| Present State | Next    | State   | Output |  |

|---------------|---------|---------|--------|--|

| riesent State | x = 0   | x = 1   | Output |  |

| $S_0^*$       | $S_1$   | $S_2$   | 1      |  |

| $S_1$         | $S_0^*$ | $S_5$   | 1      |  |

| $S_2^*$       | $S_5$   | $S_2^*$ | 0      |  |

| $S_5$         | $S_2^*$ | $S_0^*$ | 0      |  |

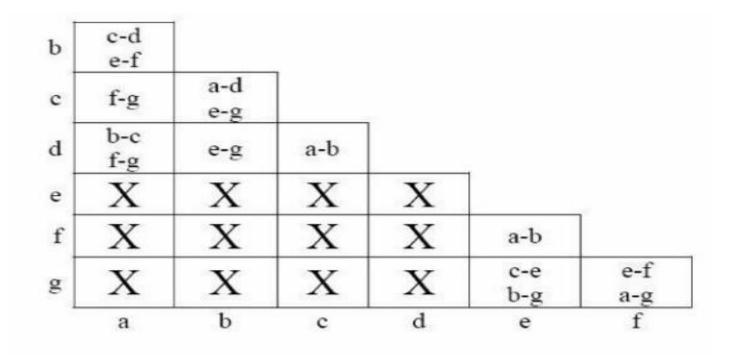

| Present<br>State | Next<br>X=0 |   | Present<br>X=0 | Output<br>X=1 |

|------------------|-------------|---|----------------|---------------|

| a                | c           | f | 0              | 0             |

| b                | d           | e | 0              | 0             |

| c                | ha          | g | 0              | 0             |

| d                | b           | g | 0              | 0             |

| e                | e           | b | 0              | 1             |

| f                | f           | a | 0              | 1             |

| g                | c           | g | 0              | 1             |

| h                | e           | £ | 0              | 0             |

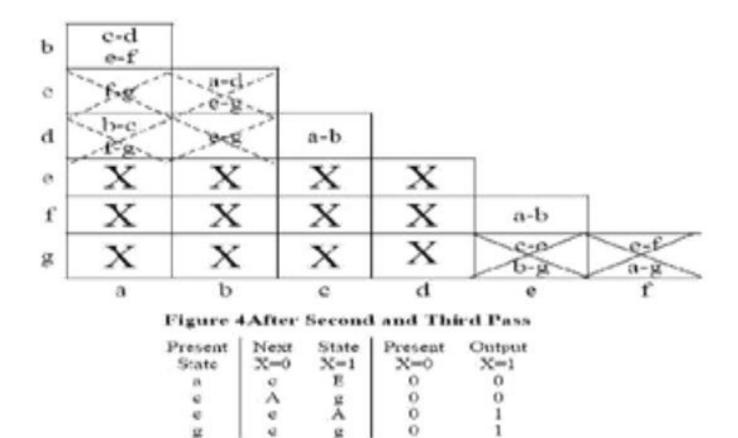

Figure 2 State Table Reduction by Row Matching

Figure 3 Implication Chart (First Pass)

**Figure 5 Final Reduced Table**

|   | Present State | Next State |     | Output |     |

|---|---------------|------------|-----|--------|-----|

|   |               | X=0        | X=1 | X=0    | X=1 |

|   | A             | А          | В   | 0      | 0   |

|   | В             | С          | D   | 0      | 0   |

|   | C             | А          | D   | 0      | 0   |

|   | D             | E          | F   | 0      | 1   |

| < | E             | А          | F   | 0      | 1   |

|   | F             | G          | F   | 0      | 1   |

| < | G             | А          | F   | 0      | 1   |

E=G , delet G Substitute each G by E Then D=F, delet F Substitute each F by D

| Present State | Next State |     | Output | Output |  |  |

|---------------|------------|-----|--------|--------|--|--|

|               | X=0        | X=1 | X=0    | X=1    |  |  |

| A             | А          | В   | 0      | 0      |  |  |

| В             | С          | D   | 0      | 0      |  |  |

| С             | А          | D   | 0      | 0      |  |  |

| D             | E          | D   | 0      | 1      |  |  |

| E             | А          | D   | 0      | 1      |  |  |

|               |            |     |        |        |  |  |