University Of Diyala College Of Engineering Computer Engineering Department

1

# Digital System Design II

Dr. Yasir Amer Al-Zubaidi Third stage 2021

### Design of Digital Sequential Circuits Using New Methods *Microprogramming Overview*

- Data path and Control

- Microoperations

- Sequencing and control

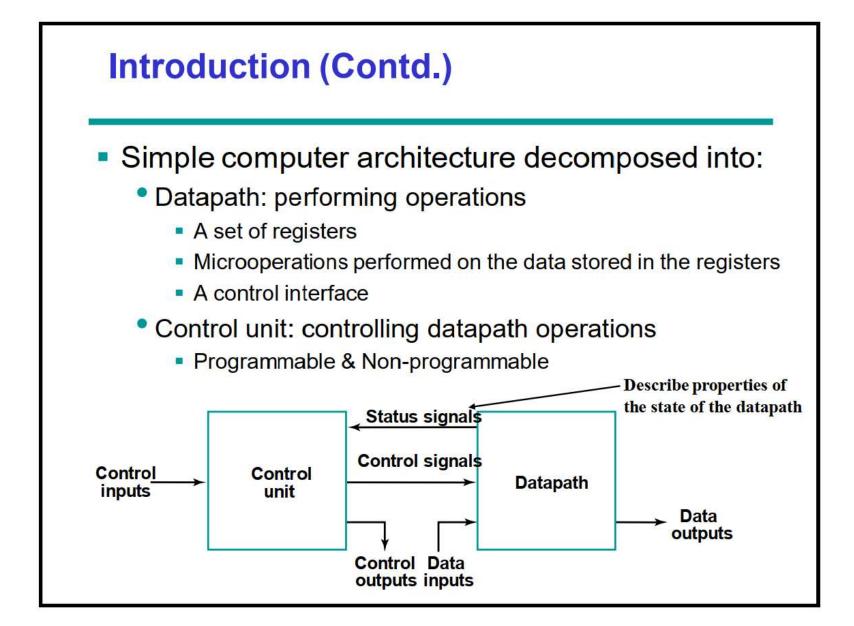

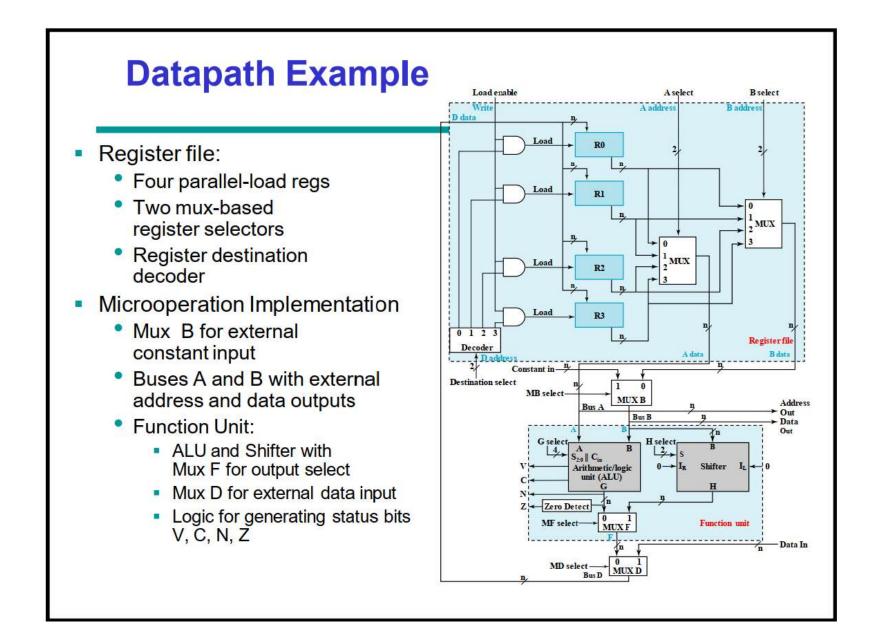

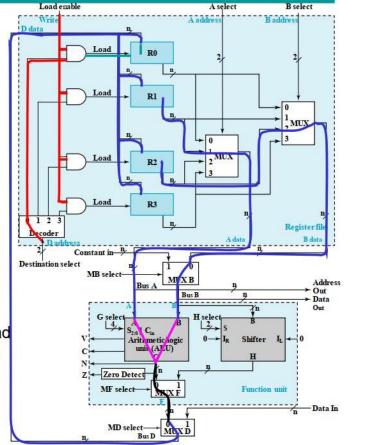

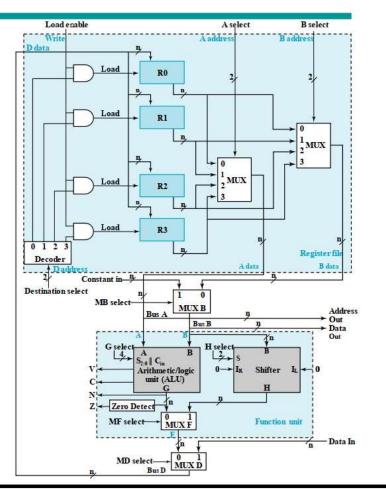

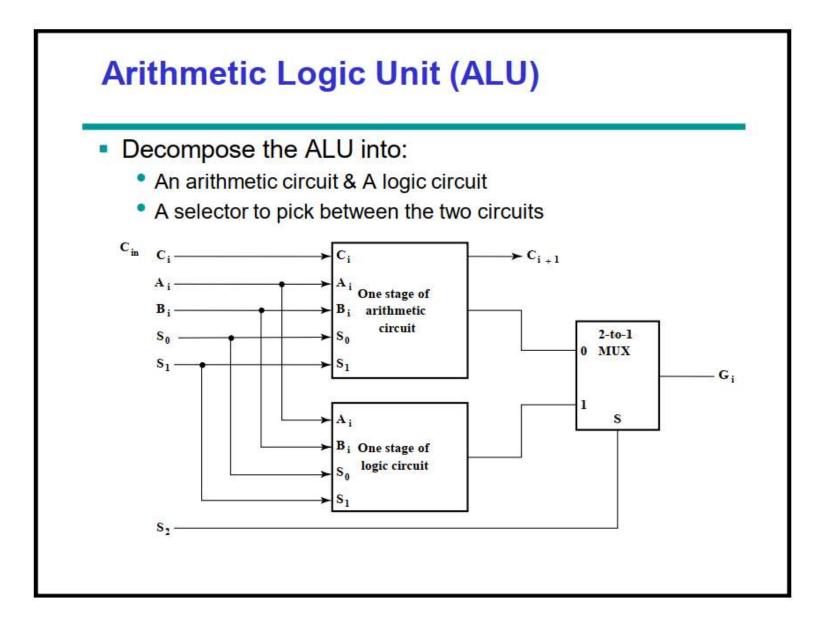

#### **Datapath and Control**

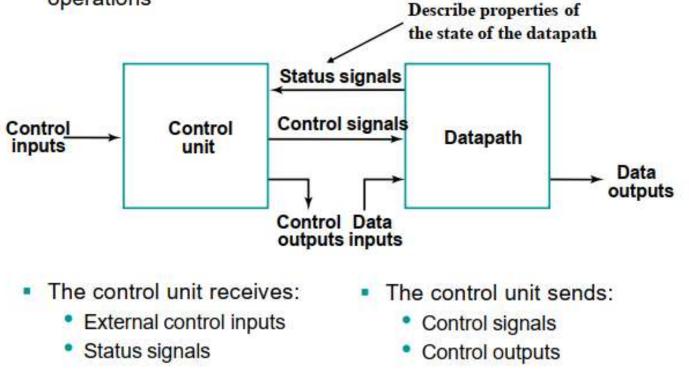

- Datapath performs data transfer and processing operations

- Control Unit Determines the enabling and sequencing of the operations

#### Overview

- Datapath and control

- Microoperations

- Register transfer operations

- Microoperations arithmetic, logic, and shift

- Register cell design

- Serial transfers and microoperations

- Sequencing and control

# **Register Transfer Operations**

- Register Transfer Operations the movement and processing of data stored in registers

- Three basic components:

- A set of registers (operands)

- Transfer operations

- Control of operations

- Elementary operations -- called microoperations

- Ioad, count, shift, add, bitwise "OR", etc.

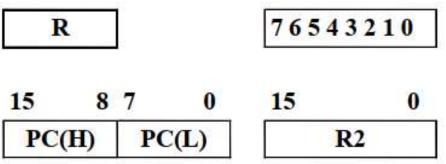

#### **Register Notation**

- Letters and numbers register (e.g. R2, PC, IR)

- Parentheses () range of register bits (e.g. R1(1), PC(7:0), AR(L))

- Arrow ( $\leftarrow$ ) data transfer (ex. R1  $\leftarrow$  R2, PC(L)  $\leftarrow$  R0)

- Brackets [] Specifies a memory address (ex. R0 ← M[AR], R3 ← M[PC] )

- Comma separates parallel operations

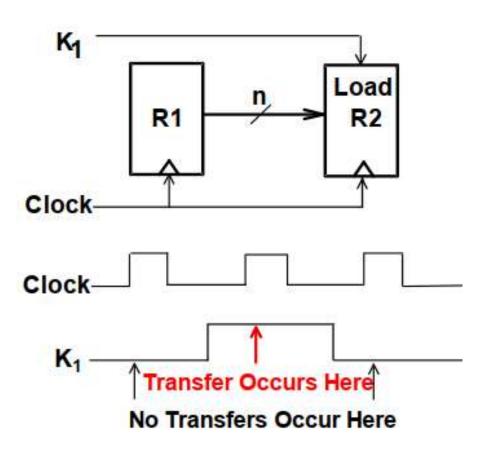

#### **Conditional Transfer**

If (K<sub>1</sub> =1) then (R2 ← R1)

⇔ K<sub>1</sub>: (R2 ← R1)

where K<sub>1</sub> is a control expression specifying a conditional execution of the microoperation.

## **Microoperations**

- Logical groupings:

- Transfer move data from one set of registers to another

- Arithmetic perform arithmetic on data in registers

- Logic manipulate data or use bitwise logical operations

- Shift shift data in registers

Arithmetic operations

- + Addition

- Subtraction

- \* Multiplication

- / Division

Logical operations ∨ Logical OR ∧ Logical AND ⊕ Logical Exclusive OR Not

# **Example Microoperations**

- R1← R1 + R2

- Add the content of R1 to the content of R2 and place the result in R1.

- PC ← R1 \* R6

- R1  $\leftarrow$  R1  $\oplus$  R2

- (K1 + K2): R1 ← R1 ∨ R3

- On condition K1 <u>OR</u> K2, the content of R1 is <u>Logic bitwise</u> <u>Ored</u> with the content of R3 and the result placed in R1.

- NOTE: "+" (as in K<sub>1</sub> + K<sub>2</sub>) means "OR." In R1 ← R1 + R2, + means "plus."

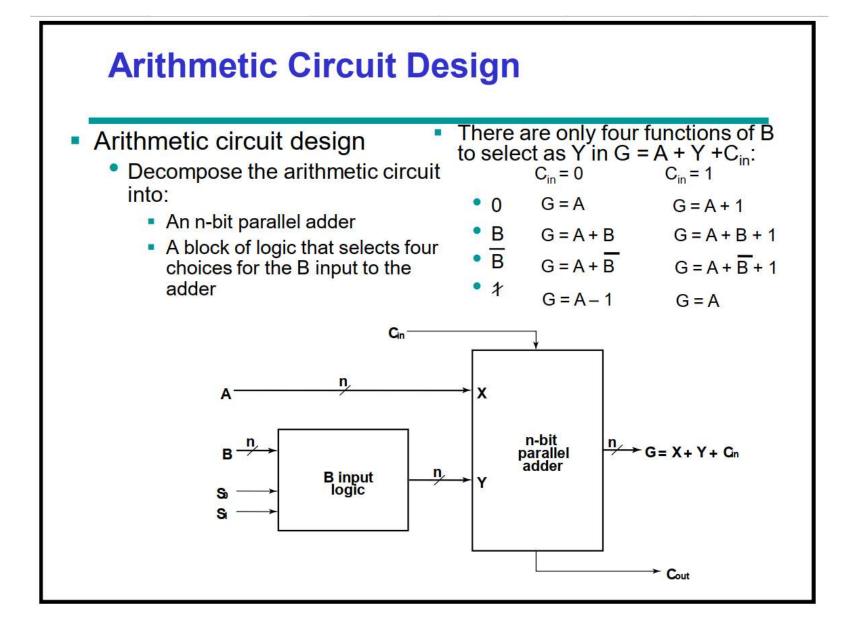

# **Arithmetic Microoperations**

| Symbolic Designation                   | Description             |  |

|----------------------------------------|-------------------------|--|

| $R0 \leftarrow R1 + R2$                | Addition                |  |

| $R0 \leftarrow \overline{R1}$          | <b>Ones Complement</b>  |  |

| $R0 \leftarrow \overline{R1} + 1$      | <b>Two's Complement</b> |  |

| $R0 \leftarrow R2 + \overline{R1} + 1$ | R2 minus R1 (2's Comp)  |  |

| $R1 \leftarrow R1 + 1$                 | Increment (count up)    |  |

| $R1 \leftarrow R1 - 1$                 | Decrement (count down)  |  |

- Any register may be specified for source 1, source 2, or destination.

- These simple microoperations operate on the whole word

# **Logical Microoperations**

| Symbolic<br>Designation                                    | Description               |  |

|------------------------------------------------------------|---------------------------|--|

| $R0 \leftarrow \overline{R1}$                              | Bitwise NOT               |  |

| $R0 \leftarrow R1 \lor R2$                                 | Bitwise OR (sets bits)    |  |

| $R0 \leftarrow R1 \land R2$                                | Bitwise AND (clears bits) |  |

| $R0 \leftarrow R1 \oplus R2$ Bitwise EXOR (complements bit |                           |  |

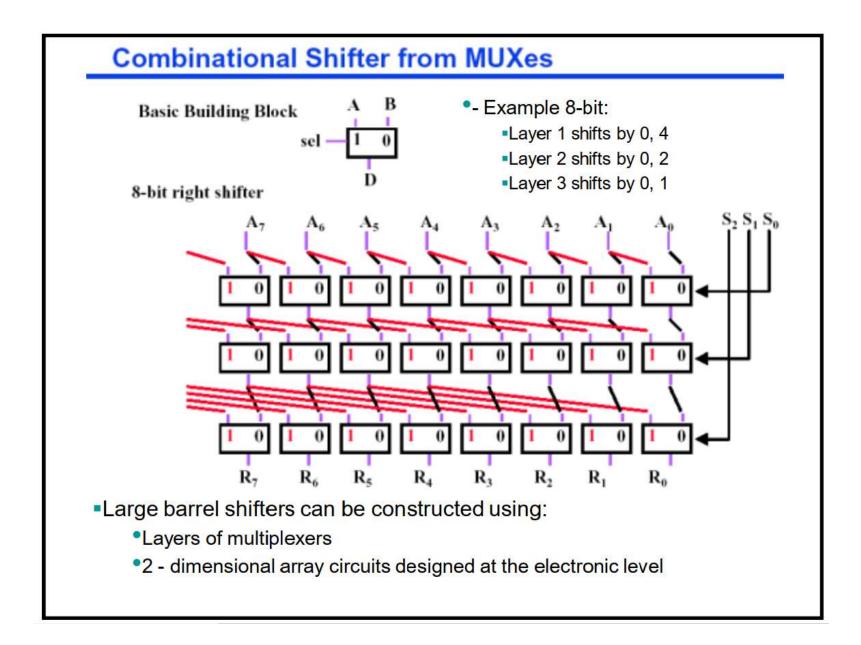

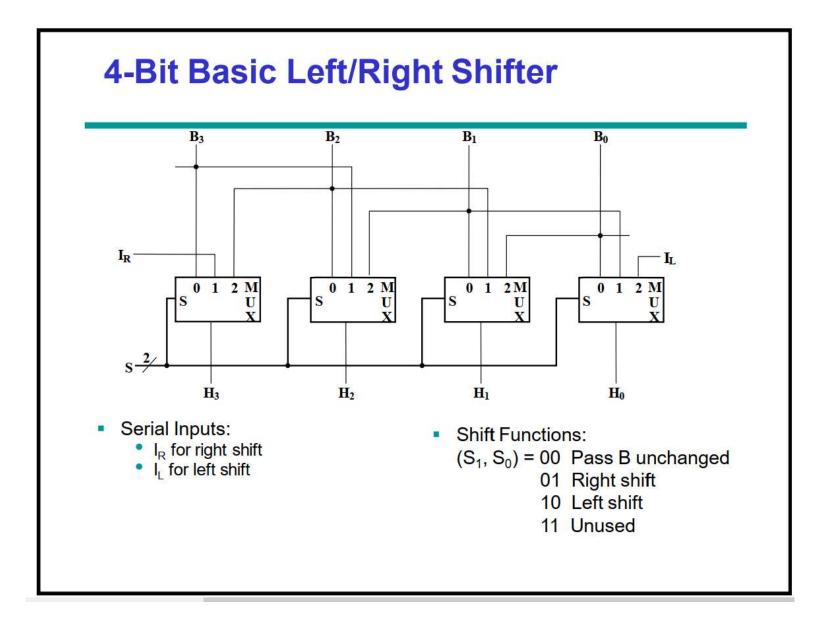

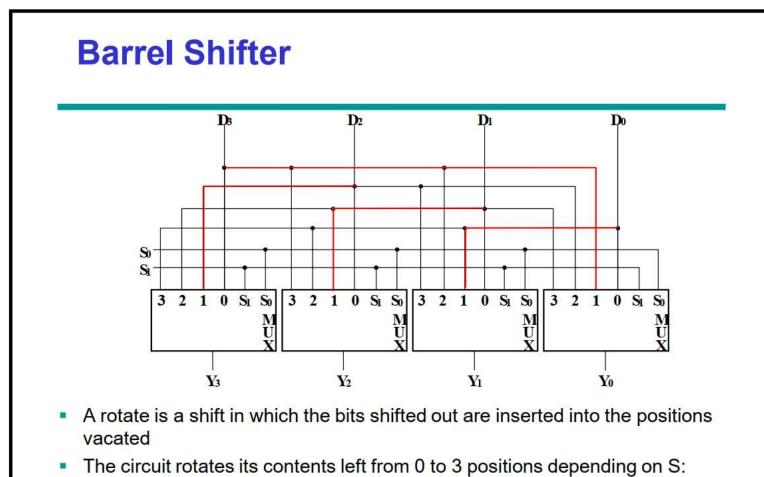

#### **Shift Microoperations**

Let R2 = 11001001

| Symbolic<br>Designation | Description | R1 content |  |

|-------------------------|-------------|------------|--|

| R1 ← sl R2              | Shift Left  | 10010010   |  |

| R1 ← sr R2              | Shift Right | 01100100   |  |

- Note: These shifts "zero fill". Sometimes a separate flip-flop is used to provide the data shifted in, or to "catch" the data shifted out.

- Other shifts are possible (rotates, arithmetic)

University Of Diyala College Of Engineering Computer Engineering Department

1

# Digital System Design II

Dr. Yasir Al-Zubaidi

**Third stage**

2019

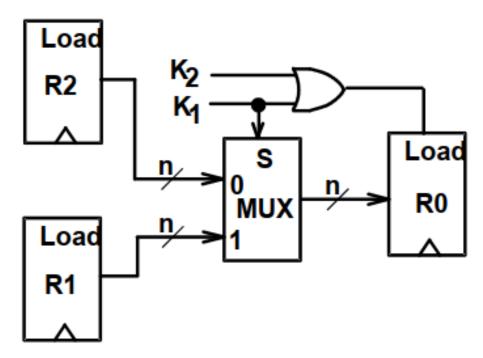

# Multiplexer-Based Single Register Transfers

- MUX connected to register outputs produce flexible transfer structures

- Transfers: K1:  $\underline{R0} \leftarrow R1$ K2 K1: R0  $\leftarrow R2$

Assume: a register consists of identical cells

- Register design can be approached as follows:

- Design a representative cell for the register

- Make copies of the cell and connect together to form the register

- Applying appropriate "boundary conditions" to cells that need to be different and contract if appropriate

- <u>Register cell design</u> is the first step of the above process

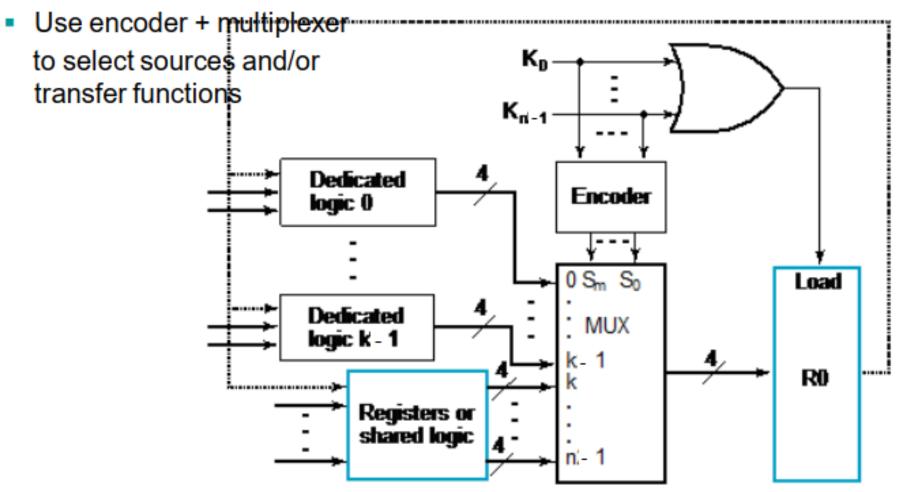

# **Approach I: Multiplexer-based**

- An n-input multiplexer with a variety of sources and functions

- Load enable by OR of control signals K<sub>0</sub>, K<sub>1</sub>, ... K<sub>n-1</sub> (for 00...0, no load)

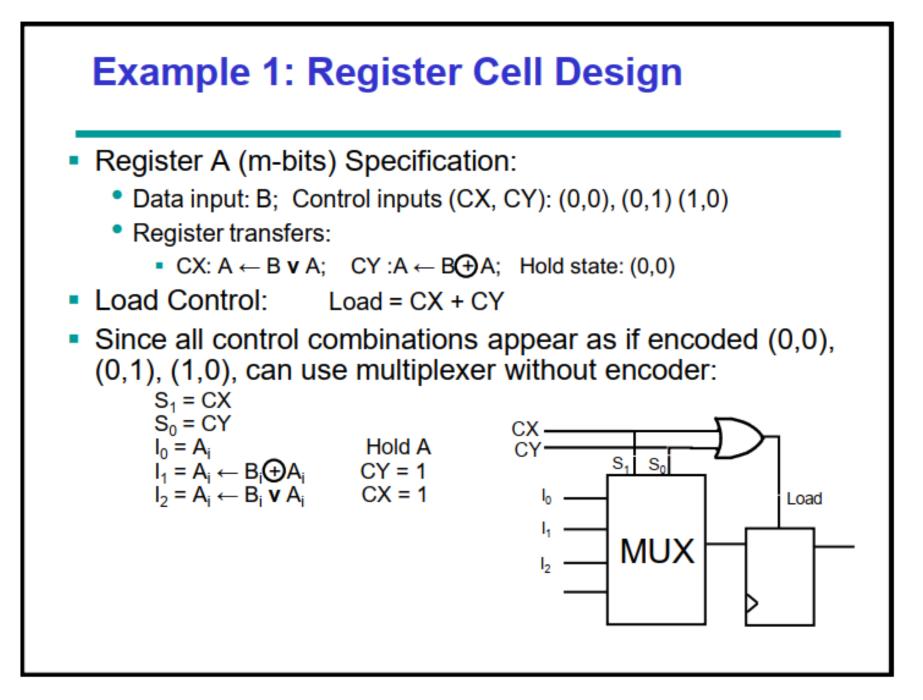

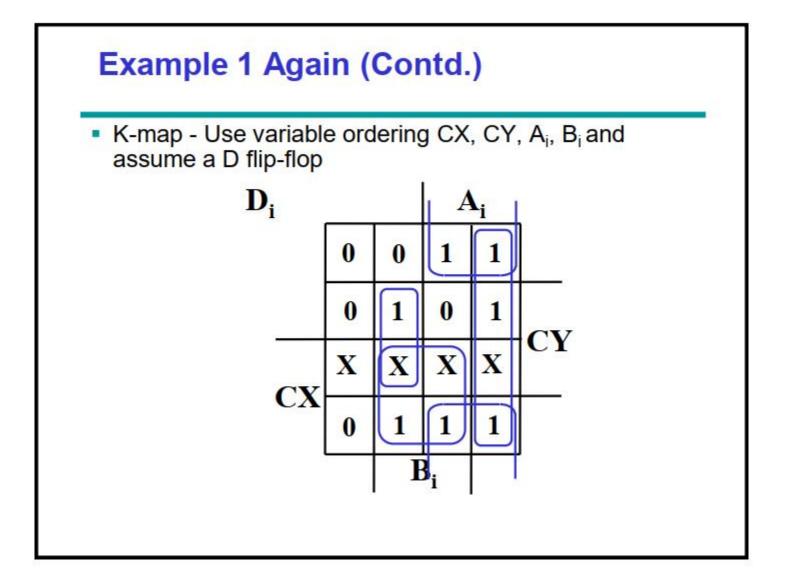

# Example 1 Again

#### State Table for D<sub>i</sub>:

|                | Hold   | Ai <b>v</b> Bi     |                    | Ai⊕Bi              |                    |

|----------------|--------|--------------------|--------------------|--------------------|--------------------|

|                | CX = 0 | CX = 1             | CX = 1             | CX = 0             | CX = 0             |

| A <sub>i</sub> | CY = 0 | CY = 0             | CY = 0             | CY = 1             | CY = 1             |

|                |        | B <sub>i</sub> = 0 | B <sub>i</sub> = 1 | B <sub>i</sub> = 0 | B <sub>i</sub> = 1 |

| 0              | 0      | 0                  | 1                  | 0                  | 1                  |

| 1              | 1      | 1                  | 1                  | 1                  | 0                  |

- Four variables (CX, CY, A, B) should give a total of 16 state table entries

- By using:

- Combinations of variable names and values

- Don't care conditions (for CX = CY = 1)

only 12 entries are required to represent the 16 entries

# Example 1 Again (Contd.)

The resulting SOP equation: D<sub>i</sub> = CX B<sub>i</sub> + CY Ā<sub>i</sub> B<sub>i</sub> + A<sub>i</sub> B

i + CY A<sub>i</sub>

= CX B<sub>i</sub> + Ā<sub>i</sub> (CY B<sub>i</sub>) + A<sub>i</sub>(CY B<sub>i</sub>)

= CX B<sub>i</sub> + A<sub>i</sub> ⊕ (CY B<sub>i</sub>)

The gate input cost per cell = 13

The gate input cost per cell for the previous version is:

Per cell: 19 Shared decoder logic: 8

- Cost gain by sequential design > 6 per cell

- Also, no Enable on the flip-flop makes it cost less

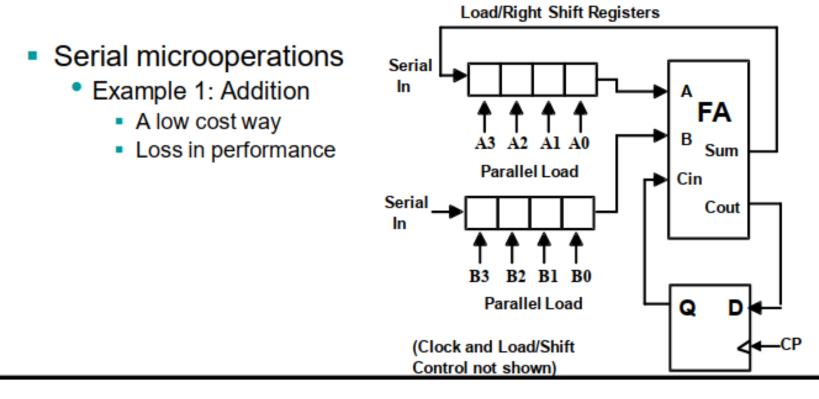

#### **Serial Transfers and Microoperations**

#### Serial Transfers

- Used for "narrow" transfer paths

- Example 1: Telephone or cable line

- <u>Parallel-to-Serial</u> conversion at source

- Serial-to-Parallel conversion at destination

#### **Overview**

- Datapath and control

- Microoperations

- Sequencing and control

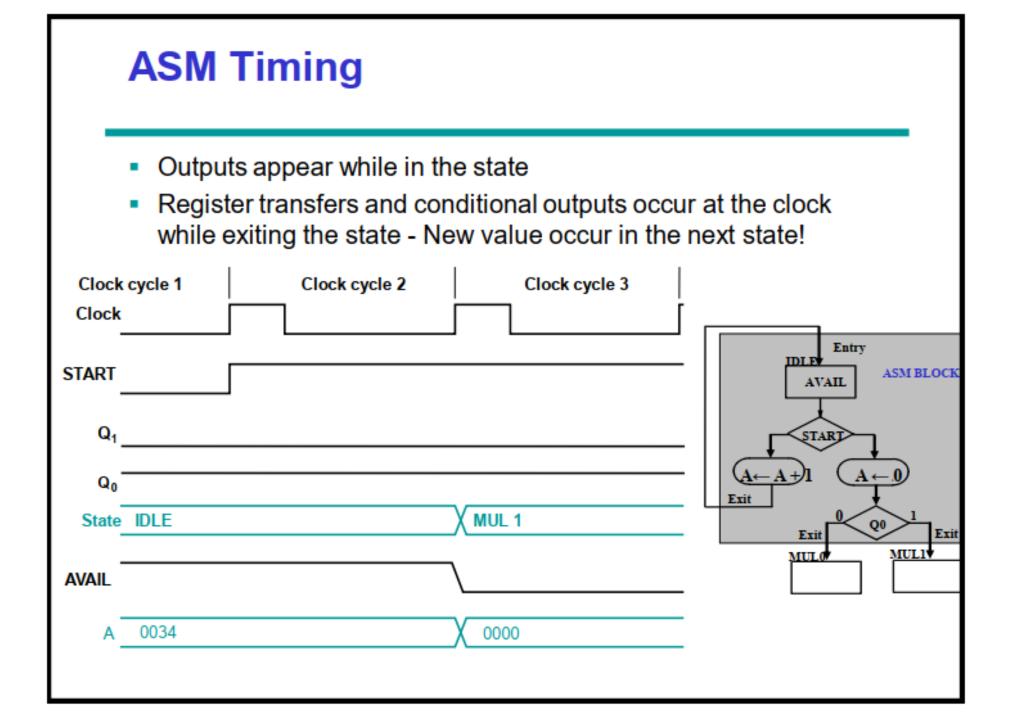

- Algorithmic State Machines (ASM)

- ASM chart

- Timing considerations

- ASM chart examples: Binary multiplier

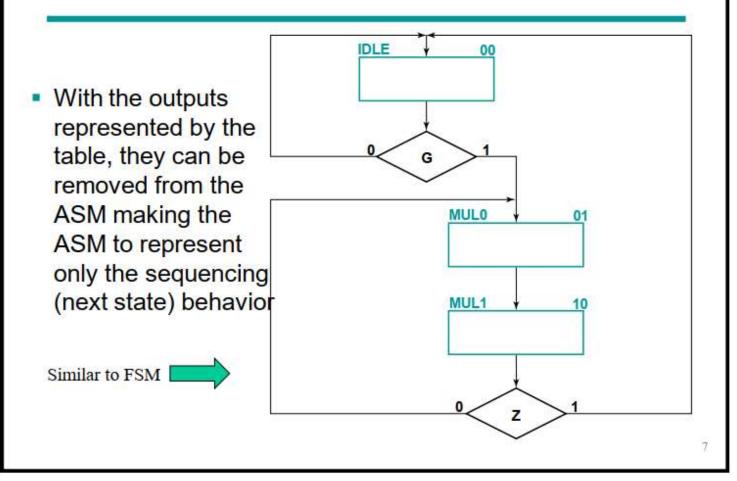

- Hardwired Control

- Control design methods

- Sequence register and decoder

- One flip-flop per state

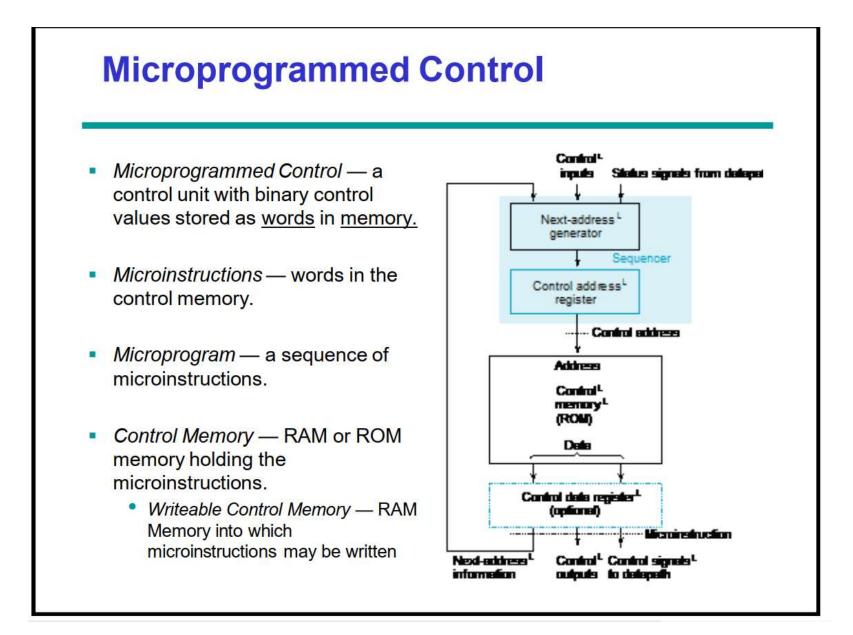

- Microprogrammed control

#### **Control Unit Types**

- Two distinct classes:

- Programmable

- Non-programmable.

- A programmable control unit:

- An external memory array for storing instructions and control information

- A program counter (PC) register points to the next instruction to be executed

- Decision logic for determining the sequence of operations and logic to interpret the instructions

- A non-programmable control unit: does not fetch instructions from a memory and is not responsible for sequencing instructions

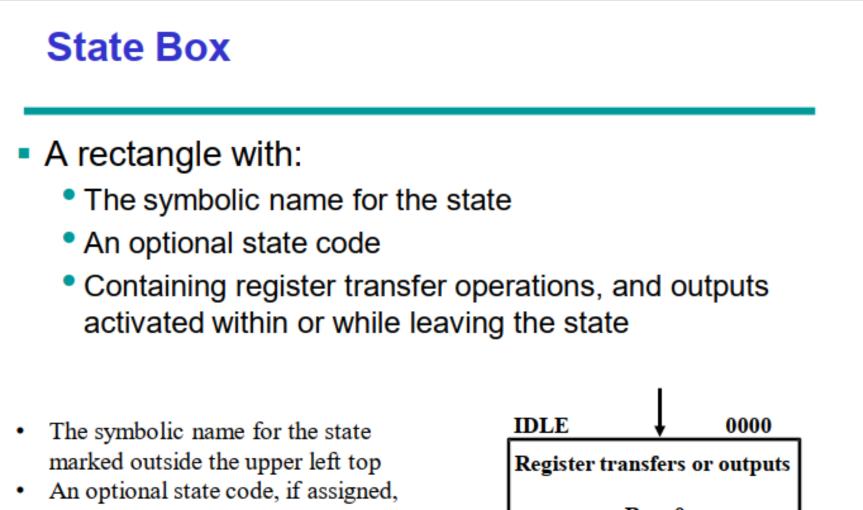

#### **Algorithmic State Machines**

- The function of a sequential circuit can be represented by a state table or a state diagram.

- An Algorithmic State Machine (ASM) is a flowchartlike way to specify state diagrams for sequential logic and, optionally, <u>actions performed in a datapath</u>.

- A flowchart is a way of showing <u>actions</u> and <u>control flow</u> in an algorithm.

- An ASM explicitly specifies a <u>sequence of actions</u> and their <u>timing</u> relationships

- An ASM chart directly leads to a hardware realization

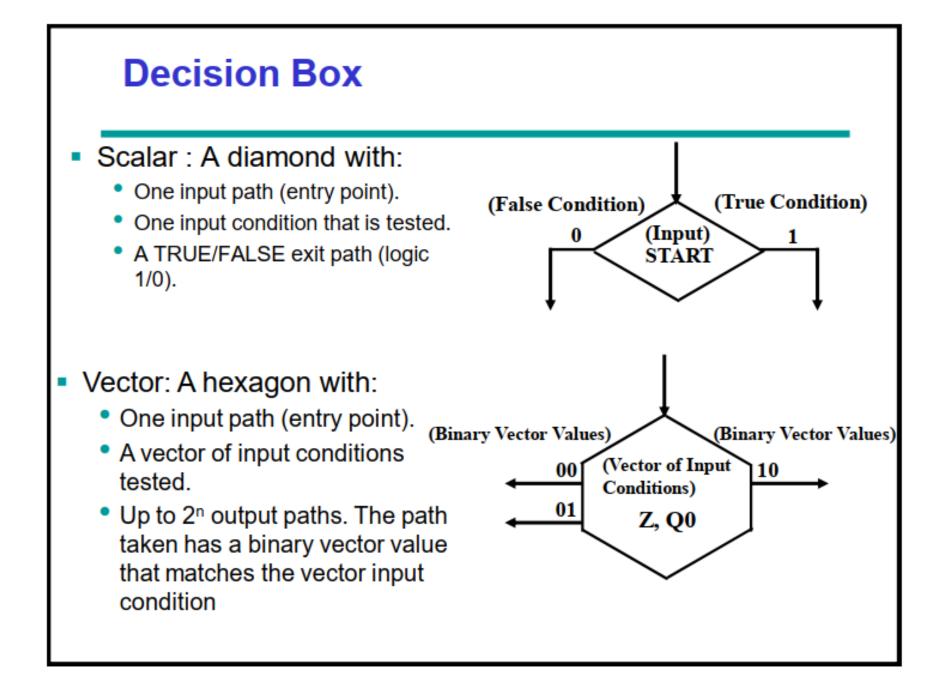

- Primitives:

- 1. State Box (a rectangle)

- 2. Decision Box

- I. Scalar (a diamond)

- II. Vector (a hexagon)

- 3. Conditional Output Box (an oval)

outside the upper right top

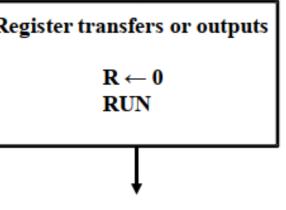

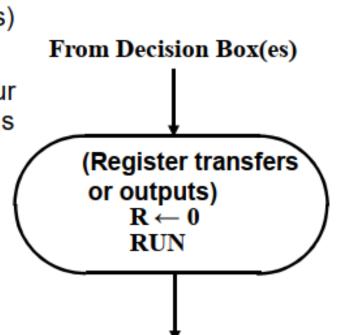

# **Conditional Output Box**

- An oval with:

- One input path from a decision box(es)

- One output path

- Register transfers or outputs that occur only if the conditional path to the box is taken.

- Transfers and outputs

- in a state box are <u>Moore type</u> dependent only on state

- in a conditional output box are <u>Mealy</u> <u>type</u> - dependent on both state and inputs

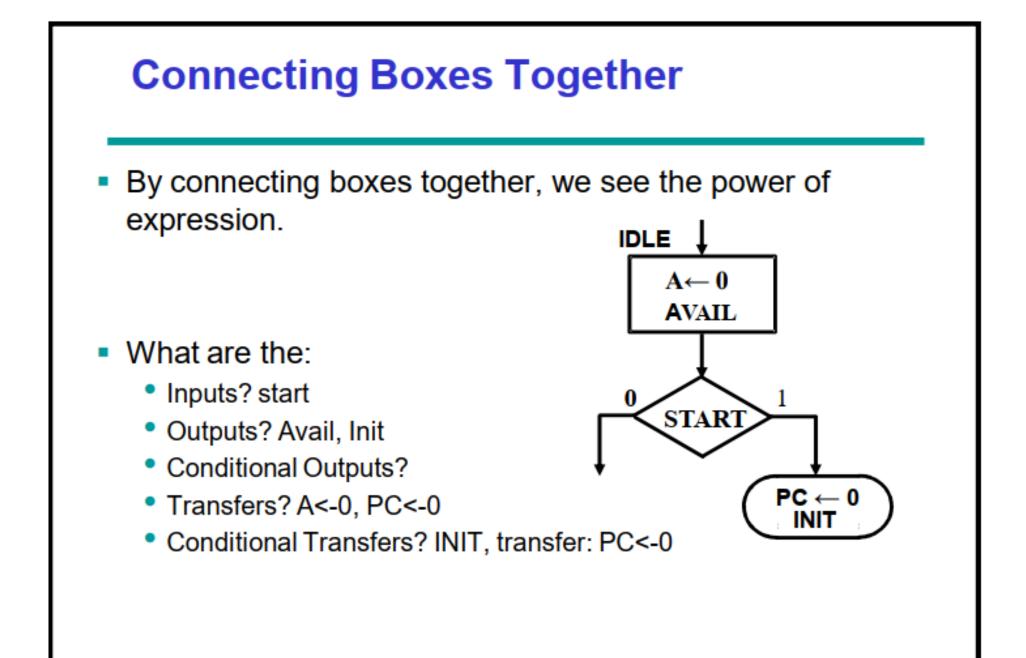

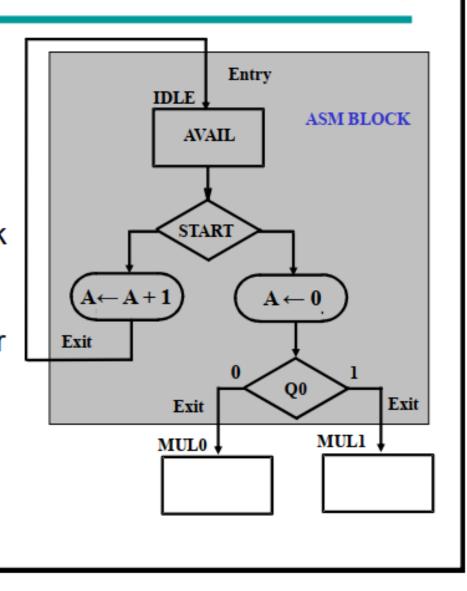

#### **ASM Blocks**

One state box along with all decision and conditional output boxes connected to it, called an ASM Block. i.e., the ASM Block includes all items on the path from the current state to the same or other states.

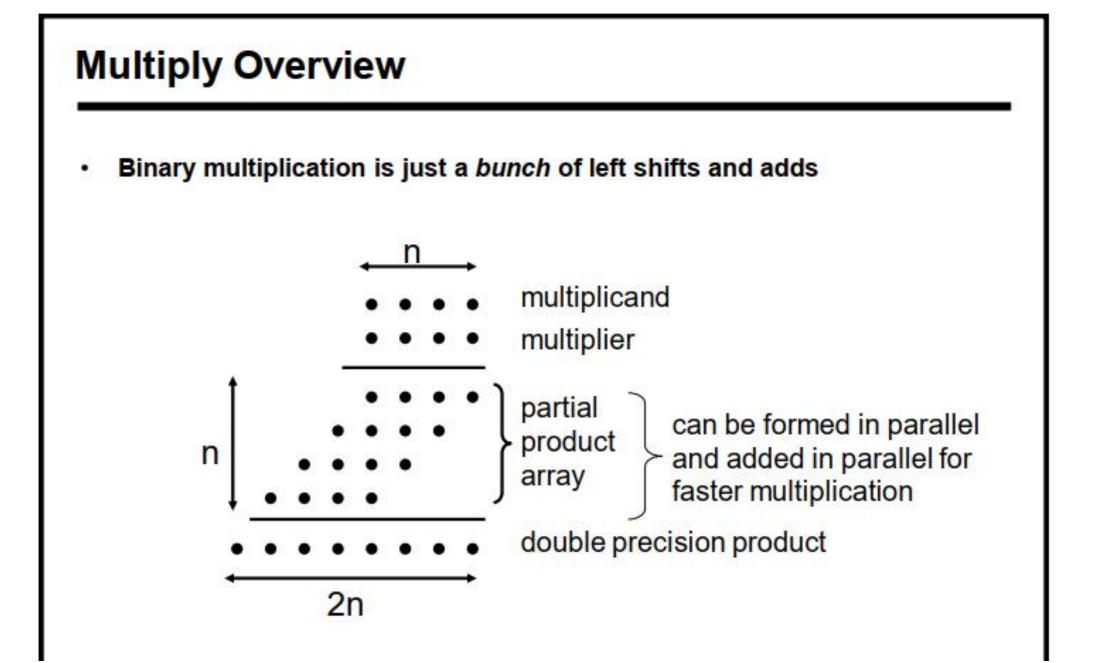

# **Multiplier Example**

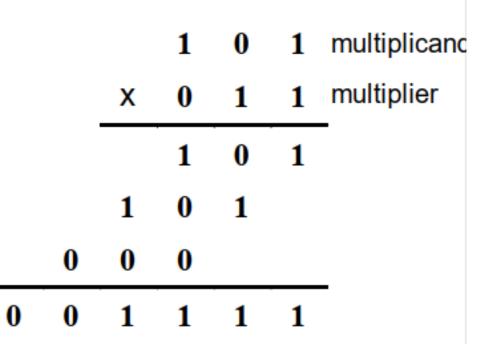

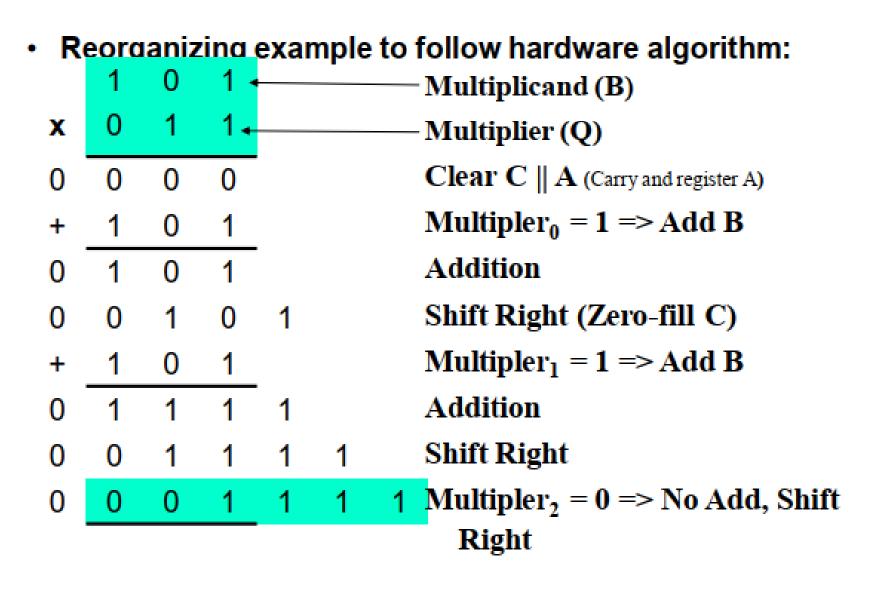

- Example: (101 x 011) Base 2

- Partial products are: 101 x 0, 101 x 1, and 101 x 1

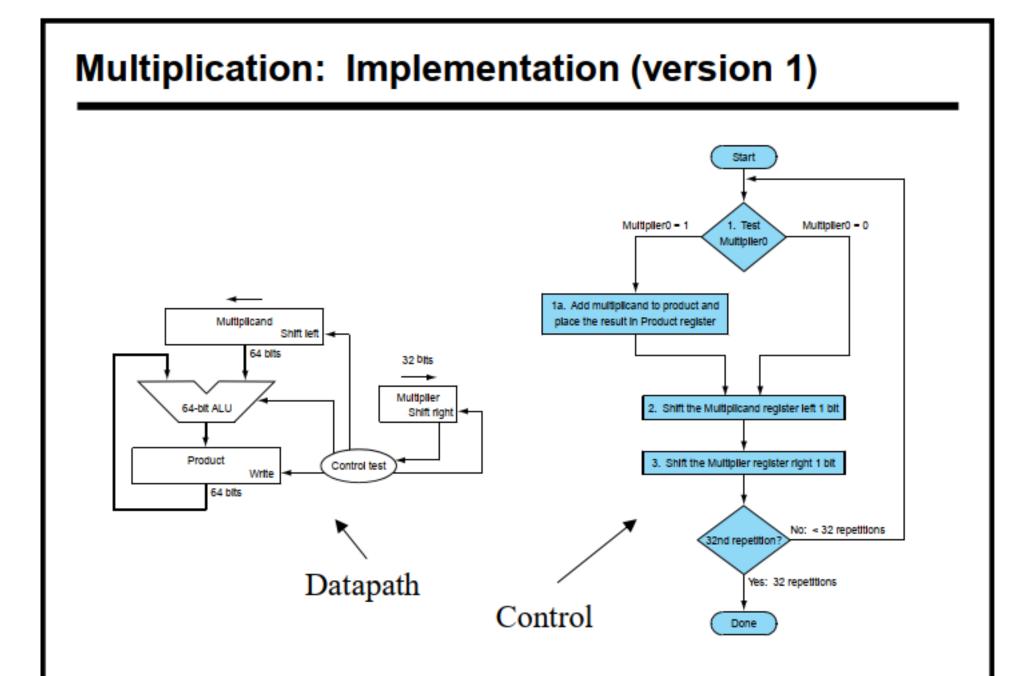

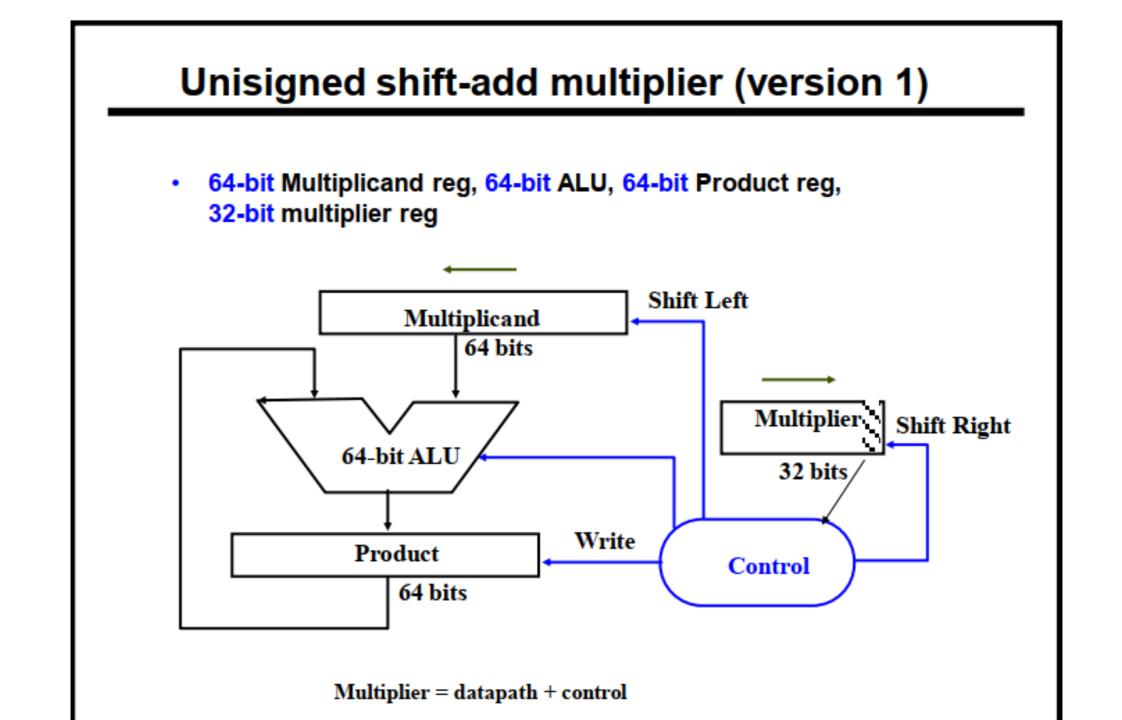

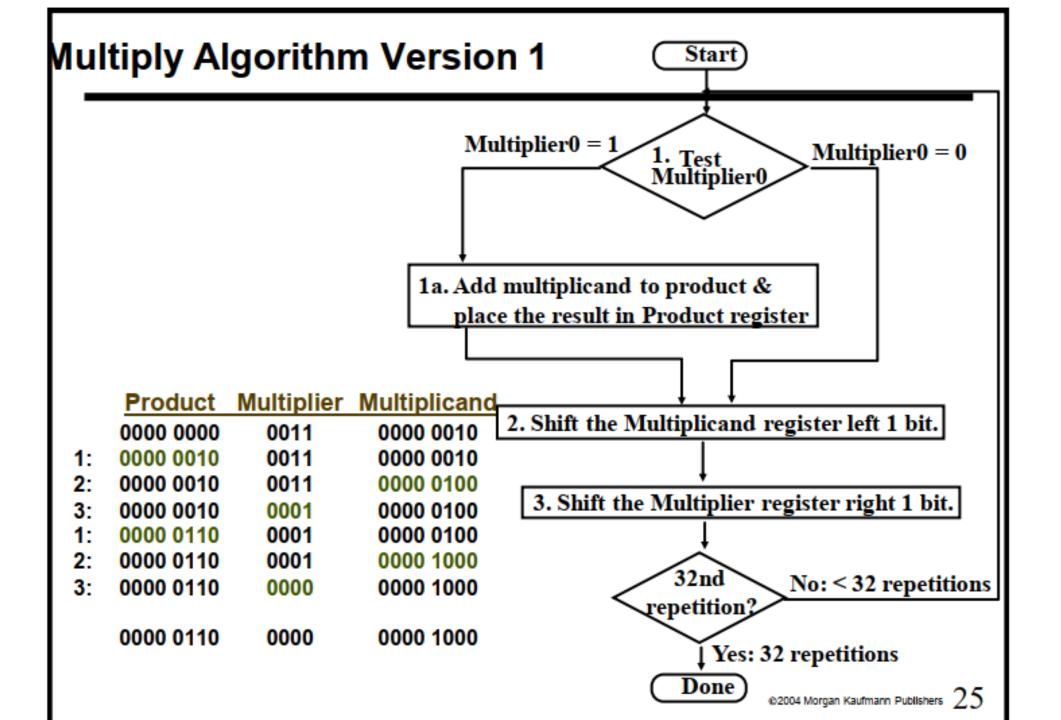

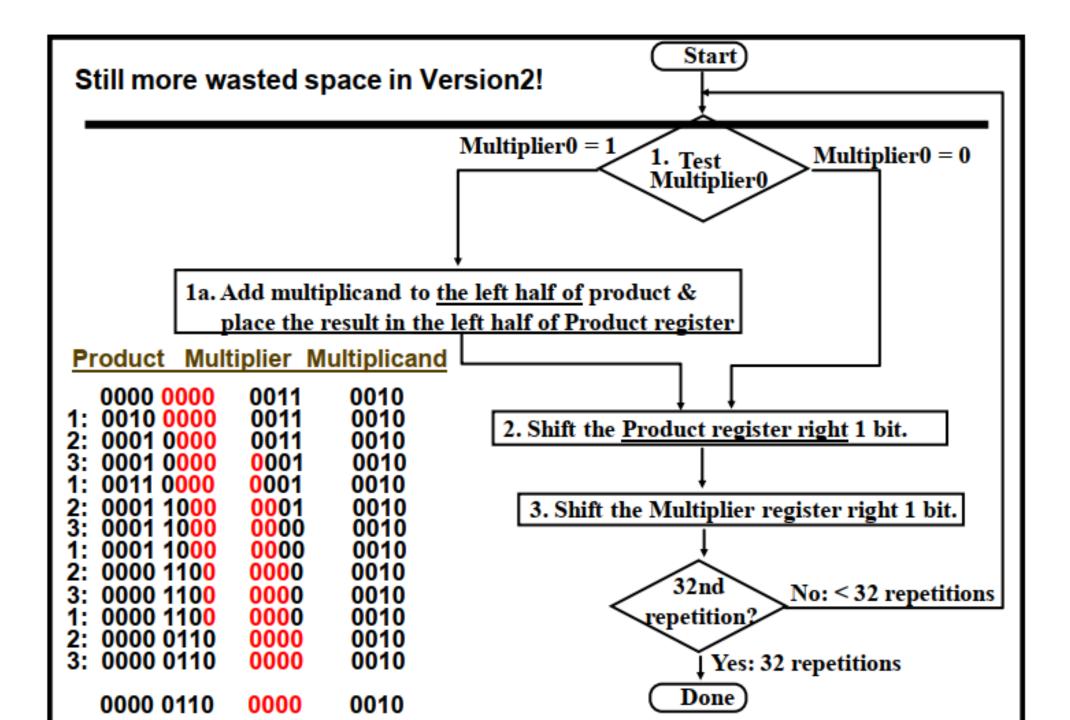

#### **Observations on Multiply Version 1**

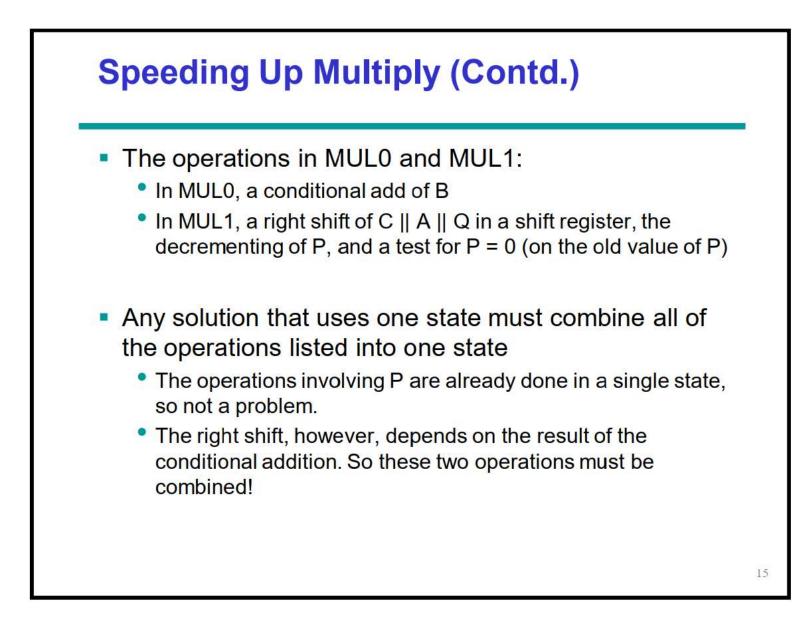

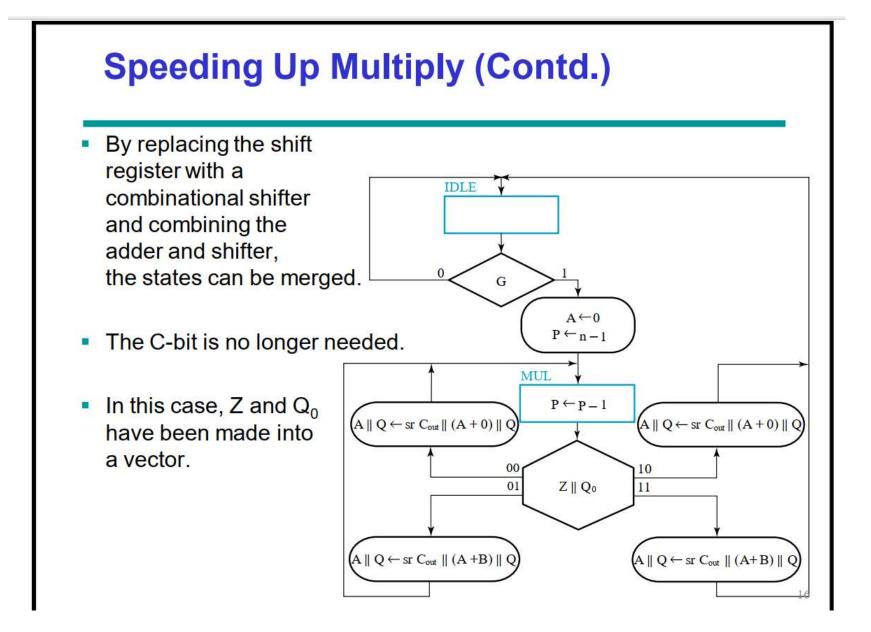

- 1 clock per cycle => ≈ 100 clocks per multiply because of 32 repetitions, 3 steps in one repetition

- Ratio of add/sub to multiply is from 5:1 to 100:1

- Slow

- 0's inserted in the rightmost bit of multiplicand as shifting left

- => least significant bits of product never changed once formed

- 1/2 bits in multiplicand always 0

- MSB are 0s at the beginning

- 0 is inserted in LSB as multiplicand shifting left

- => 64-bit multiplicand register is wasted

- => 64-bit adder is wasted

- Instead of shifting multiplicand to left, let's <u>shift</u>

product to right

(2004 Morgan Kaufmann Publishers

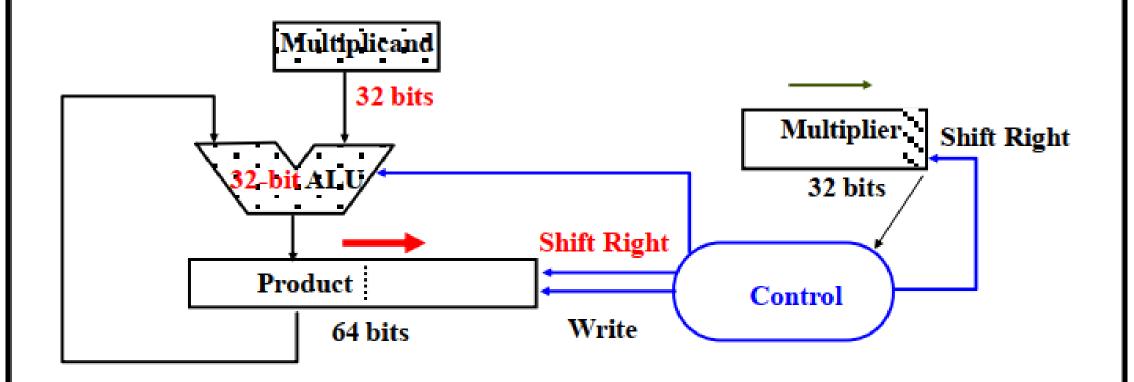

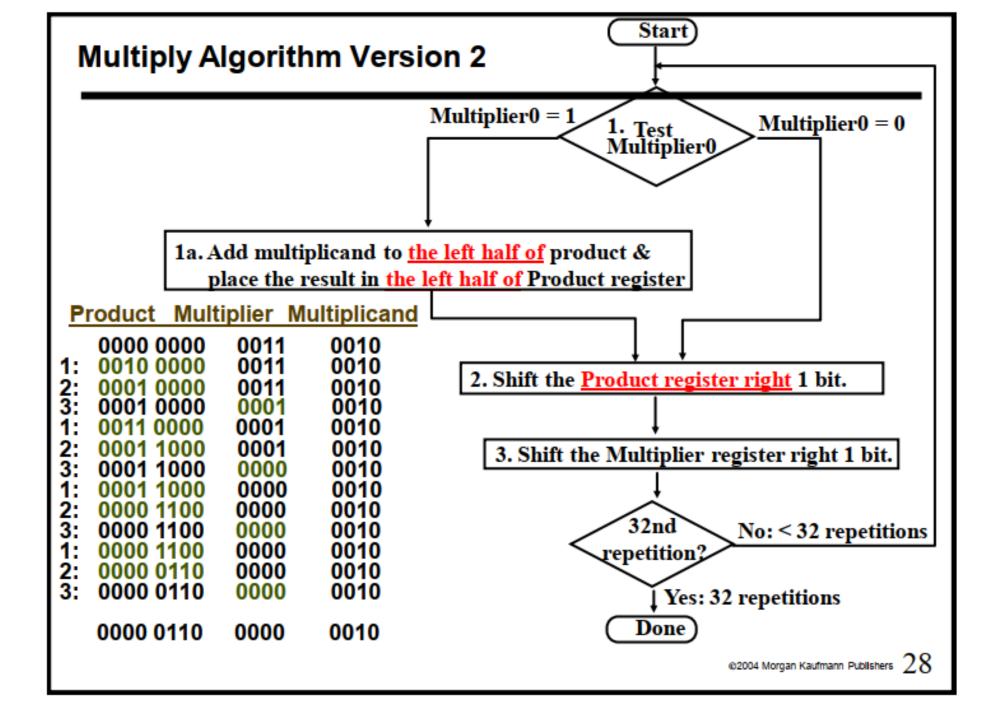

## MULTIPLY HARDWARE Version 2

<u>32</u>-bit Multiplicand reg, <u>32</u>-bit ALU, 64-bit Product reg, 32-bit Multiplier reg

### **Observations on Multiply Version 2**

Product register wastes space that exactly matches size of multiplier

=> combine Multiplier register and Product register

## Example (1 0 1) × (0 1 1) Again

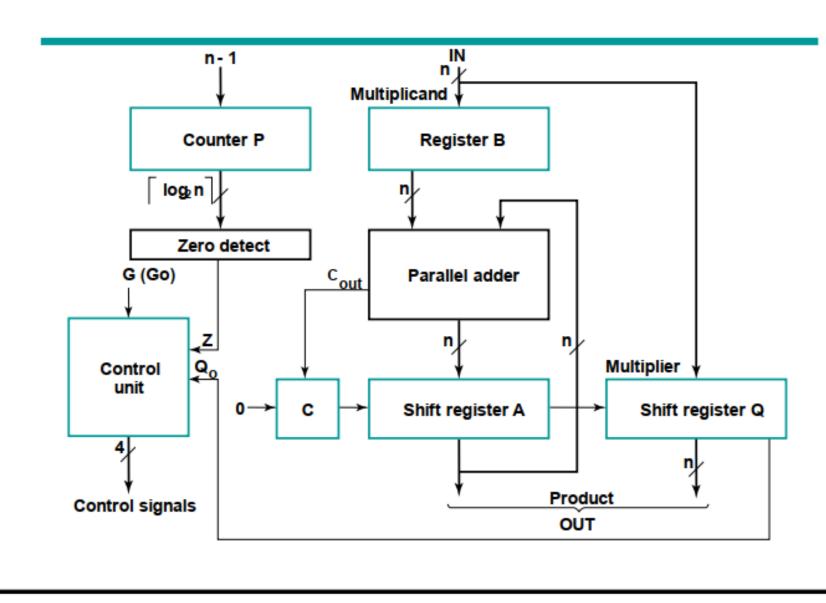

### Multiplier Example: Block Diagram

- 1. The multiplicand is loaded into register B.

- 2. The multiplier is loaded into register Q.

- 3. When G becomes 1, register C|| A is initialized to 0.

- Down Counter P is initialized to n 1 (n = number of bits in multiplier)

- 5. The partial products are formed in register C||A||Q.

- 6. Each multiplier (Q) bit, beginning with the LSB, is processed (if bit is 1, B is added to partial product of A; if bit is 0, do nothing)

- 7. C||A||Q is shifted right using the shift register

- Partial product bits fill vacant locations in Q as multiplier is shifted out

- If overflow during addition, the outgoing carry is recovered from C during the right shift

- 8. Steps 6 and 7 are repeated until P = 0 as detected by Zero detect.

University Of Diyala College Of Engineering Department of Computer Engineering

1

# Digital System Design II ASM Based Datapath and Control Design

Dr. Yasir Al-Zubaidi Third stage 2021

#### Overview

- Datapath and control

- Microoperations

- Sequencing and control

- Algorithmic State Machines (ASM)

- ASM chart

- Timing considerations

- ASM chart examples: Binary multiplier

- Hardwired Control

- Control design methods

- Sequence register and decoder

- One flip-flop per state

- Microprogrammed control

# Multiplier Example: Control Signal Table

| Block Diagram<br>Module | Microope ration                                                                    | Control<br>Sign al N ame | Control<br>Expression      |

|-------------------------|------------------------------------------------------------------------------------|--------------------------|----------------------------|

| Register A:             | <i>A</i> ←0                                                                        | Initialize               | IDLE · G                   |

| _                       | $A \leftarrow A + B$                                                               | Load                     | MULO · Qo                  |

|                         | $C \parallel A \parallel Q \leftarrow \mathrm{sr} \ C \parallel A \parallel Q$     | Shift_dec                | MUL1                       |

| Register B:             | $B \leftarrow IN$                                                                  | Load_B                   | LOADB                      |

| Flip-Flop C:            | <b>C</b> ← <b>0</b>                                                                | Clear_C                  | $IDLE \cdot G + MUL1$      |

|                         | $C \leftarrow C_{\text{out}}$                                                      | Load                     | —                          |

| Register Q:             | $\mathbf{Q} \leftarrow \mathbf{IN}$                                                | Load_Q                   | LOADQ                      |

|                         | $C \parallel A \parallel Q \leftarrow \operatorname{sr} C \parallel A \parallel Q$ | Shift_dec                | 1989)<br>1 <u>988</u><br>1 |

| Counter P:              | $P \leftarrow n-1$                                                                 | Initialize               | -                          |

|                         | $P \leftarrow P - 1$                                                               | Shift_dec                | —                          |

- Signals are defined on a register basis

- LOADQ and LOADB: external signals controlled from the system using the multiplier and will not be considered a part of this design

- Many control signals are "reused" for different registers.

- These 4 control signals are the "outputs" of the control unit: initialize, load, shift\_dec, clear\_c

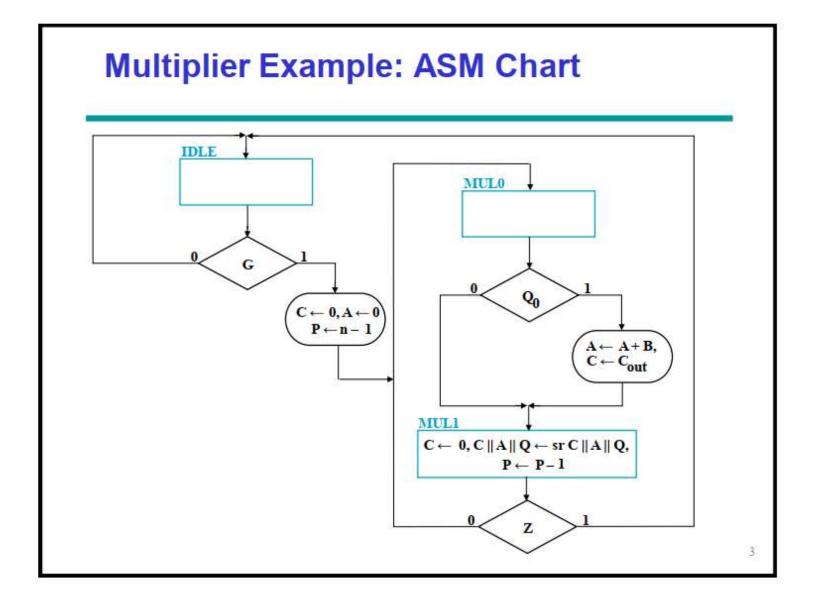

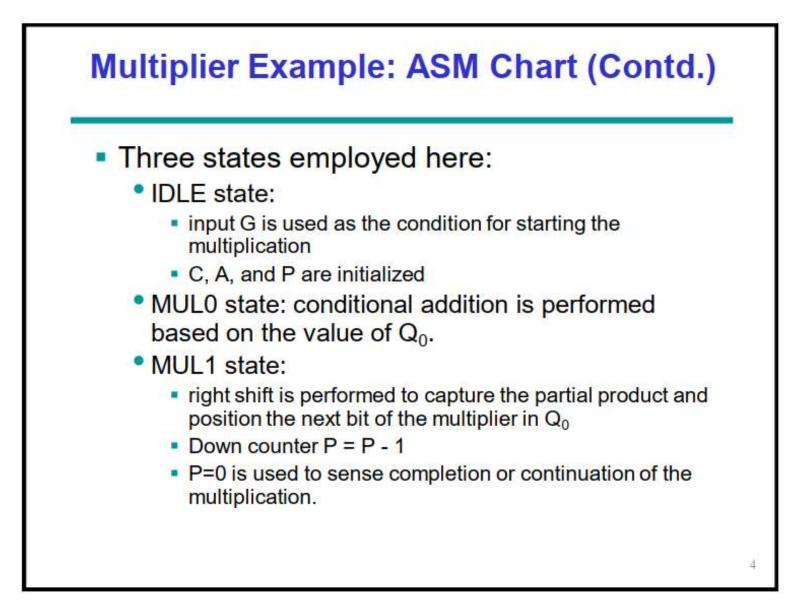

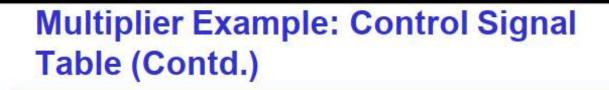

# Multiplier Example - Sequencing Part of ASM

#### Multiplier Example: Sequencer and Decoder Design - Specification

- Initially, use sequential circuit design techniques

- First, define:

- States: IDLE, MUL0, MUL1

- Input Signals: G, Z, Q<sub>0</sub> (Q<sub>0</sub> affects outputs, not next state)

- Output Signals: Initialize, LOAD, Shift\_Dec, Clear\_C

- State Transition Diagram (Use Sequencing ASM)

- Output Function: Use Control Signal Table

- Second, find

- State Assignments

- Use two state bits to encode the three states IDLE, MUL0, and MUL1.

| State  | M1 | MO |

|--------|----|----|

| IDLE   | 0  | 0  |

| MUL0   | 0  | 1  |

| MUL1   | 1  | 0  |

| Unused | 1  | 1  |

#### Multiplier Example: Sequencer and Decoder Design - Formulation

Assuming that state variables M1 and M0 are decoded into states, the next state part of the state table is:

| Current State | Input<br>G Z | Next State<br>M1 M0 | Current State<br>M1 M0 | Input<br>G Z | Next State<br>M1 M0 |

|---------------|--------------|---------------------|------------------------|--------------|---------------------|

| IDLE          | 0 0          | 0 0                 | MUL1                   | 0 0          | 0 1                 |

| IDLE          | 0 1          | 0 0                 | MUL1                   | 0 1          | 0 0                 |

| IDLE          | 1 0          | 0 1                 | MUL1                   | 1 0          | 0 1                 |

| IDLE          | 1 1          | 0 1                 | MUL1                   | 1 1          | 0 0                 |

| MUL0          | 0 0          | 1 0                 | Unused                 | 0 0          | d d                 |

| MUL0          | 0 1          | 1 0                 | Unused                 | 0 1          | d d                 |

| MUL0          | 1 0          | 1 0                 | Unused                 | 1 0          | d d                 |

| MUL0          | 1 1          | 1 0                 | Unused                 | 1 1          | d d                 |

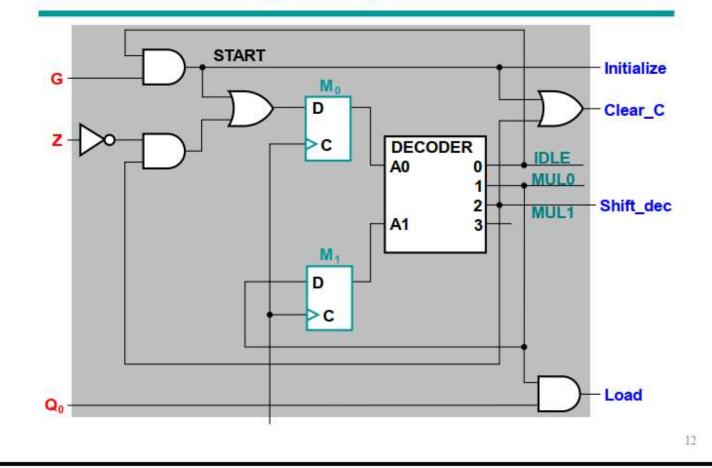

#### Multiplier Example: Sequencer and Decoder Design – Equations Derivation/Optimization

```

Finding the equations for M1 and M0 using decoded states:

M1 = MULO

M0 = IDLE \cdot G + MUL1 \cdot \overline{7}

The output equations using the decoded states:

Initialize = IDLE \cdot G

Load = MUL0 \cdot Q_0

Clear C = IDLE · G + MUL1

Shift dec = MUL1

Doing multiple level optimization, extract IDLE · G:

START = IDLE \cdot G

M1 = MUL0

M0 = START + MUL1 \cdot \overline{Z}

Initialize = START

Load = MUL0 \cdot Q_0

Clear C = START + MUL1

Shift dec = MUL1

The resulting circuit using flip-flops, a decoder, and the above

equations is given on the next slide.

```

#### Multiplier Example: Sequencer and Decoder Design - Implementation

| Binary multiplier with n=4                               | No. AL MARINESS IN THE REPORTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| library ieee;                                            | datapath_func : process (CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| use ieee.std_logic_unsigned.all;                         | variable CA: std_logic_vector (4 downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| entity binary multiplier is                              | begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| port(CLK, RESET, G, LOADB, LOADQ: in std_logic;          | if (CLK'event and CLK='1') then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MULT_IN : in std_logic_vector (3 downto 0);              | if LOADB='1' then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MULT_OUT : out std_logic_vector (7 downto 0));           | $B \le MULT IN:$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| end bianry_multiplier;                                   | The state of the s |

|                                                          | end if;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| architecture behavior_4 of binary_multiplier is          | if $LOADQ = '1'$ then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| type state_type is (IDLE, MUL0, MUL1);<br>variable P:=3; | $Q \leq MULT_IN;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| signal state, next_state : state_type;                   | end if;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| signal A, B, Q:std_logic_vector(3 downto 0);             | case state is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| signal C, Z:std_logic;                                   | when IDLE =>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| begin y g y                                              | if G = '1' then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $Z \le P(1) \text{ NOR } P(0);$                          | C <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $MULT_OUT \le A \& Q;$                                   | A <= "0000";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (CIV PECET)                                              | P <= "11":                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| state_register : process (CLK, RESET)<br>begin           | end if;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| if (RESET = '1') then                                    | when MUL0 =>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| state <= IDLE;                                           | if $Q(0) = 1$ then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| elsif (CLK'event and CLK='1') then                       | CA := ('0' & A) + ('0' & B);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <pre>state &lt;= next_state;</pre>                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| endif;                                                   | else                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| end process;                                             | CA := C & A;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          | end if;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| next_state_func : process (G, Z, state)                  | C <= CA(4);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| begin<br>case state is                                   | A <= CA(3 downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| when IDLE =>                                             | when MUL1 =>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |